Fターム[5F110BB20]の内容

Fターム[5F110BB20]に分類される特許

121 - 140 / 665

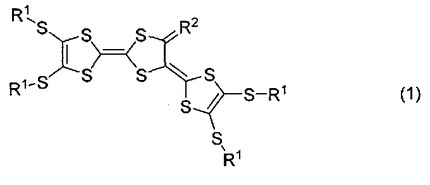

有機半導体薄膜形成材料、該材料から形成される有機半導体薄膜および該有機半導体薄膜を有する有機半導体素子

【課題】本発明は、有機溶媒に対する溶解性に優れるジチオラン化合物を含む有機半導体薄膜形成材料を提供することを課題の一つとし、該材料から形成される、キャリア移動度が高い有機半導体薄膜、および該有機半導体薄膜を有する有機半導体素子または該有機半導体薄膜を有するトランジスタを提供することを課題の一つとする。

【解決手段】本発明の有機半導体薄膜形成用材料は、下記式(1)で示されるジチオラン化合物を含む。 (もっと読む)

(もっと読む)

半導体装置

【課題】消費電力の抑制された半導体装置を提供する。

【解決手段】第1のトランジスタと、第2のトランジスタと、第1のインバータ回路と、第2のインバータ回路とを有し、前記第1のトランジスタのゲートに、反転クロック信号が入力され、前記第2のトランジスタのゲートに、クロック信号が入力され、前記第1のトランジスタのソースまたはドレインの一方に、第1の配線が電気的に接続され、前記第1のトランジスタのソースまたはドレインの他方に、前記第1のインバータ回路の入力が電気的に接続され、前記第1のインバータ回路の出力に、前記第2のトランジスタのソースまたはドレインの一方が電気的に接続され、前記第2のトランジスタのソースまたはドレインの他方に、前記第2のインバータ回路の入力が電気的に接続され、前記第2のインバータ回路の出力に、第2の配線が電気的に接続されている。

(もっと読む)

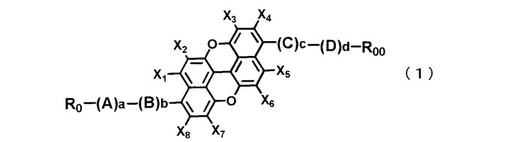

有機トランジスタ

【課題】高い移動度、大きな電流オン/オフ比を有し、保存安定性に優れた有機トランジスタを提供する。

【解決手段】有機半導体層を有する有機トランジスタにおいて、該有機半導体層に一般式(1)で表される化合物を少なくとも1種含有してなる有機トランジスタ。

〔X1〜X8は、水素原子、ハロゲン原子、アルキル基、アルコキシ基、アルコキシアルキル基、アルコキシアルコキシ基、アリール基を表し、R0およびR00は、水素原子、ハロゲン原子、アルキル基、アルコキシ基、アルコキシアルキル基、アルコキシアルコキシ基を表し、A、B、CおよびDは、フェニレン基、チエニレン基、チエノチエニレン基、ナフチレン基、アントリレン基を表し、a、b、cおよびdはそれぞれ独立に0、1または2を表す〕

(もっと読む)

不揮発性のラッチ回路及び論理回路並びにそれを用いた半導体装置

【課題】新規な不揮発性のラッチ回路及びそれを用いた半導体装置を提供する。

【解決手段】第1の素子の出力が第2の素子の入力に電気的に接続され、第2の素子の出力が第1の素子の入力に電気的に接続されるループ構造を有するラッチ部と、ラッチ部のデータを保持するデータ保持部とを有し、このラッチ部とデータ保持部とにより不揮発性のラッチ回路が構成される。データ保持部は、チャネル形成領域を構成する半導体材料として酸化物半導体を用いたトランジスタをスイッチング素子として用いている。またこのトランジスタのソース電極又はドレイン電極に電気的に接続された容量を有している。

(もっと読む)

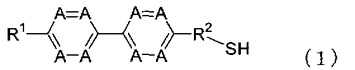

金属電極および該金属電極を有する有機半導体素子

【課題】本発明は、有機高分子等の半導体薄膜形成材料が単結晶でなく、多結晶であっても、印刷方法により金属電極上に安定で良好な有機半導体薄膜を簡便に形成することができ、性能の優れた有機半導体素子を提供することを課題とする。

【解決手段】本発明の金属電極は、下記式(1)で表される化合物を含有する溶液を用いて形成された表面処理層を有することを特徴とする。 (もっと読む)

(もっと読む)

半導体素子、半導体装置及びそれらの作製方法

【課題】チャネル長Lが短く微細化が可能な、酸化物半導体を用いたトップゲート型の半導体素子を提供することを課題とする。また、該半導体素子の作製方法を提供することを課題とする。

【解決手段】絶縁表面上に酸化物半導体層と、酸化物半導体層上にソース電極層及びドレイン電極層と、酸化物半導体層、前記ソース電極層、及び前記ドレイン電極層上にゲート絶縁層と、ゲート絶縁層上にゲート電極層とを有し、ソース電極層及びドレイン電極層は側壁を有し、側壁は前記酸化物半導体層の上面と接する半導体素子である。

(もっと読む)

半導体装置、高周波集積回路、高周波無線通信システムおよび半導体装置の製造方法

【課題】SOS基板の異方性を低減して半導体装置のデバイス特性の面内均一性を向上する。

【解決手段】絶縁体基板101の主面上にSi層(またはSi基板)100を有する半導体装置10において、絶縁体基板101はサファイア基板101であり、絶縁体基板101の主面はc面である。サファイア基板101において異方性の少ないc面にSi層100を形成するので、Si層100上に形成された半導体装置10のデバイス特性の面内均一性を向上することができる。

(もっと読む)

半導体装置

【課題】無線通信機能を有する半導体装置を低消費電力化又は長寿命化すること。

【解決手段】当該半導体装置は、電力供給源となる電池と、特定の回路とがチャネル形成領域が酸化物半導体によって構成されるトランジスタを介して電気的に接続することによって解決することができる。当該酸化物半導体の水素濃度は、5×1019(atoms/cm3)以下である。そのため、当該トランジスタのリーク電流を低減することができる。その結果、当該半導体装置の待機時の消費電力を低減することができる。また、これにより当該半導体装置を長寿命化することができる。

(もっと読む)

半導体装置及びその作製方法

【課題】安定した電気特性を持つ、酸化物半導体を用いた薄膜トランジスタを有する、信頼性の高い半導体装置の作製方法の提供を目的の一とする。

【解決手段】ゲート絶縁膜を間に挟んでゲート電極と重なっている酸化物半導体膜と、酸化物半導体膜に接するソース電極またはドレイン電極とを有しており、ソース電極またはドレイン電極は、チタン、マグネシウム、イットリウム、アルミニウム、タングステン、モリブデンなどの電気陰性度が低い金属のいずれか一つまたは複数を含む混合物、金属化合物または合金を含んでおり、ソース電極またはドレイン電極中の水素濃度は酸化物半導体膜中の水素濃度の1.2倍以上、好ましくは5倍以上である。

(もっと読む)

半導体装置、集積回路、マトリックス回路、表示素子、無線通信装置、電子機器、半導体装置の製造方法

【課題】エッチングによりソース・ドレイン電極を形成しても、有機半導体層が損傷を受けることなく、良好なオン/オフ比を示す有機半導体装置、及びその製造方法を提供することを目的とする。

【解決手段】基板1と、前記基板上に形成されたゲート電極2と、ゲート電極2及び基板1上に形成されたゲート絶縁層3と、ゲート絶縁層3上に形成されたp型有機半導体層4と、有機半導体層4上に形成された保護層5と、保護層5上に形成されたソース電極8及びドレイン電極9と、を有する半導体装置を構成する。

(もっと読む)

半導体装置

【課題】LSIやCPUやメモリに用いるトランジスタのリーク電流及び寄生容量を低減することを課題の一とする。

【解決手段】半導体基板上において、酸化物半導体中で電子供与体(ドナー)となる不純物を除去することで、真性又は実質的に真性な半導体であって、シリコン半導体よりもエネルギーギャップが大きい酸化物半導体でチャネル領域が形成されるトランジスタを用い、LSIやCPUやメモリなどの半導体集積回路を作製する。半導体基板上に形成され、水素濃度が十分に低減されて高純度化された酸化物半導体層を用いるトランジスタは、リーク電流による消費電力の少ない半導体装置を実現できる。

(もっと読む)

パワーダイオード、整流器およびこれらを有する半導体装置

【課題】逆方向飽和電流の低い非線形素子(例えば、ダイオード)によりパワーダイオードまたは整流器を提供する。

【解決手段】基板101上に設けられた第1の電極105と、前記第1の電極上に接して設けられ、二次イオン質量分析法で検出される水素濃度が5×1019atoms/cm3以下である酸化物半導体膜107と、前記酸化物半導体膜上に接して設けられた第2の電極109と、前記第1の電極、前記酸化物半導体膜、及び前記第2の電極を覆うゲート絶縁膜111と、前記ゲート絶縁膜に接して設けられ、前記第1の電極、前記酸化物半導体膜、及び前記第2の電極を介して対向する複数の第3の電極113と、を有し、前記複数の第3の電極は、前記第1の電極または前記第2の電極と接続されている非線形素子によりパワーダイオードまたは整流器を構成する。

(もっと読む)

半導体装置

【課題】待機電力の低減を実現する半導体装置の提供を、目的の一とする。

【解決手段】酸化物半導体を活性層として有するトランジスタをスイッチング素子として用い、該スイッチング素子で、集積回路を構成する回路への電源電圧の供給を制御する。具体的には、回路が動作状態のときに上記スイッチング素子により、当該回路への電源電圧の供給を行い、回路が停止状態のときに上記スイッチング素子により、当該回路への電源電圧の供給を停止する。また、電源電圧が供給される回路は、半導体を用いて形成されるトランジスタ、ダイオード、容量素子、抵抗素子、インダクタンスなどの、集積回路を構成する最小単位の半導体素子を、単数または複数有する。そして、上記半導体素子が有する半導体は、結晶性を有するシリコン(結晶性シリコン)、具体的には、微結晶シリコン、多結晶シリコン、単結晶シリコンを含む。

(もっと読む)

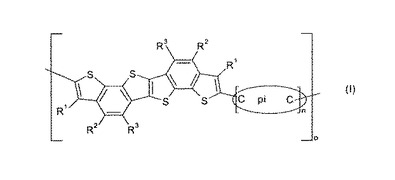

ジチエノベンゾ−チエノ[3,2−b]チオフェン−コポリマーとその溶液加工可能な高機能性半導電性ポリマーとしての利用

次式のジチエノベンゾ−チエノ[3,2−b]チオフェン−コポリマー:

【化1】

[式中、

piは、必要に応じて1〜4個のRa基で置換された単環基または多環基であり、式中

Raは、それぞれ独立して、水素、a)ハロゲン、b)−CN、c)−NO2、d)オキソ、e)−OH、f)=C(Rb)2、g)C1-20アルキル基、h)C2-20アルケニル基、i)C2-20アルキニル基、j)C1-20アルコキシ基、k)C1-20アルキルチオ基、l)C1-20ハロアルキル基、m)−Y−C3-10シクロアルキル基、n)−Y−C6-14アリール基、o)−Y−3−12員環シクロヘテロアルキル基、またはp)−Y−5−14員環ヘテロアリール基であり(上記のC1-20アルキル基とC2-20アルケニル基、C2-20アルキニル基、C3-10シクロアルキル基、C6-14アリールまたはハロアリール基、3−12員環シクロヘテロアルキル基、5−14員環ヘテロアリール基は、必要に応じて1〜4個のRb基で置換されていてもよい);

Yは、それぞれ独立して、2価のC1-6アルキル基、2価のC1-6ハロアルキル基、または共有結合であり;

R1とR2とR3はそれぞれ、独立してH、ハロゲン、CN、C1-30アルキル基、C2-30アルケニル基、C1-30ハロアルキル基、C2-30アルキニル基、C1-30アルコキシ基、C(O)−C1-20アルキル基、C(O)−OC1-20アルケニル基、Y−C3-10シクロアルキル基、−Y−3−12員環シクロヘテロアルキル基(これらはそれぞれ、ハロゲンと−CN、C1-6アルキル基、C1-6アルコキシ基、C1-6ハロアルキル基から選ばれる1〜5個の置換基で置換されていてもよい)、

−L−Ar1、−L−Ar1−Ar1、−L−Ar1−R4、または−L−Ar1−Ar1−R4であり、

Yは、それぞれ独立して、2価のC1-6アルキル基、2価のC1-6ハロアルキル基、または共有結合であり;

n=0、1、2であり;

o=1〜1000である。

(もっと読む)

半導体装置

【課題】オフ電流が小さい薄膜トランジスタによって問題なく動作することが可能な記憶素子を含む記憶装置を提供することを課題とする。

【解決手段】酸化物半導体層を有する薄膜トランジスタが少なくとも一つ設けられた記憶素子を、マトリクス状に配置した記憶装置を提供する。酸化物半導体層を有する薄膜トランジスタは、電界効果移動度が高く、且つオフ電流を小さくできるため、問題なく良好に動作させることができる。また、消費電力を低くすることもできる。このような記憶装置は、例えば酸化物半導体層を有する薄膜トランジスタが表示装置の画素に設けられている場合に、記憶装置を同一基板上に形成することができるため、特に有効である。

(もっと読む)

薄膜集積回路の作製方法及びICラベルの作製方法

【課題】シリコンウェハからなるICチップは厚いため商品容器自体に搭載する場合、表

面に凹凸が生じ、デザイン性が低下してしまった。そこで非常に膜厚の薄い薄膜集積回路

、及び薄膜集積回路を有するICチップ等を提供する。

【解決手段】薄膜集積回路を有するICチップは、従来のシリコンウェハにより形成され

る集積回路と異なり、半導体膜を能動領域(例えば薄膜トランジスタであればチャネル形

成領域)として備えることを特徴とする。このようなICチップは非常に薄いため、カー

ドや容器等の商品へ搭載してもデザイン性を損ねることがない。

(もっと読む)

半導体装置およびその作製方法

【課題】LSIやCPUやメモリに用いるトランジスタのリーク電流及び寄生容量を低減することを課題の一とする。

【解決手段】酸化物半導体中で電子供与体(ドナー)となる不純物を除去することで、真性又は実質的に真性な半導体であって、シリコン半導体よりもエネルギーギャップが大きい酸化物半導体でチャネル領域が形成される薄膜トランジスタを用い、LSIやCPUやメモリなどの半導体集積回路を作製する。水素濃度が十分に低減されて高純度化された酸化物半導体層を用いる薄膜トランジスタは、リーク電流による消費電力の少ない半導体装置を実現できる。

(もっと読む)

大面積ナノ可能マクロエレクトロニクス基板およびその使用

【課題】複数の半導体デバイスを有する電子的な基板を得るための方法および装置。

【解決手段】ナノワイヤ薄膜が、基板上に形成される。ナノワイヤ薄膜は、動作電流レベルを達成するのに十分なナノワイヤの密度を有するように形成される。複数の半導体領域が、ナノワイヤ薄膜に画定される。コンタクトが、半導体デバイス領域において形成され、それによって、電気的な接続を複数の半導体デバイスに提供する。さらに、ナノワイヤを製造するための様々な材料、p型ドーピングナノワイヤおよびn型ドーピングナノワイヤを含む薄膜、ナノワイヤヘテロ構造、発光ナノワイヤヘテロ構造、ナノワイヤを基板上に配置するためのフローマスク、ナノワイヤを成膜するためのナノワイヤ噴霧技術、ナノワイヤにおける電子のフォノン散乱を減少または除去するための技術、および、ナノワイヤにおける表面準位を減少させるための技術が、説明される。

(もっと読む)

半導体装置およびその作製方法

【課題】電気特性が良好な薄膜トランジスタ及び当該薄膜トランジスタをスイッチング素子として用いた半導体装置を提供することを目的の一とする。

【解決手段】薄膜トランジスタが、絶縁表面上に形成されたゲート電極と、ゲート電極上のゲート絶縁膜と、ゲート絶縁膜上においてゲート電極と重なっており、なおかつ、酸化物半導体が有する一または複数の金属の濃度が、他の領域よりも高い層を含む酸化物半導体膜と、層に接するように酸化物半導体膜上に形成された一対の金属酸化膜と、該金属酸化膜に接するソース電極またはドレイン電極とを有する。そして、金属酸化膜は、ソース電極またはドレイン電極に含まれる金属が酸化することで形成されている。

(もっと読む)

フレキシブル半導体装置およびその製造方法

【課題】高性能なフレキシブル半導体装置を提供すること。

【解決手段】可撓性を有するフレキシブル半導体装置であって、絶縁膜と、かかる絶縁膜の下面に位置する金属箔をエッチングすることによって形成されたソース電極およびドレイン電極と、絶縁膜の上面の一部に形成された半導体層と、ソース電極およびドレイン電極のそれぞれと、前記半導体層とを電気的に接続する取出し電極パターンと、取出し電極パターンおよび半導体層を封止する封止樹脂層と、封止樹脂層の面のうちソース電極およびドレイン電極が形成された面とは反対側の面に形成されたゲート電極とを備えたフレキシブル半導体装置。

(もっと読む)

121 - 140 / 665

[ Back to top ]