Fターム[5F110BB20]の内容

Fターム[5F110BB20]に分類される特許

81 - 100 / 665

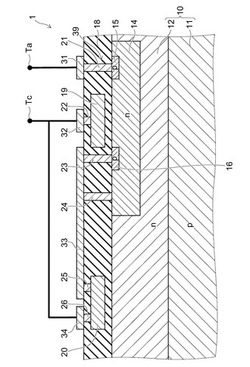

半導体装置

【課題】半導体基板へのリーク電流が少ないMOS構造をダイオードとして用いる半導体装置を提供する。

【解決手段】電界効果トランジスタと、抵抗素子20と、を備える。前記抵抗素子は、前記電界効果トランジスタのバックゲート電極24と一方のソース・ドレイン領域16との接続点23と、前記電界効果トランジスタのゲート電極19との間に接続されている。そして、前記電界効果トランジスタの他方のソース・ドレイン領域15と前記ゲート電極19との間に電圧が印加される。

(もっと読む)

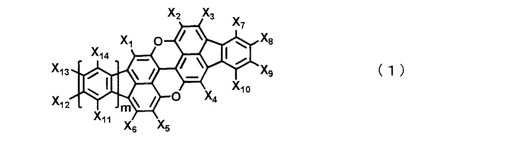

有機トランジスタ

【課題】

高い移動度、大きな電流オン/オフ比を有し、保存安定性に優れた有機トランジスタを提供する。

【解決手段】

有機半導体層を有する有機トランジスタにおいて、該有機半導体層に一般式(1)で表される化合物を少なくとも1種含有してなる有機トランジスタ。

〔式中、X1〜X14はそれぞれ独立に、水素原子、ハロゲン原子、直鎖、分岐または環状のアルキル基、直鎖、分岐または環状のアルコキシ基、直鎖、分岐または環状のアルコキシアルキル基、直鎖、分岐または環状のアルコキシアルコキシ基、あるいは置換または未置換のアリール基を表し、mは0または1を表す〕

(もっと読む)

パターン画像の形成方法

【課題】有機薄膜トランジスタソース/ドレイン電極などに適する厚みが均一で高精細なパターン画像の形成方法を提供する。

【解決手段】特定の構造単位を有するポリイミド前駆体及び該ポリイミド前駆体を脱水閉環して得られるポリイミドからなる群より選ばれる少なくとも一種の重合体を含むパターン画像下層膜形成液を基板上に塗布し、乾燥、焼成することでパターン画像下層膜を得る工程と、

得られるパターン画像下層膜に紫外線を照射しパターン画像下層膜の濡れ性を変化させる工程と、

パターン画像形成液が付着したブレードと上記パターン画像下層膜とを相対的に移動させることにより、上記パターン画像下層膜の紫外線照射領域に上記パターン画像形成液を塗布させ、乾燥する工程と、

を有することを特徴とする。

(もっと読む)

パターン付基板の作製方法、及び半導体装置の作製方法

【課題】隣接する膜パターンの間隔を制御することが可能なパターン付基板の作製方法を

提供する。また、膜パターンの幅の制御が可能で、特に、幅が細く且つ厚みのあるパター

ン付基板の作製方法を提供する。また、アンテナのインダクタンスのバラツキが少なく、

起電力の高い導電膜を有する基板の作製方法を提供することを課題とする。また、歩留ま

り高く半導体装置を作製する方法を提供することを課題とする。

【解決手段】基板、絶縁膜又は導電膜上に珪素及び酸素が結合し且つ前記珪素に不活性な

基が結合する膜を形成した後、珪素及び酸素が結合し且つ前記珪素に不活性な基が結合す

る膜表面に印刷法を用いて組成物を印刷し、組成物を焼成して膜パターンを形成すること

を特徴とする。

(もっと読む)

半導体装置の駆動方法

【課題】酸化物半導体層によってチャネル領域が形成されるトランジスタのソース及びドレインの一方に電気的に接続されたノードにおいて電荷の保持を行う半導体装置に記憶された情報の経時変化を抑制すること。

【解決手段】書き込み期間と保持期間の間に、トランジスタのゲートに強い負電位を与える期間(反転期間)を設ける。反転期間において、当該トランジスタのドレインから酸化物半導体層に対する正電荷の供給が促進される。これにより、酸化物半導体層内又は酸化物半導体層及びゲート絶縁膜の界面への正電荷の蓄積を短期間で収束させることができる。そのため、反転期間後の保持期間における当該トランジスタのドレインに電気的に接続されたノードにおける正電荷の減少を抑制することが可能である。すなわち、当該半導体装置に記憶された情報の経時変化を抑制することが可能である。

(もっと読む)

半導体装置およびその製造方法

【課題】アンテナスイッチで発生する高調波歪みをできるだけ低減できる技術を提供する。

【解決手段】界面キャリア層SCLを構成する電子の移動抑制手段として、MISFETQN1とMISFETQN2の間に電極層ELを設けて電極層ELと界面キャリア層SCLとの間に容量素子Cを形成する手段をとっている。そして、この容量素子Cの上部電極となる電極層ELに正電位を印加することにより、電極層ELに相対する界面キャリア層SCLの電子を固定している。

(もっと読む)

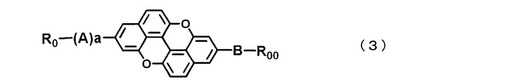

有機トランジスタ

【課題】移動度、電流オン/オフ比、保存安定性に優れた有機トランジスタを提供する。

【解決手段】下式で表される有機半導体を含有してなる有機トランジスタ。

(もっと読む)

(もっと読む)

HFET

【課題】耐圧が高いHFET(Heterojunction−FET)を提供する。

【解決手段】ヘテロ接合16aに生じる2次元電子ガスをチャネルとするHFET10であって、第1半導体領域16と、第1半導体領域16上で第1半導体領域16とヘテロ接合している第2半導体領域18と、第2半導体領域18上に形成されたソース電極20、ドレイン電極22及びゲート電極24と、第1半導体領域16と接しており、ソース電極20と導通しているp型の第3半導体領域14を有している。ゲート電極24とドレイン電極22の間の第2半導体領域18の上面のうちの、ゲート電極24に隣接する範囲の上面は、第1表面準位密度を有する第1領域40であり、第1領域40に隣接する範囲の上面は、第1表面準位密度より低い第2表面準位密度を有する第2領域42である。第3半導体領域14は、第2領域42の下側で第1半導体領域16に接している。

(もっと読む)

電源回路

【課題】回路の動作が劣化するのを抑制すること、及び、回路全体の面積を抑制することを課題とする。

【解決手段】第1の電圧が入力される第1の端子と、第2の電圧が入力される第2の端子と、前記第1の端子及び第2の端子に接続され、前記第1の電圧と第2の電圧を比較するコンパレータと、前記コンパレータから出力された第1のデジタル信号を、平均化し、積分し、デジタルPWM処理するデジタル回路と、前記デジタル回路から出力された第2のデジタル信号を増幅するPWM出力ドライバと、前記増幅された第2のデジタル信号を平滑する平滑化回路とを有する電源回路を提供する。

(もっと読む)

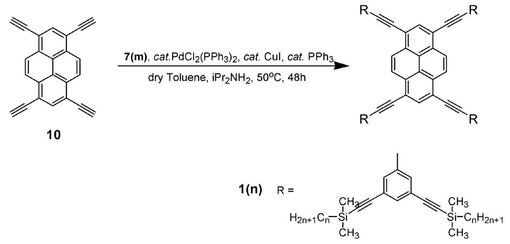

液晶性ピレン誘導体、有機半導体および有機半導体素子

【課題】新規な液晶性ピレン誘導体及び有機半導体素子等を提供する。

【解決手段】下式の反応で得られる化合物が例示される。

n;1〜10の整数

(もっと読む)

半導体組成物

【課題】高い電界効果移動度と良好な薄膜形成性とを示す半導体組成物を提供する。

【解決手段】半導体組成物は、非非晶質半導体材料と分子性ガラスとを含む。また、電子デバイスである薄膜トランジスタ(TFT10)は、半導体層70を含み、半導体層70は、非非晶質半導体材料と分子性ガラスとを含む。

(もっと読む)

有機薄膜トランジスタとその製造方法

【課題】高性能でばらつきの少ない有機薄膜トランジスタとその簡便な製造方法の提供。

【解決手段】(1)基板上にソース電極、ドレイン電極、及びソース電極とドレイン電極の間のチャネル部を構成するインクジェット法で形成された有機半導体層を有し、前記チャネル部は、平面視において前記有機半導体層の輪郭の最大幅Rを与える線分の中点を含まず、チャネル長Lが、前記最大幅Rに対し「L<R/2」を満たす有機薄膜トランジスタ。

(2)前記有機半導体層では、前記輪郭から中点に向かって結晶粒が配向しており、前記ソース電極領域から成長した結晶粒と、ドレイン電極領域から成長した結晶粒とが衝突して形成される結晶粒界αが前記チャネル部に無い(1)記載の有機薄膜トランジスタ。

(3)有機半導体材料を含むインクを用い、インクジェット法により有機半導体層を形成する有機薄膜トランジスタの製造方法。

(もっと読む)

不揮発性記憶装置及びその製造方法

【課題】電磁波又は光が照射されても広義のリーク電流が増大せず、書き込み状態及び消去状態の安定した判別を可能とする。

【解決手段】電磁波シールド性能及び遮光性能を持つ層30及び31のどちらにも半導体層60の領域面積よりも大きい領域面積を持たせ、且つこの層30及び31を、半導体層60の上下を挟み込むように設けることで、電磁波及び光が半導体層60に侵入することを防ぐことができる。この結果、広義のリーク電流が格段に低減され、書き込み状態及び消去状態の判別を安定して行うことができる。

(もっと読む)

トランジスタ

【課題】ソース電極(ドレイン電極)と、ゲート電極との重畳部に生じる寄生容量値を低減させても、オン電流値をほぼ維持できる新たな電極構造のトランジスタを提供することを課題の一とする。

【解決手段】トランジスタのソース電極及びドレイン電極の電極形状を櫛歯形状にすることによって寄生容量値を低減させる。また、櫛歯状電極の先端部の幅や、電極歯部間の間隔を制御することによって、電極歯部の側面から流れる曲線電流を発生させることができる。この曲線電流が、電極形状を櫛歯形状にすることにより減少する直線電流を補うため、寄生容量値を低減させても、低減させる前とほぼ変わらないオン電流値を維持させることができる。

(もっと読む)

分周回路

【課題】分周回路の動作不良を抑制する。

【解決手段】第1又は第2のクロック信号に従って2×X個(Xは2以上の自然数)のパルス信号を生成して出力するシフトレジスタと、2×X個のパルス信号に従って、第1のクロック信号の周期のX倍の周期である第3のクロック信号となる信号を生成して出力する分周信号出力回路と、を具備し、分周信号出力回路は、ゲートのそれぞれに、2×X個のパルス信号における1個目乃至X個目のパルス信号のうち、互いに異なるパルス信号が入力され、第3のクロック信号となる信号の電圧を第1の電圧に設定するか否かを制御するX個の第1のトランジスタと、ゲートのそれぞれに、2×X個のパルス信号におけるX+1個目乃至2×X個目のパルス信号のうち、互いに異なるパルス信号が入力され、第3のクロック信号となる信号の電圧を第2の電圧に設定するか否かを制御するX個の第2のトランジスタと、を備える。

(もっと読む)

シリコン・オン・インシュレータ構造において電界効果トランジスタを備える半導体デバイス

【課題】シリコン・オン・インシュレータ構造において複数電界効果トランジスタを備える新規な半導体デバイスを提供する。

【解決手段】基板200と、基板上の酸化物層190と、酸化物層上の半導体層230を備えるSOI構造の電解効果トランジスタと、半導体・オン・インシュレータ構造(SeOI構造)のFETであって、基板内にチャンネル領域200を備え、前記FET構造のBOX構造酸化物層190の少なくとも一部である誘電体をゲート誘電体とし、基板200をチヤネルとする半導体デバイス。

(もっと読む)

成膜装置、及び半導体装置の作製方法

【課題】不純物が混入しない酸化物半導体膜を成膜する成膜装置を提供することを課題とする。不純物が混入しない酸化物半導体膜を含む半導体装置の作製方法を提供することを課題とする。

【解決手段】成膜装置を含む環境から不純物を排除することにより、成膜装置の外部から成膜装置内へ不純物を含む気体が漏洩(リーク)する現象を防げばよい。また、当該装置を用いて成膜した、不純物が低減された酸化物半導体層を半導体装置に適用すればよい。

(もっと読む)

半導体基板の作製方法及び半導体装置の作製方法

【課題】単結晶半導体基板に付着する異物の影響を低減し、歩留まりよく半導体基板を作製することを目的の一とする。安定な特性を有する半導体装置を歩留まりよく作製することを目的の一とする。

【解決手段】半導体基板の作製工程において、単結晶半導体基板に脆化領域を形成する際、単結晶半導体基板表面に対して複数の(少なくとも二つ以上の)異なる角度で斜め方向から水素イオンを照射することによって、単結晶半導体基板に付着する異物の影響を低減し、均一な単結晶半導体層を有する半導体基板を歩留まりよく作製することができる。

(もっと読む)

薄膜トランジスタ基板および薄膜トランジスタの製造方法

【課題】本発明は、スイッチング特性に優れたTFT基板を提供することを主目的とする。

【解決手段】本発明は、基板と、上記基板上に形成された半導体層および上記半導体層と接するように形成された半導体層接触絶縁層を有する薄膜トランジスタと、を有し、上記半導体層接触絶縁層の少なくとも一つが、非感光性ポリイミド樹脂からなる非感光性ポリイミド絶縁層であることを特徴とする薄膜トランジスタ基板を提供することにより、上記目的を達成する。

(もっと読む)

薄膜素子用基板の製造方法、薄膜素子の製造方法および薄膜トランジスタの製造方法

【課題】本発明は、表面平滑性に優れ、薄膜素子の特性劣化を抑制することが可能な薄膜素子用基板の製造方法を提供することを主目的とする。

【解決手段】本発明は、所定の方法で算出した相対溶存酸素飽和率が95%以下となるように、ポリイミド樹脂組成物を脱気する脱気工程と、金属基材上に、上記ポリイミド樹脂組成物を塗布して絶縁層を形成する絶縁層形成工程とを有し、上記絶縁層の表面粗さRaが30nm以下であることを特徴とする薄膜素子用基板の製造方法を提供することにより、上記目的を達成する。

(もっと読む)

81 - 100 / 665

[ Back to top ]