Fターム[5F110BB20]の内容

Fターム[5F110BB20]に分類される特許

41 - 60 / 665

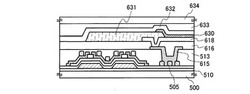

発光装置の作製方法

【課題】微細な配線パターンを備えた発光装置の作製方法の提供。

【解決手段】Inと、Gaと、Znとを有する酸化物半導体層を形成し、酸化物半導体層上に第1の導体パターンを形成し、第1の導体パターンより微細な第2の導体パターンを形成し、前記第2の導体パターンと電気的に接続する発光素子を形成する発光装置の作製方法であって、第2の導体パターンは、酸化物半導体層を横断する。

(もっと読む)

薄膜トランジスタ装置およびその製造方法

【課題】十分なキャパシタ容量が得られ、リーク電流や寄生容量を抑制した薄膜トランジスタ装置およびその製造方法を提供する。

【解決手段】薄膜トランジスタを備え、そのゲート電極111、ソース電極131、ドレイン電極132、バス配線、画素電極133、ゲート絶縁膜121、層間絶縁膜122、半導体層141の全部もしくは一部が塗布法もしくは印刷法で形成されてなり、ゲート絶縁膜121および/もしくは層間絶縁膜122が連続膜から構成され、連続膜が薄膜部と厚膜部から構成されてなる。

(もっと読む)

薄膜トランジスタ及びその製造方法並びに画像表示装置

【課題】薄膜トランジスタにおいて、ゲート絶縁膜に直接ストライプ状に凹部を形成することで隔壁形成プロセスを省き、前記凹部をガイドとして塗布法により精度よく半導体溶液を所望の場所に形成し、トランジスタ素子分離を行うことのできる薄膜トランジスタの構造を提供する。また、その構造を用いた薄膜トランジスタの製造方法、及びそれを用いたが画像表示装置を提供すること。

【解決手段】基板と、前記基板上に形成されたゲート電極と、前記基板上及び前記ゲート電極上のゲート絶縁体層と、前記ゲート絶縁体層に形成された凹部と、前記絶縁体層の凹部内に形成される半導体層と、前記半導体層上の中央部に設けられる保護膜と、前記半導体層の両端部で接続されるソース電極とドレイン電極と、を有する薄膜トランジスタにおいて、前記ゲート絶縁体層の凹部がストライプ状に形成されていることを特徴とする薄膜トランジスタとする。

(もっと読む)

トランジスタアレイ、およびその製造方法

【課題】簡略化された構成を有するトランジスタアレイを、簡易的に製造することが可能なトランジスタアレイの製造方法を提供することを主目的とする。

【解決手段】金属基板を用い、上記金属基板上に、絶縁性材料からなり、貫通孔を有する絶縁層を形成する絶縁層形成工程と、上記絶縁層上に、ドレイン電極が上記絶縁層に形成された貫通孔を介して上記金属基板に接続されるように薄膜トランジスタを形成する、薄膜トランジスタ形成工程と、上記金属基板をパターニングすることにより、上記金属基板を画素電極とする画素電極形成工程と、を有することを特徴とする、トランジスタアレイの製造方法を提供することにより、上記課題を解決する。

(もっと読む)

キサンテン系半導体組成物

【課題】高移動度で環境安定性が高く塗布形成可能な有機半導体を提供する。

【解決手段】特定構造の縮合キサンテンコアを含む低分子半導体化合物を用いる。また、ポリマーバインダーと当該低分子半導体とを含む組成物も用いられる。この組成物から作られる半導体層は、空気中で非常に安定であり、高い移動性を有する。これらの半導体組成物は、電子機器(例えば、薄膜トランジスタ(TFT))で、半導体層のような層を作成するのに有用である。

(もっと読む)

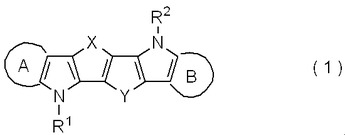

含ピロールヘテロアセン化合物、該化合物の製造方法、該化合物を含む薄膜及び該薄膜を含む有機半導体デバイス

【課題】有機半導体活性層の薄膜を与え得る新規な化合物が求められている。

【解決手段】式(1)

(式中、X及びYは、硫黄原子、酸素原子、セレン原子、テルル原子又はSO2を表す。環構造A及び環構造Bは、芳香族炭化水素環又は芳香族複素環を表す。該芳香族複素環は単一の環構造である。

R1およびR2は、水素原子、炭素数1〜30のアルキル基、炭素数1〜30のアルコキシ基、炭素数2〜30のアルケニル基、炭素数2〜30のアルキニル基、炭素数1〜30のアルキルチオ基、炭素数6〜20のアリール基、炭素数4〜20のヘテロアリール基を表す。)

で表される含ピロールヘテロアセン化合物。

(もっと読む)

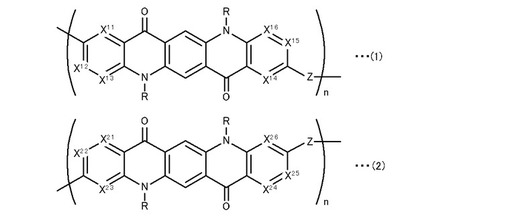

高分子化合物、高分子有機半導体材料及び有機半導体デバイス

【課題】良好な電荷移動度を示す高分子化合物、高分子有機半導体材料及び有機半導体デバイスを提供する。

【解決手段】高分子化合物は、下記一般式(1)又は(2)のいずれかで表される。 (もっと読む)

(もっと読む)

薄膜トランジスタの製造方法

【課題】高温処理プロセスを適用することなく、酸化物半導体膜を効率的に製造できる薄膜トランジスタの製造方法を提供する。

【解決手段】

基板1上にゲート電極2を所定のパターンで形成する工程と、ゲート電極2を覆うゲート絶縁膜3を所定のパターンで形成する工程と、ゲート絶縁膜3上にアモルファス酸化物膜4’を所定のパターンで形成する工程と、アモルファス酸化物膜4’上にソース電極6S及びドレイン電極6Dを所定のパターンで形成する工程と、ソース・ドレイン電極6S,6D間で露出するアモルファス酸化物膜4’を少なくとも覆う保護膜7を形成する工程とを有する。このアモルファス酸化物膜4’の形成工程では、RFスパッタリング法でアモルファス酸化物膜4’を成膜し、保護膜7の形成工程では、RFスパッタリング法で保護膜7を成膜して、アモルファス酸化物膜4’を半導体化する。

(もっと読む)

半導体装置及び半導体リレー

【課題】小型化と出力容量の低下を同時に図る。

【解決手段】従来の半導体装置では、ドレイン領域やソース領域の深さが活性層の厚みよりも浅く(薄く)なっていた。これに対して本実施形態の半導体装置1では、活性層3の厚みを薄くしてドレイン領域4A,4Bやソース領域5A,5Bの深さを活性層3の厚みと同じにしている。その結果、N型のドレイン領域4A,4B及びソース領域5A,5BとP型のベース領域7A,7BとのPN接合の接合面積が従来よりも減少するので、当該PN接合に生じる出力容量Cossの低下を図ることができる。しかも、特許文献1記載の従来例に比べて、2つのダイオードや配線パターンが不要であるから小型化を図ることもできる。

(もっと読む)

半導体装置及びその製造方法

【課題】ソース及びドレインのいずれか一方に高抵抗成分が付加されたときドレイン電流の低下を抑制する。

【解決手段】一つの実施形態によれば、半導体装置は基板、第一のソース及びドレイン、第二のソース及びドレイン、ゲート電極膜が設けられる。第一のソース及びドレインと第二のソース及びドレインは、基板表面に設けられる。第二のソース及びドレインの一方は、第一のソース及びドレインの一方に隣接配置される。第二のソース及びドレインの他方は、第一のソース及びドレインの他方に隣接配置される。ゲート電極膜は、第一及び第二のソース及びドレインの一方と第一及び第二のソース及びドレインの他方の間の基板表面上に設けられ、ゲート絶縁膜を介して設けられる。第一のソース及びドレインとゲート電極膜は第一のFETを構成し、第二のソース及びドレインとゲート電極膜は第二のFETを構成する。

(もっと読む)

ジチオケトピロロピロール系ポリマー

【課題】高いフィールド効果移動性、空気安定性、及び良好な溶解性を示す半導体ポリマーを提供すること。

【解決手段】ピロロ[3,4−C]ピロールー2,5−ジチオンを必須単位とし、該化合物の3−位及び6−位を結合手として繰り返し単位を構成し、エテニル、エチニル、アリール、置換アリール、ヘテロアリール、置換ヘテロアリール等を共重合成分として含むポリマー。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】大面積のガラス基板上に薄膜からなる集積回路を形成した後、基板から剥離を行い、接触、好ましくは非接触でデータの受信または送信が可能な微小なデバイスを大量に効率よく作製する方法を提供することを課題とする。特に薄膜からなる集積回路は、非常に薄いため、搬送時に飛んでしまう恐れがあり、取り扱いが難しかった。

【解決手段】

本発明は、分離層に対して少なくとも異なる2種類の方法を用いてダメージ(レーザ光照

射によるダメージ、エッチングによるダメージ、または物理的手段によるダメージ)を複

数回与えることにより、基板から被剥離層を効率よく剥離する。また、剥離後のデバイス

に反りを持たせることによって、個々のデバイスの取り扱いを容易とする。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】特性の良好な半導体装置(薄膜トランジスタ)を製造する。

【解決手段】本発明は、(a)基板SUBの上方に、第1金属酸化物を含有する半導体からなる導電層を形成する工程と、(b)導電層上に第2金属酸化物を含有する半導体からなる犠牲層SLを形成する工程と、(c)導電層と犠牲層SLとの積層膜を加工する工程と、(d)上記(c)工程の後、犠牲層SL上に、金属膜を形成する工程と、(e)上記(d)工程の後、上記金属膜の第1領域をドライエッチングにより除去する工程と、(f)上記(e)工程の後、上記第1領域の上記犠牲層SLをウェットエッチングにより除去する工程と、を有し、上記(c)工程と、上記(f)工程との間に、(g)導電層に熱処理を施し、導電層を結晶化し、導電層CLcとする工程を有する。かかる工程によれば、ドライエッチングにより生じた犠牲層SLのダメージ領域DRを除去できる。

(もっと読む)

テラヘルツ波素子

【課題】単色性が強く、高効率にテラヘルツ波を発生または検出することができるテラヘルツ波素子を提供する。

【解決手段】テラヘルツ波素子100は、バッファ層102と電子供給層104とのヘテロ接合を含む半導体多層構造101〜104と、半導体多層構造101〜104上に形成されたゲート電極105、ドレイン電極106およびソース電極107とを有し、ゲート電極105とヘテロ接合界面との間の静電容量は、ドレインとソースとの間を流れる電流の方向と直交する方向に周期的に、第1の静電容量と第1の静電容量の値と異なる第2の静電容量とを有している。

(もっと読む)

半導体化合物

【課題】空気安定性、良好な溶解度、および高い移動度を持つ有機薄膜トランジスタ用半導体を提供する。

【解決手段】特定構造のチアキサンテノチアキサンテン化合物を活性層として用いる。チアキサンテノチアキサンテン化合物は主に結晶性または液晶である。この化合物は、空気安定性、良好な溶解度、および高い移動度を確実にするように設計される。有機薄膜トランジスタは一般に、基板20上に、ゲート電極30、ソース電極50およびドレイン電極60、ゲート電極をソースおよびドレイン電極と分離する電気絶縁ゲート誘電体層40、およびゲート誘電体層と接触し、ソースおよびドレイン電極を架橋する半導体層70を含む。

(もっと読む)

有機薄膜トランジスタ

【課題】本発明は、ゲート絶縁膜の絶縁耐圧を高めることができ、低電圧で動作させることができる有機薄膜トランジスタを提供することを目的とする。

【解決手段】ゲート電極20と、該ゲート電極上に形成されたゲート絶縁膜30とを有する有機薄膜トランジスタであって、

前記ゲート絶縁膜は、自己組織化単分子膜31上に高分子絶縁膜32が形成された積層構造を有することを特徴とする。

(もっと読む)

電界効果型トランジスタの製造方法

【課題】電界効果型トランジスタの活性層に好適に用いられる非晶質酸化物の製造方法を提供する。

【解決手段】基板1上に、非晶質酸化物層2を形成する前に、基板1表面にオゾン雰囲気中で紫外線を照射したり、基板1表面にプラズマを照射したり、あるいは基板1表面を過酸化水素を含有する薬液により洗浄する。または、非晶質酸化物層2を形成する工程をオゾンガス、窒素酸化物ガス等の少なくともいずれかを含む雰囲気中で行う。または、基板1上に、非晶質酸化物層2を形成する後に、非晶質酸化物層2の成膜温度よりも高い温度で熱処理する工程を含む。

(もっと読む)

電界効果型トランジスタの製造方法

【課題】電界効果型トランジスタの活性層に好適に用いられる非晶質酸化物の製造方法を提供する。

【解決手段】基板1上に、非晶質酸化物層2を形成する前に、基板1表面にオゾン雰囲気中で紫外線を照射したり、基板1表面にプラズマを照射したり、あるいは基板1表面を過酸化水素を含有する薬液により洗浄する。または、非晶質酸化物層2を形成する工程をオゾンガス、窒素酸化物ガス等の少なくともいずれかを含む雰囲気中で行う。または、基板1上に、非晶質酸化物層2を形成する後に、非晶質酸化物層2の成膜温度よりも高い温度で熱処理する工程を含む。

(もっと読む)

半導体装置

【課題】非接触でデータの送受信が可能な半導体装置は、鉄道乗車カードや電子マネーカ

ードなどの一部では普及しているが、さらなる普及のためには、安価な半導体装置を提供

することが急務の課題であった。上記の実情を鑑み、単純な構造のメモリを含む半導体装

置を提供して、安価な半導体装置及びその作製方法の提供を課題とする。

【解決手段】有機化合物を含む層を有するメモリとし、メモリ素子部に設けるTFTのソ

ース電極またはドレイン電極をエッチングにより加工し、メモリのビット線を構成する導

電層とする。

(もっと読む)

電子機器

【課題】高い移動度と優れた安定性を持つ薄膜トランジスタと、それを用いた電子機器を提供する。

【解決手段】薄膜トランジスタの活性層は、2層の半導体層を備えている。第1の副層は、特定構造のポリチオフェンとカーボンナノチューブとを含む。第2の副層は、特定構造のポリチオフェンを含み、カーボンナノチューブを含まない。2層の半導体層を形成した後、これらの半導体層を一緒にアニールしても良い。カーボンナノチューブはポリチオフェンを含む分散液の塗布により成膜される。

(もっと読む)

41 - 60 / 665

[ Back to top ]