Fターム[5F110GG02]の内容

Fターム[5F110GG02]に分類される特許

81 - 100 / 7,158

半導体装置及びその製造方法

【課題】動作速度を向上し消費電力を低減しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板に第1の領域を画定する第1の素子分離絶縁膜と、半導体基板の第1の領域に形成された第1導電型の第1の導電層と、半導体基板上に形成され、第1の領域の一部である第2の領域に第1の導電層に接続して形成された第1導電型の第2の導電層と、第1の領域の他の一部である第3の領域に第1の導電層に接続して形成された第1導電型の第3の導電層とを有する半導体層と、半導体層内に設けられ、第2の導電層と第3の導電層とを分離する第2の素子分離絶縁膜と、第2の導電層上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成され、第3の導電層を介して第1の導電層に電気的に接続されたゲート電極とを有する。

(もっと読む)

CMOS半導体装置の製造方法及びCMOS半導体装置

【課題】マイクロコンタクト印刷の版を凹版として使用し、微細な電気回路と高生産性のCMOS半導体装置の製造方法を提供するものである。

【解決手段】Pチャネル型電界効果トランジスタのPチャネル領域101とNチャネル型電界効果トランジスタのNチャネル領域102とを、凹版601を用いた印刷によって形成するようにし、凹版601が、第1凹部602と第2凹部603とを備え、インクジェット法によって、第1凹部602にP型半導体インク111を供給し、第2凹部603にN型半導体インク112を供給する工程と、インク供給後に、凹版601を被印刷基板001に押しつけて、第1凹部602に供給したP型半導体インク111と第2凹部603に供給したN型半導体インク112とを一括して被印刷基板001に転写する工程と、を含むCMOS半導体装置の製造方法を提供する事により、上記課題を解決する。

(もっと読む)

電界効果トランジスタ

【課題】 装置規模を増大させることなく、測定対象の検出感度を高く維持することができる技術を提供することを目的とする。

【解決手段】 半導体基板と、半導体基板上に間隔を空けて形成されるソース領域およびドレイン領域と、絶縁層を介してソース領域およびドレイン領域に隣接するように、半導体基板上に形成されるゲート領域と、ソース領域とドレイン領域との間の静電結合による容量を制御する容量制御部と、を備える。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】オン抵抗を増加させることなく、ノーマリーオフとなる半導体装置を提供する。

【解決手段】基板11の上に形成された第1の半導体層13と、第1の半導体層13の上に形成された第2の半導体層14と、第2の半導体層14の上に形成された第3の半導体層15と、第3の半導体層15の上に形成されたゲート電極21と、第2の半導体層14の上に形成されたソース電極22及びドレイン電極23と、を有し、第3の半導体層15には、半導体材料にp型不純物元素がドープされており、第3の半導体層において、ゲート電極の直下にはp型領域15aが形成されており、p型領域15aを除く領域は、p型領域15aよりも抵抗の高い高抵抗領域15bが形成されている半導体装置。

(もっと読む)

液晶表示装置の製造方法

【課題】本発明は、製造工程を単純化して透明導電膜上に金属膜が積層された積層構造を有する共通電極配線を製造することができる液晶表示装置の製造方法を提供する。

【解決手段】液晶表示装置の製造方法であって、透明導電膜10上に金属膜11が積層された積層構造を有する枠状の共通電極配線12と、透明導電膜10の配線幅よりも小さい配線幅を有する共通電極13と、共通電極配線12の透明導電膜10の配線幅よりも小さい配線幅を有する画素電極14とからなる横電界方式において、感光性樹脂膜15をエッチングマスクにして等方性エッチングにより、共通電極13および画素電極14となる透明導電膜10上に積層された、感光性樹脂膜15の下側に位置する金属膜11を除去するとともに、共通電極配線12となる透明導電膜上10に積層された、感光性樹脂15の下側に位置する金属膜11の側面の一部を除去する工程を含む。

(もっと読む)

横型半導体装置及びその製造方法

【課題】既存のCMOS製造工程に対して工程の追加や変更を行うことなく、素子に要求される耐圧に応じて横型半導体装置が有するLocos酸化膜を最適に制御することができる、横型半導体装置の製造方法を提供する。

【解決手段】半導体基板(100、101)上のLocos形成領域に、遮蔽部及び開口部が所定の幅及び間隔で設けられたパターン(113a、113b)を有するマスク(113)を形成する(工程3a、3b)。マスク(113)を用いた熱酸化処理を施してLocos形成領域を酸化させ、半導体基板(100、101)のドリフト領域上に厚さが異なる(115a、155b)Locos酸化膜(105a、105b)を同時に形成する(工程4a、4b)。

(もっと読む)

半導体装置

【課題】結晶性の優れた酸化物半導体層を形成して電気特性の優れたトランジスタを製造

可能とし、大型の表示装置や高性能の半導体装置等の実用化を図ることを目的の一つとす

る。

【解決手段】第1の加熱処理で第1の酸化物半導体層を結晶化し、その上部に第2の酸化

物半導体層を形成し、温度と雰囲気の異なる条件で段階的に行われる第2の加熱処理によ

って表面と略垂直な方向にc軸が配向する結晶領域を有する酸化物半導体層の形成と酸素

欠損の補填を効率良く行い、酸化物半導体層上に接する酸化物絶縁層を形成し、第3の加

熱処理を行うことにより、酸化物半導体層に再度酸素を供給し、酸化物絶縁層上に、水素

を含む窒化物絶縁層を形成し、第4の加熱処理を行うことにより、少なくとも酸化物半導

体層と酸化物絶縁層の界面に水素を供給する。

(もっと読む)

スパッタリングターゲット

【課題】高密度かつ低抵抗のスパッタリングターゲット、電界効果移動度の高い薄膜トランジスタを提供する。

【解決手段】Gaをドープした酸化インジウム、又はAlをドープした酸化インジウムを含み、正4価の原子価を示す金属を、Gaとインジウムの合計又はAlとインジウムの合計に対して100原子ppm超1100原子ppm以下含み、結晶構造が、実質的に酸化インジウムのビックスバイト構造からなる焼結体を含むスパッタリングターゲット。

(もっと読む)

横型の絶縁ゲート型バイポーラトランジスタを備えた半導体装置

【課題】オン電圧の低減と、破壊耐量確保、高速スイッチングを同時に実現できる横型IGBTを提供する。

【解決手段】エミッタ側にn型バリア層15を形成することで、ホールのバリアとして機能させ、コレクタ側から注入されたホールがエミッタ側のチャネルpウェル層6に流れ出てホール濃度が低下することを防止する。これにより、エミッタ近傍のn-型ドリフト層2内のキャリア濃度を上げることが可能となり、オン電圧の低減が可能となる。また、コレクタ側において、コレクタ電極12のうちp+型層4aと接触している部分をオーミック接触、p型層4bと接触している部分をショットキー接触とする。このショットキー接触とされた部分において、コレクタ側からのホールの注入が抑制され、蓄積キャリアを低減して、寄生バイポーラトランジスタがオンし難くなるようにできる。よって、低オン電圧を維持しながらスイッチング耐圧を確保することが可能となる。

(もっと読む)

半導体装置

【課題】耐圧の低下を抑制しつつ電流駆動能力の向上と小型化とを実現できる半導体装置を提供する。

【解決手段】半導体装置1は、SOI基板の半導体層の上面に沿って形成されたゲート電極31と、ソース拡散領域181〜18Nと、電荷収集領域191〜19N+1と、ドレイン拡散領域16と、電界緩和領域17とを備える。ソース拡散領域181〜18Nと電荷収集領域191〜19N+1とは、Y軸方向に沿って交互に配列されている。ソース拡散領域181〜18Nの各々の幅をWeffとし、ゲート電極31の長さをLgとし、ゲート電極31とドレイン拡散領域16との互いに対向する端部間の距離をLdriftとするとき、Weff/2≦Lg+Ldrift/2、との関係式が成立する。

(もっと読む)

半導体装置

【課題】メモリの大容量化と図りつつ、消費電力を軽減でき、且つ、消費電力を一定にす

る。

【解決手段】メモリを、複数のメモリブロックを対称に配置して構成する。また、メモリ

に供給されるアドレス信号のうち、特定の信号の組み合わせにより、データ読み出しまた

は書き込みの対象となるメモリセルを含むメモリブロックを一意に特定する。さらに、当

該メモリブロック以外のメモリブロックに供給される信号を一定値に保つ。このようにす

ることで、メモリアレイにおけるビット線の配線長を短縮し、負荷容量を軽減すると同時

に、メモリ内のあらゆるアドレスのメモリセルに対するデータ読み出しもしくは書き込み

において、消費電流を一定にできる。

(もっと読む)

半導体装置、薄膜トランジスタ基板および表示装置

【課題】金属酸化物を用いた絶縁膜を低温プロセスで結晶化することが可能で、これによりガラス基板やプラスチック基板上に特性の向上が図られた素子を設けることが可能な半導体装置を提供する。

【解決手段】基板上に、金属酸化物を用いた絶縁膜と半導体薄膜とが積層形成された半導体装置であって、絶縁膜はゲート絶縁膜として用いられ、ゲート絶縁膜に接する側にゲート電極が積層形成され、絶縁膜および半導体薄膜は結晶化され、かつ、ゲート電極と重なる部分の結晶性が他の部分の結晶性よりも高いものである。

(もっと読む)

Cu−Mn合金スパッタリングターゲット材、それを用いた薄膜トランジスタ配線及び薄膜トランジスタ

【課題】高いバリア性を有するCu−Mn合金膜を形成する。

【解決手段】半導体素子の配線の形成に用いられるCu−Mn合金スパッタリングターゲット材10であって、濃度が8原子%以上30原子%以下のMnと、不可避的不純物とを含むCu−Mn合金からなり、Cu−Mn合金の平均結晶粒径が10μm以上50μm以下である。

(もっと読む)

半導体装置およびその製造方法

【課題】フォトダイオードとトランジスタとが絶縁膜を介して同一の半導体基板に形成された半導体装置の、フォトダイオードを形成する半導体層と絶縁膜との界面のリーク電流を小さくする。

【解決手段】一導電型の半導体層11と、半導体層の主面151に設けられた反対導電型の半導体領域182と、半導体層11の主面151に半導体領域182と離間して設けられた一導電型で半導体層11より高不純物濃度の半導体領域191、192と、少なくとも半導体領域182と半導体領域と191、192の間の半導体層11の主面151に設けられた一導電型で半導体層11より高不純物濃度で半導体領域191、192よりも低不純物濃度の半導体領域99と、を備えるフォトダイオード30と、半導体層11の主面151上に設けられた絶縁層10と、絶縁層10上に設けられ、トランジスタ素子40が形成された半導体層9と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】プロセス条件の見直しを最小限に抑制しつつ電気的特性を向上させることができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置1は、半導体構造11の上面領域に形成された島状の絶縁膜20と、絶縁膜20の上面領域に配列された複数の凸状絶縁部23と、これら凸状絶縁部23と絶縁膜20とを被覆する層間絶縁膜26とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】トレンチ分離構造の上面の周縁部にディボットが形成されても、このディボットに起因するゲート絶縁膜の破壊を防止することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置1は、トレンチ分離構造20Bと、トレンチ分離構造20Bで区画される活性領域上に形成されたゲート絶縁膜30と、ゲート絶縁膜30の上面からトレンチ分離構造20Bの上面まで延在するゲート電極層31と、ゲート電極層31の両側に形成された第1及び第2の不純物拡散領域13D,13Sとを備える。ゲート電極層31は、ゲート絶縁膜30と第1の不純物拡散領域13Dとの間の領域に貫通孔31hを有し、貫通孔31hは、トレンチ分離構造20Bの上面の周縁部の直上に形成されている。

(もっと読む)

積層配線、該積層配線を用いた半導体装置及びその製造方法

【課題】マイクロクリスタルシリコン薄膜と金属薄膜との過剰なシリサイド化反応を抑制して、マイクロクリスタルシリコン薄膜の膜剥れを防止する。

【解決手段】半導体装置20の配線として備えられ、マイクロクリスタルシリコン薄膜8と該薄膜上に形成された金属薄膜9とから成る積層配線であって、マイクロクリスタルシリコン薄膜8の結晶組織を構成している結晶粒には、半導体装置の製造時の熱処理で生じた金属薄膜9とのシリサイド化反応に起因して膜厚方向に成長した柱状の結晶粒が含まれ、マイクロクリスタルシリコン薄膜8の膜厚方向の長さがマイクロクリスタルシリコン薄膜8の膜厚の60%以上である柱状の結晶粒が、マイクロクリスタルシリコン薄膜8の結晶粒の全数の6%以上15%以下となるように形成されている。

(もっと読む)

表示装置及び表示装置の作製方法

【課題】TFTの特性ばらつきに起因する、画素間における発光素子の輝度のばらつきを低減し、信頼性が高く、画質の優れた表示装置を提供することを目的とする。

【解決手段】発光素子に接続するTFTを複数個、少なくとも2つ設け、それぞれのTFTの活性層を形成する半導体領域の結晶性を異ならせるものである。

当該半導体領域は、非晶質半導体膜をレーザーアニールにより結晶化させたものが適用されるが、結晶性を異ならせるために、連続発振レーザービームの走査方向を変えて、結晶成長の方向を互いに異ならせる方法を適用する。或いは、連続発振レーザービームの走査方向は同じとしても、個々の半導体領域間でTFTのチャネル長方向を変えて、結晶の成長方向と電流の流れる方向を異ならせる方法を適用する。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】チャネル領域にシリコンを含まない材料を用いる半導体装置であって、微細化に伴いゲート絶縁層が薄膜化されても、ゲートリーク電流が抑制された半導体装置を提供する。

【解決手段】ゲート絶縁層として熱酸化シリコン層を用いる。熱酸化シリコン層を用いることで、CVD法やスパッタリング法で形成された酸化シリコン層を用いる場合よりゲートリーク電流を抑制することができる。ゲート絶縁層に熱酸化シリコン層を用いるために、チャネル領域を含む半導体層を形成する基板とは別にシリコン基板を用意し、シリコン基板上に熱酸化シリコン層を形成する。そして熱酸化シリコン層を、チャネル領域を含む半導体層に貼り合わる。このようにして、半導体層の上に熱酸化シリコン層を形成し、熱酸化シリコン層をゲート絶縁層として用いたトランジスタを形成する。

(もっと読む)

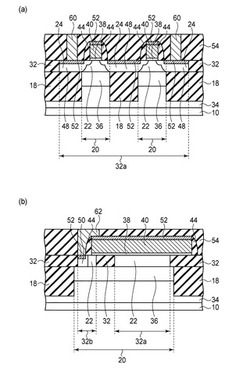

液晶パネル用基板、液晶パネル、電子機器及び投射型表示装置

【課題】半導体を基板とする液晶パネルは、ウェル領域があるため、漏れ光がトランジスタ部分のみでなくそこから離れた半導体基板を通過しただけで光リーク電流が流れることがある。この光リーク電流が、ガラス基板上にスイッチング素子としてのTFTを配置した液晶パネルに比べて多くなるという欠点がある。

【解決手段】反射電極となる画素電極(14)と、画素電極への電圧印加を制御するスイッチング素子とを有する画素単位が基板上にマトリックス状に配置されてなる液晶パネル用基板において、両素電極とスイッチング素子の端子電極を構成する導電層(6a)との間に、両者を接続するためのコンタクトホールを形成し、このコンタクトホールの形成箇所を囲む開口を有し、隣接する複数の画素電極の間の領域には開口を有さない遮光層を、画素電極と導電層との間に設けることにより、画素電極どうしの隙間から漏込む光による弊害を防ぐ。

(もっと読む)

81 - 100 / 7,158

[ Back to top ]