Fターム[5F110GG02]の内容

Fターム[5F110GG02]に分類される特許

121 - 140 / 7,158

半導体装置

【課題】信頼性の高い半導体装置を歩留まり良く製造する技術を提供する。

【解決手段】基板上に設けられ、一対の不純物領域の間に設けられたチャネル形成領域を

含む島状の半導体層と、半導体層の側面に接して設けられた第1絶縁層と、チャネル形成

領域上に設けられ、半導体層を横断するように設けられたゲート電極と、チャネル形成領

域及びゲート電極の間に設けられた第2絶縁層と、半導体層及び前記ゲート電極上に形成

された第3絶縁層と、第3絶縁層を介して、不純物領域と電気的に接続される導電層と、

を有する。不純物領域はチャネル形成領域と比較して膜厚が大きい領域を有し、且つ該膜

厚が大きい領域で導電層が接続されている。第2絶縁層は、少なくともゲート電極が重畳

する領域の半導体層の側面に設けられた第1絶縁層を覆う。

(もっと読む)

表示装置

【課題】消費電力が抑制された表示装置を提供する。

【解決手段】第1のトランジスタ、第2のトランジスタ、及び一対の電極を有する発光素

子を含む画素が複数設けられた画素部を有し、前記第1のトランジスタは、ゲートが走査

線に電気的に接続され、ソースまたはドレインの一方が信号線に電気的に接続され、ソー

スまたはドレインの他方が前記第2のトランジスタのゲートに電気的に接続され、前記第

2のトランジスタは、ソースまたはドレインの一方が電源線に電気的に接続され、ソース

またはドレインの他方が前記一対の電極の一方に電気的に接続され、前記第1のトランジ

スタは、水素濃度が5×1019/cm3以下である酸化物半導体層を有する。そして、

前記表示装置が静止画像を表示する期間の間に、前記画素部に含まれる全ての走査線に供

給される信号の出力が停止される期間を有する。

(もっと読む)

電子デバイスの製造方法

【課題】転写歩留まりを向上することが可能な電子デバイスの製造方法を提供することを目的とする。

【解決手段】薄膜トランジスタ(TFT)19の製造方法において、スタンプ5の半導体膜8および絶縁膜9が形成される側の面とは反対側の面5aにガスバリア層7が形成されている。そのため、ガスバリア層7側からスタンプ5を空気で加圧する際に、スタンプ5の半導体膜8および絶縁膜9が形成される側の面とは反対側の面5aから、半導体膜8および絶縁膜9が形成される面に、加圧した空気が抜けにくくなる。これにより、スタンプ5を基板1に押し付けることを持続することができるので、スタンプ5に形成された半導体膜8および絶縁膜9と基板1との密着性を増すことができる。したがって、基板1に転写されない半導体膜8および絶縁膜9が減少し、薄膜転写の歩留まりを向上させることができる。

(もっと読む)

半導体装置

【課題】半導体チップが薄くなっても、応力による特性変化の少ない半導体装置を提供する。

【解決手段】SOI活性層のオリフラ方向の面方位を<100>、半導体支持基板の面方位を<110>とし、SOI活性層にはPチャネルMOSトランジスタ、半導体支持基板にはNチャネルMOSトランジスタを形成することで、NチャネルMOSトランジスタとPチャネルMOSトランジスタのどちらもピエゾ抵抗効果の角度度依存を持たないように配置することが可能となり、結果としてペアトランジスタ間のシフト量がそろい、半導体装置の特性が安定することとなる。

(もっと読む)

半導体装置及びその製造方法

【課題】通電領域表面の周辺の強電界の影響がナノワイヤに及び難くして、ホットキャリアの生成やオフリーク電流を低減する。半導体装置を高性能化する。

【解決手段】基板の表面よりも深い位置に配置され互いに対向する2つの側壁を有する導電膜と、導電膜の2つの側壁の側方に形成され互いに同じ導電型の半導体領域である第1及び第2の通電領域と、導電膜を貫通して2つの半導体領域どうしを接続し第1及び第2の通電領域の導電型とは逆導電型の半導体領域であるナノワイヤと、導電膜と前記ナノワイヤとの境界部に形成された絶縁膜と、を有することを特徴とする半導体装置。

(もっと読む)

液晶表示装置

【課題】オフリーク電流を抑制することが可能な液晶表示装置を提供する。

【解決手段】本発明の液晶表示装置では、半導体層53は、平面視においてゲート電極51の範囲内に配置される。ソース電極55及びドレイン電極57は、平面視において半導体層53の範囲内に配置される。シールド7は、保護絶縁膜4上に配置され、画素電極6と同一の材料からなり、画素電極6と電気的に接続されていない。

(もっと読む)

装置の作製方法

【課題】樹脂基板等の可撓性を有する基板を用いて、柔軟性を有する表示装置を作製する

ための技術を提供する。

【解決手段】固定基板上に、剥離層となる非晶質シリコン膜を介して樹脂基板を形成する

工程と、前記樹脂基板上に少なくともTFT素子を形成する工程と、前記非晶質シリコン

膜にレーザー光を照射することにより、前記非晶質シリコン膜において前記固定基板から

前記樹脂基板を剥離する工程とを行い、前記樹脂基板を用いた柔軟性を有する表示装置を

作製する。

(もっと読む)

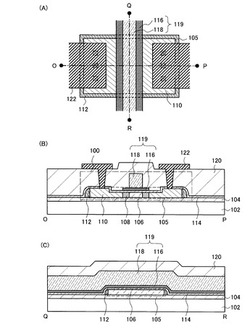

半導体装置の製造方法及びプラズマドーピング装置

【課題】フィン型半導体領域の側面に不純物を導入して低抵抗の不純物領域を形成できるようにし、それによって、所望の特性を持つフィン型半導体装置を実現する。

【解決手段】基板11上にフィン型半導体領域13を形成した後、不純物含有ガスと酸素含有ガスとを用いて、フィン型半導体領域13に対してプラズマドーピングを行うことによって、フィン型半導体領域13の少なくとも側部に不純物導入領域27Bを形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】ショットキー障壁の高さおよび幅を容易に制御すると共に寄生抵抗が低く、且つ短チャネル効果を効果的に抑制する。

【解決手段】金属ソース・ドレイン電極(ニッケルシリサイド)6とP型シリコン基板1との間に、セシウム含有領域5を形成している。こうして、金属ソース・ドレイン電極6近傍のセシウムをイオン化して正孔に対するエネルギー障壁高さを大きくし、金属ソース・ドレイン電極6とP型シリコン基板1との間のリーク電流を著しく低減する。また、チャネルと金属ソース・ドレイン電極6との間のショットキー障壁の高さおよび幅を実効的に小さくして寄生抵抗を著しく低減する。したがって、金属シリサイドの厚み(深さ)をイオン注入による制約なしに決定でき、極めて浅いソース・ドレインを形成して良好な短チャネル効果特性を得ることができる。

(もっと読む)

微結晶シリコン膜形成方法、微結晶シリコン膜成膜装置および表示装置

【課題】微結晶シリコン膜の移動度を高める。

【解決手段】高密度プラズマを用いて少なくとも(220)の結晶方位配列に成長させるように微結晶シリコン膜を形成する第1の工程を有し、第1の工程時、微結晶シリコン膜の結晶方位配列(111)に対する結晶方位配列(220)への成長比率が高くなるように、被処理体近傍の温度を300〜350℃の範囲内に設定し、総流量に対する水素ガスの流量比を高めた成膜ガスを供給する。これにより、ダングリングボンドの少ない微結晶シリコン膜20を形成して、移動度を高めることができる。

(もっと読む)

半導体装置の作製方法

【課題】複数のトランジスタが高集積化された素子の少なくとも一のトランジスタに、作製工程数を増加させることなくバックゲートを設ける半導体装置を提供する。

【解決手段】複数のトランジスタが上下に積層されて設けられた素子において、少なくとも上部のトランジスタ102は、半導体特性を示す金属酸化物により設けられ、下部のトランジスタ100が有するゲート電極層を上部のトランジスタのチャネル形成領域と重畳するように配して、ゲート電極層と同一の層の一部を上部のトランジスタ102のバックゲートBGとして機能させる。下部のトランジスタ100は、絶縁層で覆われた状態で平坦化処理が施され、ゲート電極が露出され、上部のトランジスタ102のソース電極及びドレイン電極となる層に接続されている。

(もっと読む)

半導体装置の製造方法

【課題】SOI基板を使用せずバルク基板を用いてフィン型FETを製造すると、従来技術では素子領域と半導体基板との間の絶縁耐圧が低くなっていた。

【解決手段】本発明の半導体装置の製造方法では、素子分離膜の形成時にマスクとして用いる耐酸化用膜を、半導体基板表面に設ける溝部の底部から所定の距離まで離間した部分を除いて立設部の表面に形成することで、立設部の下部の素子分離膜がほぼ一定の膜厚にすることができた。このため、立設部と半導体基板との間の絶縁耐圧が向上し、リークもなく、信頼性が向上した。

(もっと読む)

液晶表示装置

【課題】部材を新たに追加することなく、偏光サングラスを装着したままランドスケープ、ポートレートともに表示が観察可能な表示品位の優れたFFSモードの液晶表示装置を提供すること。

【解決手段】本発明に係る液晶表示装置は、ゲート配線43の延在方向に対して0°<α<90°の角度αで傾斜した配向方向を有する配向膜と、画素電極6と、画素電極6上に絶縁膜を介して対向配置される共通電極8と、共通電極8に形成され、画素電極6との間で液晶20にフリンジ電界を発生させるスリットとを備える。画素内は、配向方向に延在する境界線により分割され、スリットは、各領域において境界線の延在する方向に対して角度±θ傾斜して配置された複数の第1スリットA、第2スリットBと、境界線上に形成され、該境界線に沿う方向に延在する端辺を有する第3スリットCを有し、第2の基板には配向方向に設定された吸収軸を有する偏光板を有する。

(もっと読む)

薄膜トランジスタ、その製造方法及びこれを含む有機発光ダイオード表示装置

【課題】薄膜トランジスタ、その製造方法及びこれを含む有機発光ダイオード表示装置を提供する。

【解決手段】基板と、前記基板上に位置し、結晶化誘起金属を用いて結晶化された多結晶シリコン層からなり、ソース/ドレイン領域及びチャネル領域を含む半導体層と、前記半導体層上に位置するゲート絶縁膜と、前記ゲート絶縁膜上に位置するゲート電極と、前記ゲート電極上に位置する層間絶縁膜と、前記層間絶縁膜上に位置し、前記半導体層のソース/ドレイン領域と電気的に接続されるソース/ドレイン電極を含み、前記半導体層は前記半導体層の両端部に位置する第1ゲッタリングサイト及び前記第1ゲッタリングサイトと離隔されて前記半導体層のドレイン領域のみに位置する第2ゲッタリングサイトを含むことを特徴とする薄膜トランジスタ、その製造方法及びこれを含む有機発光ダイオード表示装置を提供する。

(もっと読む)

半導体装置

【課題】ノーマリーオフのスイッチング素子を実現するトランジスタ構造およびその作製方法を提供する。トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する構成およびその作製方法を提供する。信頼性の高い半導体装置を提供する。

【解決手段】半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてインジウム、ガリウム、亜鉛、及び酸素の4元素を少なくとも含み、該4元素の組成比を原子百分率で表したとき、インジウムの割合が、ガリウムの割合及び亜鉛の割合の2倍以上である酸化物半導体層を用いる。

(もっと読む)

液晶表示装置

【課題】TFTの工程を複雑化させることなくシステムオンパネル化を実現し、なおかつコストを抑えることができる液晶表示装置の提案を課題とする。

【解決手段】画素部に液晶素子と、液晶素子に印加される電圧を制御するTFTとを有する画素が設けられており、駆動回路が有するTFTと、液晶素子に印加される電圧を制御するTFTとは、ゲート電極とゲート電極上に形成されたゲート絶縁膜と、ゲート絶縁膜を間に挟んでゲート電極と重なっている第1の半導体膜と、第1の半導体膜上に形成された一対の第2の半導体膜とを有し、一対の第2の半導体膜には一導電型を付与する不純物が添加されており、第1の半導体膜はセミアモルファス半導体で形成されていることを特徴とする液晶表示装置。

(もっと読む)

半導体装置およびその製造方法

【課題】仕事関数の異なる複数の電極層を有し、ゲート抵抗が低く、作製が容易なゲート電極を備える半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置は、基板と、前記基板上に形成されたゲート絶縁膜とを備える。さらに、前記装置は、前記ゲート絶縁膜の上面に形成され、第1の仕事関数を有する第1の電極層と、前記ゲート絶縁膜の上面と前記第1の電極層の上面に連続して形成され、前記第1の仕事関数と異なる第2の仕事関数を有する第2の電極層と、を有するゲート電極と、前記ゲート電極の側面に形成された側壁絶縁膜とを備える。さらに、前記装置では、前記第1の電極層の上面の高さは、前記側壁絶縁膜の上面の高さよりも低い。

(もっと読む)

誘電体分離基板および半導体装置

【課題】深い不純物拡散層の形成が容易な誘電体分離基板および半導体装置を提供する。

【解決手段】誘電体分離基板10では、半導体基板11に第1の厚さt1を有する絶縁膜12が設けられている。絶縁膜12上に第2の厚さt2を有する第1導電型の半導体層13が設けられている。半導体層13の下部に絶縁膜12に接して第2導電型の不純物拡散層14が部分的に設けられている。

(もっと読む)

三次元集積回路を作製する方法

【課題】集積回路を作製する新規なタイプの方法を提供する。

【解決手段】少なくとも第3の層がその間に配置された、少なくとも半導体の第1および第2の層を備える基板を作製するステップと、少なくとも第1のMOSデバイスを作製するステップであって、その活性領域が半導体の第1の層の少なくとも一部に形成される、ステップと、少なくとも第2のMOSデバイスを作製するステップであって、その活性領域が半導体の第2の層の少なくとも一部に形成され、第2のMOSデバイスの活性領域が第2のMOSデバイスのゲートと第1のMOSデバイスの活性領域との間に配置される、ステップとを少なくとも含む、集積電子回路を作製する方法。

(もっと読む)

半導体装置

【課題】小面積、低電力動作、高速動作を並立する論理ゲートを含む半導体装置の構成を提供する。

【解決手段】本発明に係る半導体装置は、基板上にゲート絶縁膜を介してゲート電極と半導体層が配置され、半導体層に接続してソース電極とドレイン電極とが配置される薄膜トランジスタを2つ以上含む論理ゲートで構成される。少なくとも第一の薄膜トランジスタは、そのゲート電極が電気的に浮遊状態にあり、かつ、その半導体層は基板面に対して垂直方向について、ゲート電極とソース電極により挟まれる第1の重なり領域とゲート電極とドレイン電極により挟まれる第2の重なり領域を有する。また、少なくとも第二の薄膜トランジスタは、そのゲート電極が入力端子に接続され、かつ、そのチャネル層は基板面に対して垂直方向について、ゲート電極とソース電極により挟まれる第1の重なり領域とゲート電極とドレイン電極により挟まれる第2の重なり領域を有する。

(もっと読む)

121 - 140 / 7,158

[ Back to top ]