Fターム[5F110HL08]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−コンタクトホール介在 (16,138) | 材料 (10,537) | 半導体 (328)

Fターム[5F110HL08]に分類される特許

21 - 40 / 328

半導体装置

【課題】可撓性を有する基板上に有機化合物を含む層を有する素子が設けられた半導体装

置を歩留まり高く作製することを課題とする。

【解決手段】基板上に剥離層を形成し、剥離層上に、無機化合物層、第1の導電層、及び

有機化合物を含む層を形成し、有機化合物を含む層及び無機化合物層に接する第2の導電

層を形成して素子形成層を形成し、第2の導電層上に第1の可撓性を有する基板を貼りあ

わせた後、剥離層と素子形成層とを剥す半導体装置の作製方法である。

(もっと読む)

半導体装置

【課題】ソース電極およびドレイン電極間におけるオフリーク電流の低減を課題とする。

【解決手段】本発明の一態様は、ゲート電極101と、前記ゲート電極を覆うように形成されたゲート絶縁膜102と、前記ゲート絶縁膜上に形成され、前記ゲート電極の上方に位置する半導体層104と、前記半導体層上に形成された第2の絶縁膜108aと、前記第2の絶縁膜の上面と側面、前記半導体層の側面および前記ゲート絶縁膜の上に形成された第1の絶縁膜108bと、前記第1の絶縁膜上に形成され、前記半導体層と電気的に接続されたシリコン層105,106と、前記シリコン層上に形成されたソース電極107aおよびドレイン電極107bと、を有する薄膜トランジスタを具備し、前記ソース電極と前記ドレイン電極は、前記第1の絶縁膜上で互いに電気的に分離されており、前記半導体層は、前記ソース電極および前記ドレイン電極それぞれと接しない半導体装置である。

(もっと読む)

配線構造、表示装置、および半導体装置

【課題】Cu合金層と半導体層との間に通常設けられるバリアメタル層を省略しても優れた低接触抵抗を発揮し得、さらに半導体層との密着性に優れており、且つ電気抵抗率が低減された配線構造を提供すること。

【解決手段】本発明の配線構造は、基板の上に、基板側から順に、半導体層と、Cu合金層とを備えた配線構造であって、前記Cu合金層は、基板側から順に、合金成分としてMnと、X(Xは、Ag、Au、C、W、Ca、Mg、Al、SnおよびNiよりなる群から選択される少なくとも一種)を含有する第一層と、純Cu、またはCuを主成分とするCu合金であって前記第一層よりも電気抵抗率の低いCu合金からなる第二層、とを含む積層構造である。

(もっと読む)

電気光学装置の製造方法

【課題】テトラエトキシシラン等のシラン系有機材料を用いたプラズマCVD法によりシリケートガラスを形成した場合でも、シリケートガラスから半導体層へのフッ素の侵入を防止することのできる電気光学装置の製造方法を提供すること。

【解決手段】液晶装置の製造方法において、ゲート電極3cの形成工程、低濃度不純物導入工程、および高濃度不純物導入工程を行った後、シランガス等のシラン系無機原料を用いたCVD法により第1絶縁膜411を形成する。次に、第1アニール工程において第1絶縁膜411をアニールした後、テトラエトキシシラン等のシラン系有機原料を用いたプラズマCVD法によりシリケートガラスからなる第2絶縁膜412を形成する。

(もっと読む)

半導体装置

【課題】微細化による電気特性の変動が生じにくい半導体装置を提供する。

【解決手段】第1の領域と、第1の領域を介して対向する一対の第2の領域と、を含む酸化物半導体膜と、酸化物半導体膜上に設けられるゲート絶縁膜と、ゲート絶縁膜上に設けられて、かつ第1の領域に重畳する第1の電極と、を有し、第1の領域は、c軸配向した結晶部を有する非単結晶の酸化物半導体領域であり、一対の第2の領域は、ドーパントを含んで、かつ複数の結晶部を有する酸化物半導体領域であることを特徴とする半導体装置である。

(もっと読む)

半導体装置の作製方法

【課題】しきい値電圧変動が少なく信頼性の高い半導体装置の作製方法を提供することを課題とする。

【解決手段】酸化物半導体層に接して、加熱により酸素の放出が可能な絶縁膜を形成し、ゲート電極又はゲート電極と重なる領域に形成された金属層に光照射を行うことで、ゲート電極と重なる領域の酸化物半導体層中に酸素を添加する。これによりゲート電極と重なる領域の酸化物半導体層中に存在する酸素欠損や界面準位を低減することで、課題を達成できる。

(もっと読む)

液晶表示装置、電子機器

【課題】IPSにおける従来の技術は、工程数が多く、開口率が低いので、実用化できな

い。また、液晶層に最も近接している層に存在する配線及び電極が多く、画素表示部にお

ける個々の液晶にかかる電界が不均一であった。

【解決手段】本発明は、ゲイト線102、105とコモン線103、104を最初に同時

に形成し、層間膜形成後、画素電極108とコモン電極110、111とソ─ス線106

、107を同時に形成する。こうすることによって、電極パタ─ンを単純化でき、工程を

簡略化した。また、液晶層に最も近接している層に存在する配線及び電極を画素電極とコ

モン電極とソ─ス線とし、その形状を単純なものにした。

(もっと読む)

電気光学装置の製造方法

【課題】新たなパラメーターによって半導体層内における不純物分布を制御して電界効果

型トランジスターを形成することのできる電気光学装置の製造方法を提供すること。

【解決手段】LDD構造の電界効果型トランジスターからなる画素トランジスターを基板

本体10wの一方面10sに形成するにあたって、一方面10s側の半導体層1aに不純

物を導入する不純物導入工程を行う。その後、不純物拡散工程において、一方面10s側

にレーザーアニール装置、ヒートガスアニール装置、ランプアニール装置等の加熱装置9

20を配置し、一方面10s側を他方面10t側より温度を高くした状態で半導体層1a

を加熱する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の構成材料の特性劣化を抑制しつつ、基板とゲート絶縁膜との界面の界面準位密度を効率的に低減することが可能な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法では、基板100上に、ゲート絶縁膜102とゲート電極103とを含むトランジスタを形成する。さらに、基板100上に1層の配線層110を形成する処理と、1層の配線層110を配線パターンに加工する処理を1回以上行うことにより、基板100上に、1層以上の配線層113,115を含む配線構造を形成する。さらに、基板100上に、1層以上の配線層113,115のうちの少なくとも1層の配線層110が配線パターンに加工された後に、基板100上にマイクロ波を照射して基板100のアニールを行う。

(もっと読む)

SOI基板の作製方法

【課題】照射された水素イオンの単結晶半導体基板からの脱離を抑制する。

【解決手段】半導体基板中に炭素イオンを照射し、当該炭素イオンが照射された半導体基板中に、水素イオンを照射することにより、当該半導体基板中に脆化領域を形成し、当該半導体基板の表面及びベース基板の表面を対向させ、接触させることにより、当該半導体基板及び当該ベース基板を貼り合わせ、貼り合わせた当該半導体基板及び当該ベース基板を加熱し、当該脆化領域において分離させることにより、当該ベース基板上に半導体層を形成するSOI基板の作製に関する。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】高速動作可能な半導体装置を提供する。また、短チャネル効果による電気特性の変動が生じにくい半導体装置を提供する。

【解決手段】トランジスタの半導体層に結晶性を有する酸化物半導体を用い、該半導体層にチャネル形成領域とソース領域とドレイン領域を形成する。ソース領域及びドレイン領域は、ゲート電極をマスクとして、半導体層に第15族元素のうち一種類または複数種類の元素を添加する自己整合プロセスにより形成する。ソース領域及びドレイン領域に、ウルツ鉱型の結晶構造を付与することができる。

(もっと読む)

非平面形状ディスプレイ及びその製造方法

【課題】製造コストの増大を抑制することが可能な非平面形状ディスプレイ及びその製造方法を提供することを目的とする。

【解決手段】 非ガラス素材によって形成された非平面形状の絶縁基板、前記絶縁基板に接着された下地絶縁層、前記下地絶縁層上に形成されたスイッチング素子、及び、前記スイッチング素子に接続された画素電極を備えたアレイ基板と、非ガラス素材によって形成され、前記アレイ基板に貼り合わせられた対向基板と、を備えたことを特徴とする非平面形状ディスプレイ及びその製造方法。

(もっと読む)

薄膜トランジスターの製造方法、及び電気光学装置

【課題】所期の特性が得られ高品位な表示を得ることができる薄膜トランジスターの製造方法、及び電気光学装置を提供する。

【解決手段】薄膜トランジスターとしてのTFT素子の製造方法は、第1基板12上に半導体膜38を形成する工程と、半導体膜38上にゲート絶縁膜53を形成する工程と、ゲート絶縁膜53上にゲート電極35aを形成する工程と、ゲート絶縁膜53及びゲート電極35aを覆って、半導体膜38に注入する不純物72の量を調整するための、ゲート絶縁膜53とエッチングの選択比が異なる調整膜73を形成する工程と、調整膜73を介して半導体膜38に不純物72を注入する工程と、半導体膜38にアニール処理を施す工程と、を有する。

(もっと読む)

電気光学装置、投射型表示装置、電気光学装置の製造方法

【課題】画素電極表面でのヒロックの発生や、平坦化絶縁膜において凹部を埋める部分での空洞の発生を防止することのできる電気光学装置、該電気光学装置を用いた投射型表示装置、および当該電気光学装置の製造方法を提供すること。

【課題手段】電気光学装置100の素子基板10において、反射性の画素電極9aの上層側に設けられた平坦化絶縁膜17は、画素電極9a上に積層された層がドープトシリコン酸化膜170からなる。ドープトシリコン酸化膜170の熱膨張係数は、画素電極9aを構成するアルミニウム膜の熱膨張係数との差が小さい。このため、加熱した状態で平坦化絶縁膜17を成膜しても、画素電極9aおよび平坦化絶縁膜17に大きな熱応力が発生しないので、画素電極9aの表面にヒロック等の欠陥が発生しにくい。また、ドープトシリコン酸化膜170は、段差被覆性に優れている。

(もっと読む)

トランジスタの作製方法

【課題】特性のバラツキが少なく、電気特性が良好なトランジスタを作製する。

【解決手段】ゲート電極上にゲート絶縁膜を形成し、ゲート絶縁膜上に微結晶半導体を含む半導体層を形成し、半導体層上に不純物半導体層を形成し、不純物半導体層上にマスクを形成した後、マスクを用いて半導体層及び不純物半導体層をエッチングして、半導体積層体を形成し、マスクを除去した後に半導体積層体を希ガスを含む雰囲気で発生させたプラズマに曝して半導体積層体の側面に障壁領域を形成し、半導体積層体の不純物半導体層に接する配線を形成する。

(もっと読む)

トランジスタ、発光装置、及び、電子機器

【課題】トランジスタ外部からの光による悪影響を軽減又は防止したトランジスタ、発光装置、及び、電子機器を提供する。

【解決手段】トランジスタTrは、ゲート電極12と、透光性を有する絶縁層を介してゲート電極12と対向配置される、ゲート電極12側の面に光の反射面を有する導電体層22と、ゲート電極12と導電体層22との間に位置し、チャネルが形成される半導体層14と、を備える。光を吸収する光吸収層21は、導電体層22と半導体層14との間、並びにゲート電極12と半導体層14との間の少なくともいずれか一方に位置する。

(もっと読む)

半導体装置の作製方法

【課題】簡単な工程で絶縁膜、半導体膜、導電膜等の膜パターンを有する基板を作製する方法、さらには、低コストで、スループットや歩留まりの高い半導体装置の作製方法を提供することを目的とする。

【解決手段】基板上に形成された絶縁膜、半導体膜又は導電膜上に接して第1の膜を形成する工程と、第1の膜上に第1のマスク材料を含有する溶液を吐出して第1の膜上に第1のマスクを形成する工程と、第1のマスクを用いて第1の膜をパターニングして絶縁膜、半導体膜又は導電膜表面上に塗れ性の低い領域と塗れ性の高い領域を形成する工程と、第1のマスクを除去する工程と、塗れ性の低い領域に挟まれた塗れ性の高い領域に、第2のマスク材料を含有する溶液を吐出して第2のマスクを形成する工程と、第2のマスクを用いて、パターニングされた第1の膜をエッチングするとともに絶縁膜、半導体膜又は導電膜をエッチングする。

(もっと読む)

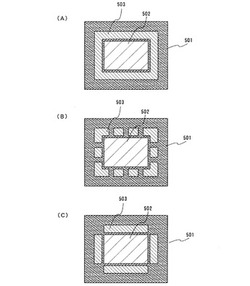

トランジスタ構造体、トランジスタ構造体の製造方法及び発光装置

【課題】トランジスタ特性が変化しにくい薄膜トランジスタを容易に作り分けること。

【解決手段】ボトムゲート構造の第1薄膜トランジスタである駆動トランジスタ6と、トップゲート構造の第2薄膜トランジスタであるスイッチトランジスタ5とを形成する際、駆動トランジスタ6の第1ゲート電極6aとスイッチトランジスタ5の第2遮光膜5eを形成する工程と、スイッチトランジスタ5の第2ゲート電極5aと駆動トランジスタ6の第1遮光膜6eを形成する工程を別工程にし、それ以外の薄膜トランジスタの構成を共通の工程によって形成する。こうして、ゲート電極(6a、5a)と遮光膜(6e、5e)を形成する以外の工程を共通の製造工程とする製造方法によって、駆動トランジスタ6とスイッチトランジスタ5を作り分けることを可能にした。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】第1のトランジスタ160と、第2のトランジスタ162と、第1のトランジスタ160のソース領域またはドレイン領域120と、第2のトランジスタ162のチャネル形成領域144との間に設けられた絶縁層128と、を含むメモリセルを有し、第1のトランジスタ160と、第2のトランジスタ162とは、少なくとも一部が重畳して設けられる半導体装置である。また、絶縁層128と第2のトランジスタのゲート絶縁層146は、式((ta/tb)×(εrb/εra)<0.1)を満たす。(但し、式中、taはゲート絶縁層146の膜厚を示し、tbは絶縁層128の膜厚を示し、εraはゲート絶縁層146の誘電率を示し、εrbは絶縁層128の誘電率を示す。)

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】第1のトランジスタと第2のトランジスタを有し、第1のトランジスタと第2のトランジスタとは少なくとも一部が重畳する第1のメモリセルと、第3のトランジスタと第4のトランジスタを有し、第3のトランジスタと第4のトランジスタとは少なくとも一部が重畳する第2のメモリセルと、駆動回路と、を有し、第2のメモリセルは、第1のメモリセル上に設けられ、第1のトランジスタは、第1の半導体材料を含んで構成され、第2のトランジスタ、第3のトランジスタ、および第4のトランジスタ、は、第2の半導体材料を含んで構成される半導体装置である。

(もっと読む)

21 - 40 / 328

[ Back to top ]