Fターム[5F110NN14]の内容

薄膜トランジスタ (412,022) | その他の構成要素 (47,691) | 保護膜(パッシベーション膜) (34,477) | 島状のチャネル保護膜 (1,301) | 膜厚が規定 (220)

Fターム[5F110NN14]に分類される特許

81 - 100 / 220

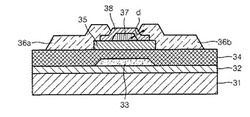

薄膜トランジスタ及びその製造方法

【課題】キャリアの移動を円滑にした薄膜トランジスタ及びその製造方法を提供する。

【解決手段】基板31の上に酸化膜32を介して形成されたゲート33と、ゲート33の上にゲート絶縁層34を介して形成されたチャネル35と、チャネル35表面にソース36a及びドレイン36bと離隔して形成され、キャリアの移動を円滑にするフローティングチャネル37と、を備えることができ、フローティングチャネル37上にソース36aまたはドレイン36bとの間隔を制御するための絶縁層38をさらに備えることができる薄膜トランジスタ。

(もっと読む)

表示装置及び電子機器

【課題】表示装置に置いて、多階調表示を実現することを目的とする。

【解決手段】トランジスタ及び表示素子を有する画素がマトリクス状に配置された画素部と、前記トランジスタのゲートに電気的に接続されたゲートドライバと、前記トランジスタのソース又はドレインに電気的に接続されたソースドライバと、前記ソースドライバに信号を出力するデータ処理回路とを有し、前記トランジスタは、酸化物半導体を用いており、前記データ処理回路は、入力されるmビットのデジタルデータのうち、nビットのデジタルデータ(m、nは共に正の整数、かつm>n)を電圧階調に用い、(m−n)ビットのデジタルデータを時間階調に用いる表示装置である。

(もっと読む)

トランジスタの駆動方法及び該方法で駆動されるトランジスタを含む装置

【課題】AOS−TFTの課題として、電気的ストレスによる特性変化、主に閾値電圧の変化がある。

【解決手段】半導体層と、絶縁層1と、絶縁層2と、導電層1と、導電層2と、を有し、半導体層は絶縁層1と絶縁層2とに挟まれ、絶縁層1は半導体層と接する面とは反対側の面で導電層1と接し、絶縁層2は半導体層と接する面とは反対側の面で導電層2と接するトランジスタの駆動方法であって、導電層2に、VBG<Von1×C1/(C1+C2)を満たす電圧VBGを印加することを特徴とするトランジスタの駆動方法。但し、C1:絶縁層1の単位面積当たりの容量、C2:絶縁層2の単位面積当たりの容量、VON1:ソース電圧を基準電圧とし、かつ導電層2にかかる電圧を0Vにしたときのドレイン電流の立ち上がり電圧である。

(もっと読む)

表示装置、及び表示装置を有する電子機器

【課題】消費電力が抑制された表示装置を提供することを課題の一とする。また、消費電力が抑制された自発光型の表示装置を提供することを課題の一とする。また、暗所でも長時間の利用が可能な、消費電力が抑制された自発光型の表示装置を提供することを課題の一とする。

【解決手段】高純度化された酸化物半導体を用いた薄膜トランジスタで回路を構成し、画素が一定の状態(映像信号が書き込まれた状態)を保持することを可能とする。その結果、静止画を表示する場合にも安定した動作が容易になる。また、駆動回路の動作間隔を長くできるため、表示装置の消費電力を低減できる。また、自発光型の表示装置の画素部に蓄光材料を適用し、発光素子の光を蓄えれば、暗所でも長時間の利用が可能になる。

(もっと読む)

表示装置、及び当該表示装置を具備する電子機器

【課題】消費電力が抑制された表示装置を提供する。

【解決手段】第1のトランジスタ、第2のトランジスタ、及び一対の電極を有する発光素子を含む画素が複数設けられた画素部を有し、前記第1のトランジスタは、ゲートが走査線に電気的に接続され、ソースまたはドレインの一方が信号線に電気的に接続され、ソースまたはドレインの他方が前記第2のトランジスタのゲートに電気的に接続され、前記第2のトランジスタは、ソースまたはドレインの一方が電源線に電気的に接続され、ソースまたはドレインの他方が前記一対の電極の一方に電気的に接続され、前記第1のトランジスタは、水素濃度が5×1019/cm3以下である酸化物半導体層を有する。そして、前記表示装置が静止画像を表示する期間の間に、前記画素部に含まれる全ての走査線に供給される信号の出力が停止される期間を有する。

(もっと読む)

液晶表示装置、及び当該液晶表示装置を具備する電子機器

【課題】低消費電力化できる液晶表示装置を提供することを課題の一とする。

【解決手段】表示部に複数の画素を有し、複数のフレーム期間で表示を行う液晶表示装置であって、フレーム期間は、書き込み期間及び保持期間を有し、書き込み期間において、複数の画素のそれぞれに、画像信号を入力した後、保持期間において、複数の画素が有するトランジスタをオフ状態にして、少なくとも30秒間、画像信号を保持させる。画素は、酸化物半導体層でなる半導体層を具備し、酸化物半導体層は、キャリア濃度が1×1014/cm3未満である。

(もっと読む)

直流変換回路及び電源回路

【課題】高い信頼性を有する直流変換回路を提供する。

【解決手段】流れる電流の変化に応じて起電力が発生する誘導素子と、ゲート、ソース、及びドレインを有し、オン状態又はオフ状態になることにより、誘導素子における起電力の発生を制御するトランジスタと、トランジスタがオフ状態のときに導通状態になる整流素子と、トランジスタのオン状態又はオフ状態を制御する制御回路と、を具備し、トランジスタは、チャネル形成層として水素濃度が5×1019atoms/cm3以下である酸化物半導体層を有する構成とする。

(もっと読む)

表示装置、及び当該表示装置を具備する電子機器

【課題】ブルー相を示す液晶材料を利用した表示装置において、消費電力の低い表示装置を提供する。

【解決手段】トランジスタを含む画素が設けられた画素部を有する第1の基板と、前記第1の基板と対向する第2の基板と、前記第1の基板及び前記第2の基板の間に配置された液晶層とを有し、前記液晶層は、ブルー相を示す液晶材料を有し、前記トランジスタは、ゲートが走査線に電気的に接続され、ソースまたはドレインの一方が信号線に電気的に接続され、ソースまたはドレインの他方が電極に電気的に接続され、前記トランジスタは、水素濃度が5×1019/cm3以下である酸化物半導体層を有する。

(もっと読む)

薄膜トランジスタ、表示装置および電子機器

【課題】キャリアの移動度を向上させることが可能な薄膜トランジスタ、ならびにそのような薄膜トランジスタを用いた表示装置および電子機器を提供する。

【解決手段】酸化物半導体層15を、チャネルを構成するキャリア走行層151と、キャリア供給層152とを含む多層膜により構成する。また、キャリア供給層152における伝導帯下端準位Ec2が、キャリア走行層151における伝導帯下端準位Ec1よりもエネルギー的に高くなるように設定する(Ec2>Ec1)。キャリア供給層152からキャリア走行層151へとキャリア(電子)が供給され、キャリア走行層151内におけるキャリア供給層152との界面近傍の領域に、電子を蓄積させることができる。これにより、従来と比べて電子に対する走行散乱が抑えられる。

(もっと読む)

変調回路及びそれを備えた半導体装置

【課題】変調回路の消費電力を低減する。

【解決手段】変調回路は、負荷と、スイッチとして機能するトランジスタとを有し、前記トランジスタは、水素濃度が5×1019/cm3以下である酸化物半導体層を有し、前記トランジスタのオフ電流は、1×10−13A以下である。または、変調回路は、負荷と、スイッチとして機能するトランジスタと、ダイオードとを有し、前記負荷、前記トランジスタ、及び前記ダイオードは、アンテナの両端間に直列に接続されており、前記トランジスタは、水素濃度が5×1019/cm3以下である酸化物半導体層を有し、前記トランジスタのオフ電流は、1×10−13A以下である。また、前記トランジスタのゲートに入力される信号により、当該トランジスタの導通・非導通が制御される。また、前記負荷は、抵抗、容量、または抵抗及び容量である。

(もっと読む)

スパッタリングターゲットおよびその製造方法、並びにトランジスタ

【課題】酸化物半導体膜を成膜する成膜技術を提供することを課題の一とする。

【解決手段】金属酸化物の焼結体を含み、その金属酸化物の焼結体の含有水素濃度が、たとえば、1×1016atoms/cm3未満と低いスパッタリングターゲットを用いて酸化物半導体膜を形成することで、H2Oに代表される水素原子を含む化合物、もしくは水素原子等の不純物の含有量が少ない酸化物半導体膜を成膜する。また、この酸化物半導体膜をトランジスタの活性層として適用する。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】安定した電気的特性を有する酸化物半導体を用いた半導体装置を提供することを目的の一つとする。

【解決手段】不対結合手に代表される欠陥を多く含む絶縁層を、酸素過剰な混合領域、又は酸素過剰な酸化物絶縁層を間に介して、酸化物半導体層上に形成し、酸化物半導体層に含まれる水素や水分(水素原子や、H2Oなど水素原子を含む化合物)などの不純物を、酸素過剰な混合領域、又は酸素過剰な酸化物絶縁層を通過させて欠陥を含む絶縁層に拡散させ、上記酸化物半導体層中の不純物濃度を低減する。

(もっと読む)

半導体装置およびその作製方法

【課題】同一基板上に画素部と駆動回路を形成する場合、対向電極が対向基板の全面に設けられていると、最適化した対向電極の電圧が駆動回路にも影響を与える恐れがある。

【解決手段】一対の基板間に液晶層を有し、一方の基板に画素電極と駆動回路を設け、もう一方の基板は対向基板であり、対向基板に電位の異なる2つの対向電極層を設け、一方の電極層は、液晶層を介して画素電極と重なり、もう一方の電極層は液晶層を介して駆動回路に重なる構成とする。駆動回路は、酸化物半導体層を用いる。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】off電流が低下している薄膜トランジスタを提供する。

【解決手段】基板1上に形成されたゲート電極2と、ゲート電極2を覆うように形成されたシリコン窒化膜3と、シリコン窒化膜3上に形成された微結晶シリコンからなる微結晶Si半導体層4と、微結晶Si半導体層4に接して形成されているソース電極5およびドレイン電極6とを備えており、微結晶Si半導体層4のゲート電極2と重畳する領域にチャネル領域11が形成されており、チャネル領域11の微結晶シリコンに対して水素プラズマ処理が施されている。

(もっと読む)

半導体膜の製造方法、薄膜トランジスタの製造方法および表示装置の製造方法

【課題】半導体薄膜の結晶の不均一性を緩和し、薄膜トランジスタの動作特性を向上させることが可能な半導体膜の製造方法を提供する。

【解決手段】

基板10上に非晶質シリコン膜15Aおよび光熱変換層16をこの順に形成する。光熱変換層16を介して非晶質シリコン膜15Aに第1ビームL1を照射することにより非晶質シリコン膜15Aに高温過熱領域11を形成する。同時に、第2ビームL2を照射することにより高温過熱領域11の走査方向の前後に低温過熱領域12(昇温領域12Aおよび徐冷領域12B)を形成する。非晶質シリコン15Aでは、第1レーザL1の照射により結晶成長が始まり、第2レーザL2の照射により昇温、徐冷されるため、非晶質シリコン15Aの結晶化が緩やかに進行し、結晶粒径の不均一性が緩和される。

(もっと読む)

アナログ回路及び半導体装置

【課題】酸化物半導体層を用いる薄膜トランジスタにおいて、信号検出感度が高く、ダイナミックレンジの広い半導体装置を得ることを課題の一つとする。

【解決手段】チャネル形成層としての機能を有し、水素濃度が5×1019(atoms/cm3)以下であり、電界が発生していない状態においては、実質的に絶縁体として機能する酸化物半導体を有する薄膜トランジスタを用いてアナログ回路を構成することで、信号検出感度が高く、ダイナミックレンジの広い半導体装置を得ることができる。

(もっと読む)

薄膜トランジスタ基板、その製造方法及び画像表示装置

【課題】InMZnO系半導体膜を有する薄膜トランジスタ基板のドレイン電流のON/OFF比を大きくすることができる薄膜トランジスタ基板の製造方法を提供する。

【解決手段】基板10上に、ゲート電極13、ゲート絶縁膜14、InMZnO(MはGa,Al,Feのうち少なくとも1種)系半導体膜15、ソース電極16s及びドレイン電極16dが形成された薄膜トランジスタ基板1の製造方法であって、所定パターンのInMZnO系半導体膜15を形成する工程と、InMZnO系半導体膜15を覆う少なくとも1種の金属元素を含む金属酸化物、金属窒化物、金属炭化物及び金属酸窒化物のいずれかからなる保護膜17を設ける工程と、保護膜17を覆うアルミニウム、チタン及びモリブデンのいずれかからなる金属膜18を設ける工程と、金属膜18を設けた後に熱処理する工程とを有する。

(もっと読む)

論理回路及び半導体装置

【課題】論理回路の誤作動を防止すること又は消費電力を低減すること。

【解決手段】論理回路は、チャネル形成領域が酸化物半導体によって構成された薄膜トランジスタと、該薄膜トランジスタがオフすることによって、一方の端子の電位が浮遊状態となる容量素子とを有する。当該酸化物半導体は、水素濃度が5×1019(atoms/cm3)以下であり、電界が発生していない状態においては、実質的に絶縁体として機能する。そのため、薄膜トランジスタのオフ電流を低減することができる。これにより、容量素子に蓄積された電荷の薄膜トランジスタを介したリークを抑制することができる。その結果、論理回路の誤動作を防止することができる。また、薄膜トランジスタのオフ電流を低減することにより、論理回路内に流れる無駄な電流を低減することができる。これにより、論理回路の消費電力を低減することができる。

(もっと読む)

論理回路及び半導体装置

【課題】トランジスタのリーク電流を低減し、論理回路の誤動作を抑制する。

【解決手段】チャネル形成層としての機能を有する酸化物半導体層を含み、チャネル幅1μmあたりのオフ電流が1×10−13A以下であるトランジスタを有し、入力信号として、第1の信号、第2の信号、及びクロック信号である第3の信号が入力され、入力された第1の信号乃至第3の信号に応じて電圧状態が設定された第4の信号及び第5の信号を出力信号として出力する構成とする。

(もっと読む)

半導体装置、表示装置及び電子機器

【課題】電気特性が良好で信頼性の高い薄膜トランジスタ及び当該薄膜トランジスタをスイッチング素子として用いた表示装置を提供することを課題とする。

【解決手段】チャネル形成領域に酸化物半導体を用いたチャネル保護型の薄膜トランジスタであって、加熱処理により脱水化または脱水素化された酸化物半導体層を活性層に用い、チャネル形成領域の表層部にはナノクリスタルで構成された結晶領域を有し、その他の部分は非晶質、または非晶質領域中に微結晶が点在した非晶質と微結晶の混合物で形成されている。この様な構成をした酸化物半導体層を用いることにより、表層部からの水分の再侵入や酸素の脱離によるN型化や寄生チャネル発生の抑制、及びソース電極及びドレイン電極との接触抵抗を下げることができる。

(もっと読む)

81 - 100 / 220

[ Back to top ]