Fターム[5F110NN14]の内容

薄膜トランジスタ (412,022) | その他の構成要素 (47,691) | 保護膜(パッシベーション膜) (34,477) | 島状のチャネル保護膜 (1,301) | 膜厚が規定 (220)

Fターム[5F110NN14]に分類される特許

121 - 140 / 220

半導体装置

【課題】半導体装置の表示領域と駆動回路に設けられたTFTの構造を機能に応じて適切なものとするとき、pチャネル型TFTにおいて、チャネル形成領域と、不純物領域との接合に欠陥が形成され、オフ電流が増加することを防止する。

【解決手段】表示領域に第1のnチャネル型TFTが配置され、駆動回路に第2のnチャネル型TFT及びpチャネル型TFTが配置された半導体装置であって、pチャネル型TFTはチャネル形成領域と、これに隣接した不純物領域を有し、不純物領域にはnチャネル型TFTのために添加された不純物元素を含ませない。そのために、pチャネル型TFTのチャネル長はnチャネル型TFTのチャネル長より短くなる。

(もっと読む)

薄膜トランジスタ及びその作製方法、表示装置及びその作製方法、並びに電子機器

【課題】光電流による影響が小さく、オンオフ比が高い薄膜トランジスタを提供する。

【解決手段】ボトムゲートボトムコンタクト型(コプラナ型)の薄膜トランジスタにおいて、チャネル形成領域をゲート電極と重畳させ、チャネル形成領域と、配線層と接触する第2の不純物半導体層と、の間に第1の不純物半導体層を設け、好ましくはチャネル形成領域となる半導体層と第1の不純物半導体層はゲート電極と重畳する領域で接し、第1の不純物半導体層と第2の不純物半導体層はゲート電極と重畳しない領域で接する。

(もっと読む)

トランジスタを有するトランジスタ基板及びトランジスタを有するトランジスタ基板の製造方法

【課題】微結晶シリコンをチャンネル領域として用い、コンタクト歩留まりを向上させ、良好な特性を備えるトランジスタを有するトランジスタ基板及びその製造方法を提供する。

【解決手段】トランジスタ100は、基板11と、ゲート電極112と、ゲート絶縁膜113と、第1の半導体層114と、第2の半導体層115と、ストッパ膜116と、オーミックコンタクト層117、118と、ドレイン電極119と、ソース電極120と、を備える。微結晶シリコンを用いた第1の半導体層114上に第2の半導体層115を積層させた上で、第1の半導体層114及び第2の半導体層115の側面でオーミックコンタクト層117、118とコンタクトを取ることにより、コンタクト歩留まりを向上させ、良好な特性を備えるトランジスタを有するトランジスタ基板及びその製造方法を提供することができる。

(もっと読む)

半導体装置

【課題】しきい値電圧の制御にチャネルドープ法を用いて行う場合、活性層に不純物を導入するため、必然的にこの不純物起因のバルク結晶欠陥や、半導体層と絶縁層の界面凖位を生じさせてしまう。この結果、TFT特性、特に電界効果型移動度を悪化させる原因となる。

【解決手段】基板上に形成された電極上に設けられた第1の絶縁層の応力と膜厚の積と、第1の絶縁層上に設けられた引張り応力を有する結晶質半導体膜からなる活性層の応力と膜厚の積と、活性層上に設けられた第2の絶縁層の応力と膜厚の積を適当な大きさに設定することでしきい値電圧を制御する。

(もっと読む)

薄膜トランジスタ及びその製造方法、並びに薄膜トランジスタアレイ基板及び表示装置

【課題】閾値電圧シフトが小さく、かつオン特性に優れた薄膜トランジスタ、及びその製造方法を提供する。

【解決手段】本発明に係る薄膜トランジスタの製造方法は、ゲート電極2、ゲート絶縁膜3、第1の半導体層10、オーミックコンタクト層として機能する第2の半導体層、ソース電極5及びドレイン電極6をこの順に形成する工程を備え、第1の半導体層10を形成する工程は、実質的にイントリンシックな微結晶シリコン層からなる微結晶層11を形成し、少なくともソース電極5、ドレイン電極6と対向配置される領域に、微結晶層11aの表面の結晶欠陥を低減するように、低濃度のP(リン)が添加された非晶質シリコン層からなる欠陥修復層12aを形成し、その後、実質的にイントリンシックな非晶質シリコン層からなる非晶質層13aを形成する。

(もっと読む)

フレキシブル半導体デバイスを高温で提供する方法およびそのフレキシブル半導体デバイス

いくつかの実施例は、半導体デバイスを提供する方法を含む。当該方法は、

(a)フレキシブル基板を提供する段階、(b)フレキシブル基板上に少なくとも1つの材料層を堆積させる段階であって、そのフレキシブル基板上の少なくとも1つの材料層の堆積は、少なくとも180℃の温度で生じる、段階、および(c)金属層とa−Si層との間に拡散バリアを提供する段階を含む。他の実施例も本願において開示される。  (もっと読む)

(もっと読む)

電界効果型トランジスタの製造方法、電界効果型トランジスタ、及び表示装置の製造方法

【課題】電界効果型トランジスタの製造工程の簡略化が図れる電界効果型トランジスタの製造方法、電界効果型トランジスタ、及び表示装置の製造方法を提供する。

【解決手段】本実施の形態のトップコンタクト型の電界効果型トランジスタ10の製造方法によれば、半導体層形成工程で形成した活性層18上に、防護層22を形成した後に、該防護層22上にフォトレジスト膜を形成して露光工程においてパターン状に露光する。そして、次の現像工程において、アルカリ性現像液を用いて、上記露光工程を経たフォトレジスト膜30を現像してレジストパターン30B’を形成すると共に、防護層22における該レジストパターン30B’から露出している領域22Aを除去して防護層22のエッチングを行なう。

(もっと読む)

有機電界効果トランジスタ

【課題】有機トランジスタの導電特性を改良し、高強度の電流を得られるようにする。

【構成】ソース電極6及びドレイン電極8間の半導体層10中に、導電性チャンネルに近接し、又は電気絶縁層20及び前記半導体層10に対して、ゲート電極22の反対側に位置する圧電層23を備え、該圧電層23は、前記ソース電極6及びドレイン電極8から、及び前記半導体層10から絶縁されている。

(もっと読む)

電子デバイスの製造方法

【課題】可撓性を有する電子デバイスを、素子の劣化を防いで簡易に且つ短時間で製造することができる電子デバイスの製造方法を提供する。

【解決手段】支持基板12上に、特定の刺激によって発泡する発泡材を含む剥離層14を形成する工程と、前記剥離層上に電子デバイスを構成する素子を含む構造体11を形成する工程と、前記剥離層に前記特定の刺激を加えることにより該剥離層に含まれる前記発泡材を発泡させ、該剥離層を介して前記構造体を前記支持基板から剥離させる工程と、を有する電子デバイス10の製造方法。好ましくは、発泡材として熱膨張性マイクロカプセル15を用いる。

(もっと読む)

金属酸化物半導体の製造方法、金属酸化物半導体及びこれを用いた半導体素子、薄膜トランジスタ

【課題】本発明の目的は、酸化物半導体を用いた薄膜トランジスタにおいて、酸化物半導体の、半導体特性(移動度、on/off、Vg(ON))を向上させ、ばらつきを低減させて、生産効率が向上した製造方法を提供することであり、また、この酸化物半導体を用いた半導体素子、薄膜トランジスタを提供することにある。

【解決手段】金属塩を含有する半導体前駆体層に加熱処理を行って金属酸化物半導体を形成する金属酸化物半導体の製造方法において、加熱時の昇温速度が1〜100℃/分であることを特徴とする金属酸化物半導体の製造方法。

(もっと読む)

薄膜トランジスタ及びその製造方法

【課題】ソース・ドレイン電極形成時の活性層へのダメージを抑制するとともに、製造工程の簡略化を図ることが可能な薄膜トランジスタ及びその製造方法を提供する。

【解決手段】導電層50をエッチングによってパターニングすることにより、活性層18に接触するソース電極20及びドレイン電極22を形成するとともに、ソース電極20とドレイン電極22を除いた部分にソース電極20及びドレイン電極22よりも厚みが薄い導電層を第1保護薄膜56として残存させる工程と、第1保護薄膜56を半導体又は絶縁体に化学変化させて第2保護薄膜24を得る工程と、を含む薄膜トランジスタの製造方法を採用する。

(もっと読む)

薄膜トランジスタ、その製造方法、半導体装置および表示装置

【課題】オン電流が大きく、かつ電気的特性のばらつきが小さな薄膜トランジスタおよびその製造方法を提供する。

【解決手段】周辺TFT110のチャネル層141を形成するシリコンの結晶粒径は、微結晶シリコンによって形成されているので、閾値電圧のばらつきをある程度抑えながら、オン電流を大きくすることができる。しかし、多結晶シリコンからなるチャネル層を有する周辺TFTと比べて、小さなオン電流しか流すことができない。そこで、周辺TFT110のゲート電極125と対向する窒化シリコン膜180の表面に、さらにゲート電極195を形成する。この結果、チャネル層341を流れるオン電流は、2つのゲート電極125、195によって制御されるので、オン電流の不足分を補うことができる。

(もっと読む)

薄膜トランジスタおよび表示装置

【課題】酸化物半導体層に酸素を供給しやすく、良好なトランジスタ特性を回復させることが可能な薄膜トランジスタおよびこれを備えた表示装置を提供する。

【解決手段】TFT20のソース電極25Sおよびドレイン電極25Dに、酸化物半導体層23を露出させる開口部27を設ける。TFT20形成後に酸素アニールをする際に、開口部27から、酸化物半導体層23に酸素を供給しやすくし、良好なトランジスタ特性を回復させる。また、ソース電極25Sおよびドレイン電極25Dを、酸化物半導体層23を露出させる溝により、チャネル幅方向に分割するようにしてもよい。あるいは、ソース電極25Sまたはドレイン電極25Dのチャネル保護層24に重なる辺に対向する辺に沿って、酸化物半導体層23がソース電極25Sまたはドレイン電極25Dの端から露出しているはみ出し領域を設けてもよい。

(もっと読む)

薄膜トランジスタおよび表示装置

【課題】酸化物半導体層を含む薄膜トランジスタにおいて、信頼性を向上させることが可能な薄膜トランジスタを提供する。

【解決手段】シリコン酸化膜またはシリコン酸窒化膜からなるゲート絶縁膜222を、酸化物半導体層23に対応する領域において、この酸化物半導体層23と接するように選択的に形成する。ゲート絶縁膜222と酸化物半導体層23との間で良好なデバイス界面が形成され、酸化物半導体層23での格子欠陥の形成を抑制することができる。また、シリコン窒化膜からなるゲート絶縁膜221上において、酸化物半導体層23の上面および側面とゲート絶縁膜222の側面とが、ソース・ドレイン電極25およびチャネル保護膜24によって覆われているようにする。酸化物半導体層23への水分等の混入が抑えられ、酸化物半導体層23での水分の吸着を抑制することができる。

(もっと読む)

薄膜トランジスタおよび表示装置

【課題】酸化物半導体層を含む薄膜トランジスタにおいて、信頼性を向上させることが可能な薄膜トランジスタを提供する。

【解決手段】ゲート絶縁膜22上において、酸化物半導体層23の上面および側面が、ソース・ドレイン電極25およびチャネル保護膜24によって覆われているようにする。これにより、酸化物半導体層23への水分等の混入が抑えられ、酸化物半導体層23での水分の吸着を抑制することができる。なお、ゲート絶縁膜221,222としては、水分等に対してバリア性の高い酸化アルミニウム膜やシリコン窒化膜層を用いるようにするのが好ましい。

(もっと読む)

薄膜トランジスタの製造方法

【課題】酸化物半導体薄膜、特に、前駆体から熱変換され形成される酸化物半導体薄膜を有する薄膜トランジスタの製造方法において、半導体特性の向上およびその安定性が向上した生産効率の高い薄膜トランジスタを提供する。

【解決手段】基体310上に、ゲート電極302、ゲート絶縁膜303、酸化物半導体薄膜306を有する薄膜トランジスタの製造方法において、ゲート絶縁膜303が大気圧プラズマ法により形成されることを特徴とする薄膜トランジスタの製造方法。

(もっと読む)

電界効果型トランジスタ、電界効果型トランジスタの製造方法及び半導体素子の製造方法

【課題】遮断周波数の高い電界効果型トランジスタを提供する。

【解決手段】酸化物を含む半導体層、及び半導体層の保護層を有し、前記半導体層の、下記A又はBに対するエッチングレートが、酸化ケイ素のエッチングレートの2分の1以下である、電界効果型トランジスタ。

A:10質量%の弗化水素酸を含むウェットエッチング液

B:15質量%の弗化アンモニウムを含むウェットエッチング液

(もっと読む)

薄膜トランジスタ及びその製造方法

【課題】ノーマリーオフのTFT特性を示す酸化物半導体膜を含む薄膜トランジスタ、及びその製造方法を提供する。

【解決手段】酸化インジウムと、酸化ランタン、酸化ネオジム、酸化サマリウム、酸化ユウロピウム、酸化ガドリニウム、酸化テルビウム、酸化ジスプロシウム、酸化ホルミウム、酸化エルビウム、酸化ツリウム及び酸化イッテリビウムからなる群から選ばれた1種又は2種以上の酸化物をM2O3としたときに、原子比M/(In+M)の値が、0.1以上0.4以下で含む酸化物半導体膜を含む薄膜トランジスタ。

(もっと読む)

TFT−LCDアレイ基板、及びその製造方法

【課題】TFT−LCDアレイ基板及びその製造方法に関する。

【解決手段】TFT−LCDアレイ基板の製造方法であって、基板にゲート金属層薄膜を堆積し、ゲート電極とゲート・ラインとのパターンが含まれたパターンを形成するステップ1と、前記ステップ1を完成した基板にゲート絶縁層薄膜と、半導体層薄膜と、TFTチャネル部分の半導体層がエッチングされることを防止する阻止層薄膜とを堆積し、ゲート絶縁層と、半導体層と、阻止層とのパターンが含まれたパターンを形成するステップ2と、前記ステップ2を完成した基板にオーミック接触層薄膜と、透明導電層薄膜と、ソース・ドレイン金属層薄膜と、パッシベーション層薄膜とを堆積し、オーミック接触層と、画素電極と、データ・ラインと、ソース電極と、ドレイン電極と、パッシベーション層とのパターンが含まれたパターンを形成するステップ3と、を備える。

(もっと読む)

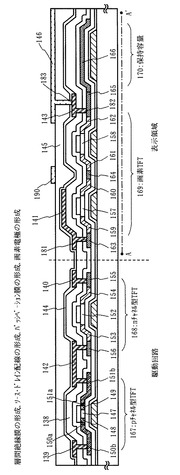

半導体装置およびその作製方法

【課題】表示装置の高精細化に伴い、画素数が増加し、ゲート線数、及び信号線数が増加する。ゲート線数、及び信号線数が増加すると、それらを駆動するための駆動回路を有するICチップをボンディング等により実装することが困難となり、製造コストが増大するという問題がある。

【解決手段】同一基板上に画素部と、画素部を駆動する駆動回路とを有し、駆動回路の少なくとも一部の回路を、上下をゲート電極で挟んだ酸化物半導体を用いた薄膜トランジスタで構成する。酸化物半導体とその上に設けられるゲート電極の間にはチャネル保護層を設ける。同一基板上に画素部及び駆動回路を設けることによって製造コストを低減する。

(もっと読む)

121 - 140 / 220

[ Back to top ]