Fターム[5F110NN14]の内容

薄膜トランジスタ (412,022) | その他の構成要素 (47,691) | 保護膜(パッシベーション膜) (34,477) | 島状のチャネル保護膜 (1,301) | 膜厚が規定 (220)

Fターム[5F110NN14]に分類される特許

21 - 40 / 220

表示装置およびその製造方法

【課題】活性層となる酸化物導電体層への光の入射を防ぎ、TFT特性の低下を抑制することが可能な表示装置およびその製造方法を提供する。

【解決手段】本技術の表示装置は、活性層が酸化物導電体よりなる薄膜トランジスタと、薄膜トランジスタ上に設けられた発光素子と、薄膜トランジスタおよび発光素子の各端面、並びに発光素子の上面の一部を覆う遮光膜とを備える。

(もっと読む)

半導体装置

【課題】良好な特性を維持しつつ、微細化を達成した、酸化物半導体を用いた半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と接するソース電極及びドレイン電極と、酸化物半導体層と重なるゲート電極と、酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、酸化物半導体層に接して設けられた絶縁層と、を有し、酸化物半導体層は、該酸化物半導体層の端面において、ソース電極またはドレイン電極と接し、且つ該酸化物半導体層の上面において、絶縁層を介して、ソース電極またはドレイン電極と重なる半導体装置である。

(もっと読む)

半導体装置の作製方法

【課題】配線間の寄生容量を十分に低減できる構成を備えた半導体装置を提供することを

課題の一とする。

【解決手段】金属薄膜の一部または全部を酸化させた第1の層と酸化物半導体層の積層を

用いるボトムゲート構造の薄膜トランジスタにおいて、ゲート電極層と重なる酸化物半導

体層の一部上に接するチャネル保護層となる酸化物絶縁層を形成し、その絶縁層の形成時

に酸化物半導体層の積層の周縁部(側面を含む)を覆う酸化物絶縁層を形成する。

(もっと読む)

半導体装置

【課題】半導体装置の開口率を向上することを課題の一とする。

【解決手段】同一基板上に駆動回路部と、表示部(画素部ともいう)とを有し、当該駆動回路部は、ソース電極及びドレイン電極が金属によって構成され且つチャネル層が酸化物半導体によって構成された駆動回路用チャネルエッチ型薄膜トランジスタと、金属によって構成された駆動回路用配線とを有し、当該表示部は、ソース電極層及びドレイン電極層が酸化物導電体によって構成され且つ半導体層が酸化物半導体によって構成された画素用チャネル保護型薄膜トランジスタと、酸化物導電体によって構成された表示部用配線とを有する半導体装置である。半導体装置に設けられる該薄膜トランジスタは多階調マスクによって形成されたレジストマスクを用いて作製する。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタパネル、及びこれらを製造する方法

【課題】薄膜トランジスタ、薄膜トランジスタパネル、及びこれらを製造する方法に関する。

【解決手段】薄膜トランジスタは、ゲート電極、ゲート絶縁膜、上記ゲート絶縁膜上に形成された酸化物半導体層、及び上記酸化物半導体層上に相互に離隔して形成されたドレーン電極及びソース電極を含む。上記ドレーン電極は、上記酸化物半導体層上に形成された第1のドレーン副電極及び上記第1のドレーン副電極上に形成された第2のドレーン副電極を含む。上記ソース電極は、上記酸化物半導体層上に形成された第1のソース副電極及び上記第1のソース副電極上に形成された第2のソース副電極を含む。上記第1のドレーン副電極及び上記第1のソース副電極は、ガリウム亜鉛酸化物(GaZnO)を含み、上記第2のドレーン副電極及び上記第2のソース副電極は、金属原子を含む。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】配線層中の配線をゲート電極として使用し、かつ拡散防止膜と同一層にゲート絶縁膜を有している半導体素子を有する半導体装置において、拡散防止膜の機能を損なうことなく、半導体素子のオン抵抗を低くする。

【解決手段】第1配線層150を構成する絶縁層の表層には、第1配線154及びゲート電極210が埋め込まれている。第1配線層150と第2配線層170の間には、拡散防止膜160が形成されている。ゲート絶縁膜230は、拡散防止膜160のうちゲート電極210と重なる領域及びその周囲の上面に凹部を形成し、この部分を薄くすることにより、形成されている。

(もっと読む)

デバイスおよび表示装置

【課題】基板上に形成された絶縁膜の応力を低減し、歩留まりが向上したデバイスおよびこのデバイスを備えた表示装置を提供する。

【解決手段】本開示の表示装置は、基板と、基板上の一部の領域に形成された金属層と、金属層上に設けられると共に、金属層未形成領域の少なくとも一部に溝を有する第1絶縁膜とを備える。

(もっと読む)

半導体装置の作製方法、および半導体装置

【課題】低温プロセスを実現する半導体装置の作製方法、及び半導体装置を提供する。

【解決手段】結晶構造を有する半導体層の一部にp型を付与する不純物元素及び水素を同時に添加することによって、一部の上層部分を非晶質化するとともに、一部の下層部分に結晶質を残存させ、加熱処理を行うことによって、一部の中の水素を拡散させる。

(もっと読む)

有機半導体素子およびその製造方法

【課題】本発明は、製造時におけるソース電極およびドレイン電極の劣化を好適に防止することができ、優れたスイッチング機能を有する有機半導体素子およびその製造方法を提供することを主目的とする。

【解決手段】基材と、上記基材上に形成されたゲート電極と、上記ゲート電極を覆うように形成されたゲート絶縁層と、上記ゲート絶縁層上に形成され、銀を主成分とする金属材料を含むソース電極およびドレイン電極と、上記ソース電極および上記ドレイン電極上に形成され、酸素に対する遮蔽性を有する電極保護層と、少なくとも上記ソース電極および上記ドレイン電極の間のチャネル領域に形成可能なパターン形状を有し、有機半導体材料を含む有機半導体層と、上記有機半導体層上のみに形成され、真空紫外光に対する遮光性を有する遮光材料を含むVUV遮蔽層とを有することを特徴とする有機半導体素子を提供することにより上記課題を解決する。

(もっと読む)

半導体装置および該半導体装置の作製方法

【課題】良好な電気特性を有する半導体装置および該半導体装置の作製方法を提供する。

【解決手段】ゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜を形成し、ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に水素透過膜を形成し、水素透過膜上に水素捕縛膜を形成し、加熱処理を行って、酸化物半導体膜から水素を脱離させ、酸化物半導体膜の一部に接するソース電極およびドレイン電極を形成し、水素捕縛膜の露出されている部分を除去して、水素透過膜のチャネル保護膜を形成する半導体装置の作製方法である。また、該作製方法で作製された半導体装置である。

(もっと読む)

薄膜トランジスタ及びその製造方法並びに画像表示装置

【課題】薄膜トランジスタにおいて、ゲート絶縁膜に直接ストライプ状に凹部を形成することで隔壁形成プロセスを省き、前記凹部をガイドとして塗布法により精度よく半導体溶液を所望の場所に形成し、トランジスタ素子分離を行うことのできる薄膜トランジスタの構造を提供する。また、その構造を用いた薄膜トランジスタの製造方法、及びそれを用いたが画像表示装置を提供すること。

【解決手段】基板と、前記基板上に形成されたゲート電極と、前記基板上及び前記ゲート電極上のゲート絶縁体層と、前記ゲート絶縁体層に形成された凹部と、前記絶縁体層の凹部内に形成される半導体層と、前記半導体層上の中央部に設けられる保護膜と、前記半導体層の両端部で接続されるソース電極とドレイン電極と、を有する薄膜トランジスタにおいて、前記ゲート絶縁体層の凹部がストライプ状に形成されていることを特徴とする薄膜トランジスタとする。

(もっと読む)

薄膜トランジスタとその製造方法、および当該薄膜トランジスタを用いた画像表示装置

【課題】隔壁形成プロセスを省き、かつ、塗布法により半導体溶液を所望の場所に形成し、トランジスタ素子分離を行うことのできる薄膜トランジスタを提供する。

【解決手段】基板上に形成された梯子状の凸部を有するゲートバス電極と、ゲートバス電極の表面形状に沿うように当該ゲートバス電極上および基板上に形成されたゲート電極と、ゲート電極の凹凸に沿うようにゲート電極上および基板上に形成されたゲート絶縁体層と、ゲート絶縁体層の凹部内に形成された半導体層と、半導体層の中央に形成された保護膜と、半導体層の両端部で接続されたソース電極とドレイン電極とを備える。

(もっと読む)

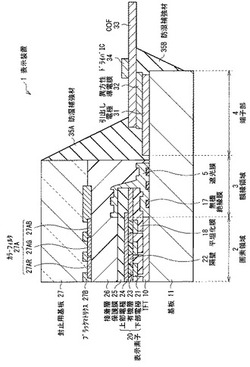

表示装置およびその製造方法

【課題】TFTの特性劣化を抑制しつつクロス容量を低下することが可能な表示装置およびその製造方法を提供する。

【解決手段】基板11上にゲート電極12および第1配線層21を形成したのち、全面にゲート絶縁膜13を形成する。次に、ゲート絶縁膜13上に半導体層14Aを形成したのち、半導体層14A上に第1保護膜15を形成する。第1配線層に対向する領域の半導体層14および第1保護膜15の除去およびその他の領域をエッチングにより加工する。次いで、全面に第2保護膜23を形成および加工したのち、ソース・ドレイン電極17および第2配線層24を形成する。これにより、チャネル層14表面の損傷が防止されると共に、配線部20のクロス容量が低減される。

(もっと読む)

薄膜トランジスタ及びその製造方法、表示装置

【課題】低温プロセスで製造できる酸化物半導体を用いた高信頼性の薄膜トランジスタ及びその製造方法、表示装置を提供する。

【解決手段】薄膜トランジスタは、基板と、前記基板上に設けられ、インジウムを主成分とする酸化物で形成された半導体層140と、前記半導体層140のソース電極コンタクト領域およびドレイン電極コンタクト領域を除いた上面を覆う第1の絶縁膜と、少なくとも前記半導体層140の1対の側面を覆う、前記第1の絶縁膜と異なる条件で成膜された第2の絶縁膜と、前記絶縁膜上または前記半導体層140下に設けられたゲート電極120と、前記半導体層140のソース電極コンタクト領域上に設けられたソース電極161と、前記半導体層140のドレイン電極コンタクト領域上に設けられ、前記半導体層140の1対の側面を挟んで前記ソース電極161と対向するドレイン電極162と、を有する。

(もっと読む)

半導体装置

【課題】さらなる低温プロセス(350℃以下、好ましくは300℃以下)を実現し、安

価な半導体装置を提供する。

【解決手段】本発明は、結晶構造を有する半導体層103を形成した後、イオンドーピン

グ法を用いて結晶質を有する半導体層103の一部にn型不純物元素及び水素元素を同時

に添加して不純物領域107(非晶質構造を有する領域)を形成した後、100〜300

℃の加熱処理を行うことにより、低抵抗、且つ非晶質な不純物領域108を形成し、非晶

質な領域のままでTFTのソース領域またはドレイン領域とする。

(もっと読む)

半導体装置の作製方法

【課題】電気特性の変動が生じにくく、且つ電気特性の良好な半導体装置の作製方法を提供することである。

【解決手段】基板上にゲート電極を形成し、ゲート電極上にゲート絶縁膜を形成し、酸化物半導体膜を形成し、第1の酸化物半導体膜を形成した後、加熱処理をして第2の酸化物半導体膜を形成し、第1の導電膜を形成し、厚さの異なる領域を有する第1のレジストマスクを形成し、第1のレジストマスクを用いて第2の酸化物半導体膜および第1の導電膜をエッチングして第3の酸化物半導体膜および第2の導電膜を形成し、第1のレジストマスクを縮小させて、第2のレジストマスクを形成し、第2のレジストマスクを用いて第2の導電膜の一部を選択的に除去することでソース電極およびドレイン電極を形成する半導体装置の作製方法である。

(もっと読む)

半導体装置及び電子機器

【課題】薄膜の応力を用いて、トランジスタのしきい値電圧を変化させる。

【解決手段】第1のチャネル形成領域を有する第1の半導体層と、第2のチャネル形成領域を有する第2の半導体層に対して、それらの上に形成された薄膜の応力を用いて、トランジスタのしきい値電圧を異ならせることができる。これらを電気的に接続することで、E/D MOS回路を提供できる。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】高速動作可能な半導体装置を提供する。また、短チャネル効果による電気特性の変動が生じにくい半導体装置を提供する。

【解決手段】トランジスタの半導体層に結晶性を有する酸化物半導体を用い、該半導体層にチャネル形成領域とソース領域とドレイン領域を形成する。ソース領域及びドレイン領域は、ゲート電極をマスクとして、半導体層に第15族元素のうち一種類または複数種類の元素を添加する自己整合プロセスにより形成する。ソース領域及びドレイン領域に、ウルツ鉱型の結晶構造を付与することができる。

(もっと読む)

半導体装置およびその作製方法

【課題】スパッタ法でトランジスタ、ダイオード等の半導体用途に好適な材料を提供する。具体的には結晶性の高い酸化物半導体膜を形成する作製プロセスを提供する。

【解決手段】意図的に窒素を酸化物半導体に対して添加することにより、六方晶であり、ウルツ鉱型結晶構造を有する酸化物半導体膜を形成する。酸化物半導体膜において、窒素を含む領域の結晶性は、窒素をあまり含まない領域、或いは窒素を意図的に添加していない領域に比べて高くなる。この結晶性の高いウルツ鉱型結晶構造を有する酸化物半導体膜をトランジスタのチャネル形成領域として用いる。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】バックチャネル部の表面のアルミニウム汚染に起因する漏れ電流を抑制を防止でき、高い信頼性と、高い歩留を実現できる構造の薄膜トランジスタを提供することを目的とする。

【解決手段】この発明に係る薄膜トランジスタは、シリコンを半導体層とするバックチャネル部を有するボトムゲート構造の薄膜トランジスタであって、アルミニウムを含むソース電極またはドレイン電極と、バックチャネル部の一部であって半導体層の表層を覆うサイアロン化合物の層とを有するものである。

(もっと読む)

21 - 40 / 220

[ Back to top ]