Fターム[5F110PP03]の内容

Fターム[5F110PP03]の下位に属するFターム

Fターム[5F110PP03]に分類される特許

101 - 120 / 2,255

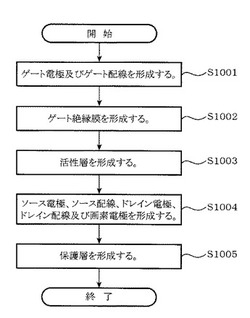

半導体デバイス及び薄膜トランジスタ、並びに、それらの製造方法

【課題】管理コストを低減し、さらに、製造工程を削減して製造原価のコストダウンを図ることの可能な半導体デバイス及び薄膜トランジスタ、並びに、それらの製造方法の提案を目的とする。

【解決手段】所定の材料からなり、活性層41となる半導体と、所定の材料と同じ組成の材料からなり、ソース電極51、ドレイン電極53及び画素電極55の少なくとも一つとなる導電体とを備えた薄膜トランジスタ2の製造方法であって、非晶質の所定の材料からなる被処理体及び導電体(ソース電極51、ソース配線52、ドレイン電極53、ドレイン配線54及び画素電極55)を一括成膜し、さらに一括形成する工程と、形成された被処理体を結晶化させて活性層41とする工程とを有する方法としてある。

(もっと読む)

記憶回路、記憶装置、信号処理回路

【課題】電源電圧の供給が停止した後もデータ保持可能な記憶回路の提供、消費電力の低減可能な信号処理回路を提供する。

【解決手段】記憶回路は、トランジスタと、容量素子と、第1の演算回路と、第2の演算回路と、第3の演算回路と、スイッチと、を有し、第1の演算回路の出力端子は、第2の演算回路の入力端子と電気的に接続され、第2の演算回路の入力端子は、スイッチを介して第3の演算回路の出力端子と電気的に接続され、第2の演算回路の出力端子は、第1の演算回路の入力端子と電気的に接続され、第1の演算回路の入力端子は、トランジスタのソース及びドレインの一方と電気的に接続され、トランジスタのソース及びドレインの他方は、容量素子の一対の電極のうちの一方、及び第3の演算回路の入力端子と電気的に接続され、トランジスタのチャネルは酸化物半導体層に形成される。

(もっと読む)

半導体装置及び電子器具

【課題】 可撓性を有するアクティブマトリクス型表示装置を実現する方法を提供することを課題とする。また、異なる層に形成された配線間の寄生容量を低減する方法を提供することを課題とする。

【解決手段】 第1の基板上に形成された薄膜デバイスと第2の基板とを接着して固定した後、第1の基板を取り除いて薄膜デバイスに配線等を形成する。その後、第2の基板も取り除き、可撓性を有するアクティブマトリクス型表示装置を形成する。また、第1の基板を取り除いた後、配線を活性層のゲート電極が形成されていない側に形成することにより、寄生容量を低減することができる。

(もっと読む)

NAND型不揮発性メモリのデータ消去方法

【課題】NAND型不揮発性メモリを提供する。

【解決手段】ビット線と、ソース線と、複数の不揮発性メモリが直列に接続されたNAND型セルと、選択トランジスタと、を有し、不揮発性メモリは、第1の絶縁膜を介した半導体上の電荷蓄積層と、第2の絶縁膜を介した電荷蓄積層上の制御ゲートと、を有し、NAND型セルの一方の端子は、選択トランジスタを介して、ビット線に接続され、NAND型セルの他方の端子は、ソース線に接続されたNAND型不揮発性メモリであって、第1の絶縁膜は、半導体に酸素雰囲気で高密度プラズマ処理を行った後、窒素雰囲気で高密度プラズマ処理を行うことで形成されるNAND型不揮発性メモリ。

(もっと読む)

基板上のフィルム領域を処理して、こうした領域内及びその端部領域をほぼ均一にするレーザ結晶化プロセス及びシステム、及びこうしたフィルム領域の構造

【課題】薄膜フィルム試料を処理するシステム、並びに薄膜フィルム構造を提供する。

【解決手段】フィルム試料170の一区画の特定部分の第1部分を融解させるべく照射ビームパルスの第1パルスの第1小ビームで照射して、この第1部分が少なくとも部分的に融解して自ずと再凝固して結晶化し、それぞれの隣接する第1部分どうしの間に第1未照射部分が残る。特定部分の第1小ビームによる照射の後に、この特定部分を、この特定部分の第2部分を融解させるべく照射ビームパルスの第2パルスの第2小ビームで再び照射して、この第2部分が少なくとも部分的に融解して自ずと再凝固して結晶化し、それぞれの隣接する第2部分どうしの間に第2未照射部分が残る。再凝固して結晶化した第1部分及び前記第2部分は、フィルム試料の領域内で互いに間に入り合う。これに加えて、第1部分が第1画素に対応し、第2部分が第2画素に対応する。

(もっと読む)

電気光学装置の製造方法

【課題】テトラエトキシシラン等のシラン系有機材料を用いたプラズマCVD法によりシリケートガラスを形成した場合でも、シリケートガラスから半導体層へのフッ素の侵入を防止することのできる電気光学装置の製造方法を提供すること。

【解決手段】液晶装置の製造方法において、ゲート電極3cの形成工程、低濃度不純物導入工程、および高濃度不純物導入工程を行った後、シランガス等のシラン系無機原料を用いたCVD法により第1絶縁膜411を形成する。次に、第1アニール工程において第1絶縁膜411をアニールした後、テトラエトキシシラン等のシラン系有機原料を用いたプラズマCVD法によりシリケートガラスからなる第2絶縁膜412を形成する。

(もっと読む)

半導体の製造方法及び半導体装置

【課題】複雑な工程を経ることなく、通常の半導体製造装置を使用して、低コストで、半導体装置の、低電圧動作、高集積性を実現する。

【解決手段】次の工程(1)〜(5)で半導体装置を製造する。(1)シリコン結晶製の半導体支持基板の表面を洗浄し、酸化被膜を除去して、結晶面を露出させる工程、(2)該結晶面上に高誘電率非晶質薄膜を低温で堆積する工程、(3)該高誘電率非晶質薄膜の結晶化開始温度よりも低いプレアニール温度で該高誘電率非晶質薄膜をプレアニールする工程、(4)該半導体支持基板を選択的に急速加熱することにより該高誘電率非晶質薄膜内部に基板界面から該薄膜表面方向に向けて温度が低くなる急峻な温度勾配を形成することにより該高誘電率非晶質薄膜を結晶化して、エピタキシャル薄膜を形成する工程、(5)該エピタキシャル薄膜の上面に半導体結晶の配向膜を形成する工程を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】高性能でかつばらつきの少ないナノワイヤトランジスタを備えた半導体装置およびその製造方法を提供する。

【解決手段】半導体基板上に第1絶縁膜を形成する工程と、第1絶縁膜上に設けられ、第1領域と第1領域よりも幅の広い第2および第3領域とを有しこれらの第2および第3領域の少なくとも一方が第1領域に接続するように構成された第1半導体層と、第1半導体層の上面に設けられるマスクと、を形成する工程と、マスクを用いて、前記第1半導体層の第1領域の側面にイオン注入を行う第1イオン注入を行う工程と、イオン注入を行った後に、第1熱処理を行う工程と、マスクを除去した後、第1半導体層の前記第1領域の少なくとも側面にゲート絶縁膜を形成する工程と、ゲート絶縁膜上にゲート電極を形成する工程と、ゲート電極の、第2および第3領域側の側面に絶縁体のゲート側壁を形成する工程と、少なくとも第1半導体層の第2および第3領域に第2イオン注入を行う工程と、とを備えている。

(もっと読む)

発光装置

【課題】駆動用トランジスタと、スイッチング用トランジスタを有する発光装置において、トランジスタのばらつきを低減する。

【解決手段】駆動用トランジスタと、スイッチング用トランジスタを有する発光装置において、駆動用トランジスタのチャネル幅をチャネル長よりも小さくする。その際、ゲート配線と平行にアノード側電源線を設けて、フルカラー表示を行う。

(もっと読む)

電界効果トランジスタのゲート絶縁層用組成物、ゲート絶縁層、電界効果トランジスタ及び表示パネル

【課題】エッチング液や剥離液に対する耐性に優れているゲート絶縁層を形成することにより、このゲート絶縁層上にエッチング法により電極を形成させることができるようにすること。及び、その上に半導体材料を湿式塗布、結晶化処理しても溶出し難いゲート絶縁層を形成すること。すなわち、安価で高性能な上に、樹脂製のフレキシブル基板に適用可能な電界効果トランジスタを製造すること。

【解決手段】電界効果トランジスタのゲート絶縁層用組成物であって、重合性モノマー、重合開始剤及び架橋性基としてアリル基及び/又は(メタ)アクリロイル基を有する樹脂を含み、該重合性モノマーがエチレン性不飽和結合を2個以上有し、該架橋性基を有する樹脂の架橋性基当量が800g/eq以下であることを特徴とする電界効果トランジスタのゲート絶縁層用組成物。

(もっと読む)

半導体装置

【課題】大面積化しても低消費電力を実現した半導体装置の構造およびその作製方法を提供する。

【解決手段】画面で使われる画素の薄膜トランジスタを作製する。その薄膜トランジスタにおいて、ソース配線、ゲート電極を同一平面上に作製する。また、ソース配線と薄膜トランジスタをつなぐ配線と、画素電極と薄膜トランジスタをつなぐ配線を同一工程で作製する。

(もっと読む)

半導体装置

【課題】隣接する画素の間に設ける絶縁膜は、バンク、隔壁、障壁、土手などとも呼ばれ

、薄膜トランジスタのソース配線や、薄膜トランジスタのドレイン配線や、電源供給線の

上方に設けられる。特に、異なる層に設けられたこれらの配線の交差部は、他の箇所に比

べて大きな段差が形成される。隣接する画素の間に設ける絶縁膜を塗布法で形成した場合

においても、この段差の影響を受けて、部分的に薄くなる箇所が形成され、その箇所の耐

圧が低下されるという問題がある。

【解決手段】段差が大きい凸部近傍、特に配線交差部周辺にダミー部材を配置し、その上

に形成される絶縁膜の凹凸形状を緩和する。また、上方配線の端部と下方配線の端部とが

一致しないように、上方配線と下方配線の位置をずらして配置する。

(もっと読む)

表示装置およびその製造方法

【課題】スキャナ内のトランジスタの特性の差に起因するスジの発生を抑止することが可能な表示装置およびその製造方法を提供する。

【解決手段】アクティブマトリクス型有機EL表示装置のELA結晶化工程においてエキシマレーザのスキャン方向と、垂直スキャナ内のバッファを形成するトランジスタ(TFT)210のL長方向(電流が流れる方向)が直交する方向になるようにし、かつ、スキャナの画素配列に対応する各段バッファ群の各トランジスタが、チャネル長方向と同方向である駆動信号の出力線の配線方向と直交する方向において、列をなすように形成され、列をなすように形成された各段バッファ群の各トランジスタは、チャネル幅方向において大きい部分と小さい部分とが混在し、かつ、チャネル幅方向における同様の領域において粒径の大きい部分と小さい部分とが存在する。

(もっと読む)

薄膜半導体装置

【課題】工程を複雑にすることなく、多結晶シリコン膜に回路特性に適した複数の異なる

ゲート絶縁膜厚を有する薄膜トランジスタ(TFT)を同一基板に形成することができる

薄膜半導体装置とその製造方法を提供。

【解決手段】ガラス基板上に形成した多結晶シリコン膜に駆動電圧が異なるTFTを混載

する際に、低電圧駆動TFTではチャネル領域の不純物をアクセプタがより多くなるよう

にしあるいはドナーがより少なくなるようにし、高電圧駆動TFTではチャネル領域の不

純物をドナーがより多くなるようにしあるいはアクセプタがより少なくなるようにする。

(もっと読む)

半導体装置の製造方法、半導体装置、電気光学装置および電子機器

【課題】チャネルドープを含む製造工程を簡略化できる半導体装置の製造方法、半導体装置、電気光学装置および電子機器を提供すること。

【解決手段】本適用例の半導体装置の製造方法は、基板に半導体膜としての多結晶半導体膜14aを形成する工程と、多結晶半導体膜14a上に、少なくとも2つの異なる膜厚を有し、それぞれが孤立したレジストパターン16,17を形成するレジスト形成工程と、該レジストパターン16,17をマスクとして多結晶半導体膜14aに第一不純物の注入を行う第一不純物注入工程と、該レジストパターン16,17に沿って多結晶半導体膜14aをエッチングするエッチング工程と、該レジストパターン16,17を剥離する工程とを有し、第一不純物注入工程は、レジストパターン16,17の膜厚の差に基づいて、第一不純物の注入、非注入を制御することを特徴とする。

(もっと読む)

半導体装置

【課題】小型化、薄型化、軽量化を実現した半導体装置の提供を課題とする。また、作製時間を短縮し、歩留まりを向上することができる半導体装置の作製方法の提供を課題とする。

【解決手段】トランジスタと、トランジスタ上に設けられた絶縁層と、絶縁層に設けられた開口部を介して、トランジスタのソース領域又はドレイン領域に電気的に接続された第1の導電層(ソース配線又はドレイン配線に相当)と、絶縁層及び第1の導電層上に設けられた第1の樹脂層と、第1の樹脂層に設けられた開口部を介して、第1の導電層に電気的に接続された導電性粒子を含む層と、第2の樹脂層及びアンテナとして機能する第2の導電層が設けられた基板とを有する。上記構成の半導体装置において、第2の導電層は、導電性粒子を含む層を介して、第1の導電層に電気的に接続されている。また、第2の樹脂層は、第1の樹脂層上に設けられている。

(もっと読む)

液晶表示装置

【課題】動作性能および信頼性の高い液晶表示装置を提供する。

【解決手段】トランジスタ上に第1の絶縁膜を有し、第1の絶縁膜上に第1及び第2の配線を有し、第1及び第2の配線上に第2の絶縁膜を有し、第2の絶縁膜上に電極を有し、電極上に第3の絶縁膜を有し、第3の絶縁膜上に画素電極を有し、画素電極は、電極と重なる第1の領域と、電極と重ならない第2の領域と、を有し、画素電極は、第1の配線に電気的に接続されており、第1の配線は、トランジスタのソース又はドレインの一方と電気的に接続されており、電極は、画素部の外側において前記第2の配線と電気的に接続されている。

(もっと読む)

EL表示装置

【課題】動作性能および信頼性の高いEL表示装置を提供する。

【解決手段】第1のチャネル形成領域と、第1のソース領域及び第1のドレイン領域と、ゲート絶縁膜と、第1のゲート電極とを備えた第1のTFTと、第2のチャネル形成領域と、第2のソース領域及び第2のドレイン領域と、ゲート絶縁膜と、第2のゲート電極とを備えた第2のTFTと、第1のTFT及び第2のTFT上に設けられた第1の絶縁膜と、第1のソース領域及び第1のドレイン領域の一方と接続されたソース配線と、第1のソース領域及び第1のドレイン領域の他方と接続し、且つ第2のゲート電極に接続された第1のドレイン配線と、第1の絶縁膜上に設けられ、第2のソース領域及び第2のドレイン領域の一方に接続された第2のドレイン配線と、第1の絶縁膜上に設けられ、第2のソース領域及び第2のドレイン領域の他方に接続された電流供給線と、を有する。

(もっと読む)

表示装置および電子機器

【課題】配線層を低抵抗に保ち、かつ薄膜トランジスタにおける膜剥がれを防止した表示装置および電子機器を提供する。

【解決手段】基板11上に薄膜トランジスタ10および配線層20を備える。薄膜トランジスタ10は、基板11側からゲート電極12,ゲート絶縁膜13および半導体層14を有し、配線層20は、配線層20aおよび配線層20bにより構成されている。配線層20bとゲート電極12とは同一の膜厚および構成材料からなる。配線層20とゲート電極12との厚みは異なっている。具体的には、ゲート電極12の厚みは配線層20の厚みよりも薄く、ゲート電極12の膜内応力が小さくなっている。

(もっと読む)

液晶表示装置、電子機器

【課題】IPSにおける従来の技術は、工程数が多く、開口率が低いので、実用化できな

い。また、液晶層に最も近接している層に存在する配線及び電極が多く、画素表示部にお

ける個々の液晶にかかる電界が不均一であった。

【解決手段】本発明は、ゲイト線102、105とコモン線103、104を最初に同時

に形成し、層間膜形成後、画素電極108とコモン電極110、111とソ─ス線106

、107を同時に形成する。こうすることによって、電極パタ─ンを単純化でき、工程を

簡略化した。また、液晶層に最も近接している層に存在する配線及び電極を画素電極とコ

モン電極とソ─ス線とし、その形状を単純なものにした。

(もっと読む)

101 - 120 / 2,255

[ Back to top ]