Fターム[5F140AA39]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 目的 (9,335) | 微細化 (812)

Fターム[5F140AA39]に分類される特許

161 - 180 / 812

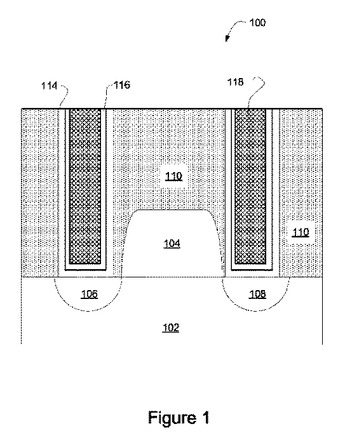

半導体装置及びその製造方法

基板(11)上に形成されたフィン型半導体領域(13)の両側部にエクステンション領域(17)が設けられている。フィン型半導体領域(13)を跨ぐと共にエクステンション領域(17)と隣り合うようにゲート電極(15)が形成されている。ゲート電極(15)と隣り合う領域のフィン型半導体領域(13)の上部に、エクステンション領域(17)よりも高い抵抗率を有する抵抗領域(37)が形成されている。 (もっと読む)

半導体デバイスの形成方法及びエッチング・マスク

【課題】 フィン型FETデバイス及びこれの製造方法を提供する。

【解決手段】 半導体デバイスは、基板を準備しそして基板上に半導体含有層を形成することにより形成される。次いで、複数個の開口を有するマスクが、半導体含有層上に形成され、ここでマスクの複数個の開口のうち互いに隣接する開口は、最小構造寸法だけ離されている。その後、半導体含有層の第1部分にドーパントを導入するために、角度付けしたイオン注入が行われ、ここでドーパントがほぼ存在しない残りの部分がマスクの下側に存在する。サブリソグラフィック寸法のパターンを形成するために、半導体含有層のうちドーパントを含む第1部分がこの半導体層のうちドーパントをほぼ含まない残りの部分に対して選択的に除去され、そしてサブリソグラフィック寸法のフィン構造を生じるために、パターンが基板に転写される。

(もっと読む)

減少させられたゲート電極ピッチを有する非対称トランジスタのための段階的なウエル注入

【解決手段】

洗練された半導体デバイスにおいて、非対称ウエル注入に基いて非対称トランジスタ構造が得られる一方で傾斜注入プロセスは回避し得る。この目的のために、段階的なレジストマスクのような段階的な注入マスクが形成されてよく、段階的な注入マスクは、非対称トランジスタのソース側と比較してドレイン側で高いイオン遮断能力を有していてよい。例えば、非対称構造は、高度な性能向上を伴う非傾斜注入プロセスに基いて得ことができ、また考慮されている技術標準にかかわりなく完成され得る。

(もっと読む)

半導体装置およびその製造方法

【課題】移動体通信装置用半導体装置(RFパワーモジュール)の電力付加効率を向上させる。

【解決手段】パワーMOSFETのゲート電極7とn+型ドレイン領域15との間に介在するオフセットドレイン領域を二重オフセット構造とし、ゲート電極7に最も近いn−型オフセットドレイン領域9の不純物濃度を相対的に低く、ゲート電極7から離間したn型オフセットドレイン領域13の不純物濃度を相対的に高くする。これにより、オン抵抗(Ron)と帰還容量(Cgd)を共に小さくすることができるので、増幅素子をシリコンパワーMOSFETで構成したRFパワーモジュールの小型化と電力付加効率の向上を図ることができる。

(もっと読む)

半導体装置の製造方法及び設計支援装置

【課題】コンタクト領域の欠損を抑制する技術を提供する。

【解決手段】半導体装置の製造方法は、基板上方に導電膜を形成し、導電膜上に補助パターンを形成し、導電膜及び補助パターンを覆うように金属膜を形成し、金属膜をエッチバックし、補助パターンの側面にサイドウォール膜を形成し、補助パターンを除去し、導電膜及びサイドウォール膜の一部を覆い、一部を露出させるレジストパターンを形成し、レジストパターンをマスクとしてエッチングによりサイドウォール膜の露出している部分を除去し、サイドウォール膜をマスクとして導電膜をエッチングして、ゲート電極及びゲート電極と導通するコンタクト領域を形成し、露出している部分が除去されることにより導電膜上に残存するサイドウォール膜の形状は、ゲート電極及びコンタクト領域の形状に対応し、補助パターンの形状は、コンタクト領域の形状に対応するサイドウォール膜の少なくとも三辺と接する。

(もっと読む)

半導体装置の製造方法

【課題】所望のシリサイド膜を形成しつつ、半導体装置の生産性を向上することが可能な半導体装置の製造方法を提供する。

【解決手段】第1の圧力の不活性雰囲気中において、第1の加熱温度の第1の加熱処理により、ソース・ドレイン拡散層のシリコンとソース・ドレイン拡散層上の金属とを反応させて、ソース・ドレイン拡散層の上部をシリサイド化してシリサイド膜を形成し、第2の圧力の酸化性雰囲気において、第2の加熱温度の第2の加熱処理により、素子分離絶縁膜の上の金属膜の少なくとも表面を選択的に酸化して、金属酸化膜を形成し、第1の加熱温度および第2の加熱温度よりも高い第3の加熱温度の第3の加熱処理により、シリサイド膜のシリコンの濃度を増加し、素子分離絶縁膜上の金属酸化膜および金属膜の未反応部分を選択的に除去する。

(もっと読む)

MISトランジスタ

【課題】ゲート電極とソース/ドレイン電極間で電気的短絡を起こし難いMISトランジスタを得る。

【解決手段】サイドウォール15を二重構造とする。バッファ層13は窒化酸化シリコンで形成され、バッファ層13の上に窒化シリコン層14が形成される。このサイドウォール15をマスクとしてシリサイド膜10を形成する。バッファ層13は窒化酸化シリコンのみならず、酸化シリコンで形成されてもよい。シリサイド膜はコバルトシリサイドでも、ニッケルシリサイドでもよい。窒化シリコン層14はバッファ層13よりも大きい応力を持つ。

(もっと読む)

半導体装置、及びその製造方法

【課題】、サイズを小さくできると共に、外部からのノイズに強く、漏洩電流が抑制された半導体装置及びその製造方法を提供すること。

【解決手段】 例えば、半導体基板10と、半導体基板10に形成されたP型のウェル10A(第1伝導型の第1領域)と、P型のウェル10A内に埋め込まれて形成されたN型のウェル10B(第2伝導型の第2領域)と、P型のウェル10A内であってN型のウェル10Bよりも上方に形成されたP型のウェル10C(第1伝導型の第3領域)と、P型のウェル10Cに形成された半導体素子20と、P型のウェル10CをN型のウェル10Bと共に取り囲むと共に、少なくとも底部がN型のウェル10Bと接触する深さを持って形成されたトレンチ型絶縁領域30と、を具備する半導体装置、及びその製造方法である。

(もっと読む)

金属−絶縁体−半導体トンネリングコンタクト

本発明はソース領域又はドレイン領域へのコンタクトに関する。コンタクトは導電性材料を有するが、その導電性材料は絶縁体によりソース領域又はドレイン領域から分離されている。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】従来の半導体装置では、分離領域の形成領域を狭めつつ、MOSトランジスタの動作耐圧を向上させ難いという問題があった。

【解決手段】本発明の半導体装置では、P型の埋込層9が這い上がり、P型の拡散層12が這い下がり、両拡散層9、12が連結することで、MOSトランジスタ3のバックゲート領域が構成される。この構造により、分離領域1のP型の拡散層13の横方向拡散幅が抑制され、分離領域の形成領域及びMOSトランジスタのデバイスサイズが低減される。その一方で、バックゲート領域での寄生抵抗が低減し、MOSトランジスタの動作耐圧が向上する。

(もっと読む)

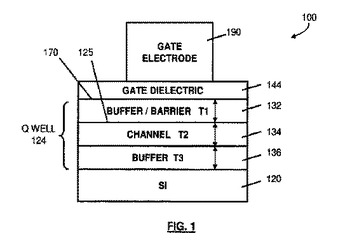

金属ソース/ドレイン及びコンフォーマル再成長ソース/ドレインにより発生される一軸性歪みを有する量子井戸MOSFETチャネル

開示の実施形態は、MOSチャネル領域に一軸性歪みを与える金属ソース/ドレイン及びコンフォーマル再成長ソース/ドレインを備えた、歪みトランジスタ量子井戸(QW)チャネル領域を含む。チャネル層の除去された部分が、チャネル材料の格子間隔とは異なる格子間隔を有するジャンクション材料で充填されることで、量子井戸の頂部バリア層及び底部バッファ層によってチャネル層に発生される二軸性歪みに加えて、一軸性歪みがチャネルに発生される。  (もっと読む)

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】従来の同一サイズの半導体装置と比較してゲート耐圧を向上させるとともに、素子分離層をバーズビークを含まない構造とすることにより素子分割領域の面積を縮小し、素子の微細化を図ることができる半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体基板表面に素子形成領域から素子分割領域に亘って延在するLOCOS膜を形成する。素子形成領域内の半導体基板上にLOCOS膜に接続されたゲート酸化膜を形成する。LOCOS膜およびゲート酸化膜を覆うように導電膜を形成する。導電膜を部分的にエッチングしてゲート酸化膜およびLOCOS膜の一部を覆うゲート電極を形成する。導電膜のエッチングによって露出したLOCOS膜を部分的にエッチングしてLOCOS膜を素子分離層とゲート酸化膜の端部を構成する高膜厚部とに分割する。LOCOS膜のエッチングによって露出した半導体基板の表面にイオン注入を行ってゲート電極を挟む位置にドレイン領域およびソース領域を形成する。

(もっと読む)

半導体装置

【課題】半導体基板において回路が形成される領域の占有面積を削減して小型化が図られる半導体装置を提供する。

【解決手段】高電位が印加されるセンス抵抗9と第1ロジック回路26が形成された高電位ロジック領域25の周囲を取り囲むように、分離領域30を介在させて、RESURF領域24が形成されている。RESURF領域24の外側には、接地電位に対して第2ロジック回路22を駆動させるのに必要な駆動電圧レベルが印加される第2ロジック回路領域が形成されている。RESURF領域24では、電界効果トランジスタTのドレイン電極12が内周に沿って形成され、ソース電極10が外周に沿って形成されている。また、センス抵抗9に接続されたポリシリコン抵抗4が、内周側から外周側に向かってスパイラル状に形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の小型化が進んでも半導体装置の信頼性向上を図ることができる技術を提供する。

【解決手段】本発明の技術的思想は、積層形成される窒化シリコン膜SN1〜SN3のそれぞれの膜厚を一定値ではなく、トータルの総膜厚を一定に保ちながら、上層の窒化シリコン膜SN3から下層の窒化シリコン膜SN1にしたがって膜厚を薄くするように構成している点にある。これにより、歪シリコン技術を実効あらしめる窒化シリコン膜SN1〜SN3の引張応力を確保しながら、特に、最上層の窒化シリコン膜SN3の埋め込み特性を改善できる。

(もっと読む)

半導体装置の製造方法および熱処理装置

【課題】半導体装置の製造工程において、100msec以下のパルス幅で照射光を照射することによる半導体基板のダメージを抑え、半導体基板の割れによる歩留り低下を抑えるとともに、低抵抗化と浅接合化の両立を図ることが可能な半導体装置の製造方法と熱処理装置を提供する。

【解決手段】表面に素子領域が形成された半導体基板wの表面に、0.1〜100msecのパルス幅で所定の照射エネルギー密度の第1の照射光を照射すると同時に、半導体基板wの裏面の外周部に0.1〜100msecのパルス幅で所定の照射エネルギー密度の第2の照射光を照射し、半導体基板wの裏面の外周部の温度が、半導体基板wの表面の中心の温度より高温となるように熱処理を行う。

(もっと読む)

半導体装置及びその製造方法

【課題】シリサイド層が第1不純物拡散層まで拡がるのを抑制し、複数種類のトランジスタを自由に設計することが可能な半導体装置及びその製造方法を提供する。

【解決手段】少なくとも、基台部1Bの上に複数立設された柱状のピラー部1Cを含むシリコン基板1と、基台部1Bの側面1bを覆うように設けられるビット線6と、ピラー部1Cの側面を覆うゲート絶縁膜4と基台部1Bの上面1aにおいて、ピラー部1Cが設けられる位置以外の領域に設けられる第1不純物拡散層8と、ピラー部1Cの上面1dに形成される第2不純物拡散層14と、ビット線6とシリコン基板1との間に形成され、第1不純物拡散層8との間で高低差を有し、且つ、上端5aが、第1不純物拡散層8の上端8aよりも低い位置に配されてなる第3不純物拡散層5と、ピラー部1Cの側面1c側に設けられるワード線10の一部をなすゲート電極10Aと、が備えられる。

(もっと読む)

半導体装置及びその製造方法

【課題】 素子分離絶縁膜の微細化、及びMOSトランジスタの性能向上を図る。

【解決手段】

第1のMOSトランジスタと第2のMOSトランジスタを有する半導体装置において、第1のMOSトランジスタ11が形成される半導体基板100の第1の領域10と、第1の領域10に隣接され、かつ第2のMOSトランジスタ21が形成される半導体基板100の第2の領域20と、第1領域10と第2領域20の間に形成された第1の素子分離絶縁膜30と、第1領域10に形成された複数層の半導体エピタキシャル層12とを有し、第1の素子分離絶縁膜30のアスペクト比が6.7以上である半導体装置。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】コンタクトプラグとゲート電極との間のショートおよび/またはコンタクトプラグとシリコンピラーとの間のショートを防止した半導体装置および半導体装置の製造方法を得るという課題があった。

【解決手段】基板1上に立設された第一のシリコンピラー2と、その側面を覆う絶縁膜5と、絶縁膜5を覆うとともに、その先端部6aが第一のシリコンピラー2の先端部2aよりも基板1よりに位置してなるゲート電極6と、からなる縦型Tr部101と、基板1上に立設された第二のシリコンピラー2’と、その側面を覆う絶縁膜5’と、絶縁膜5’を覆うとともに、その先端部6’aが第二のシリコンピラー2’の先端部2’aよりも基板1から離れた側に位置してなり、ゲート電極6に接続されてなるゲートコンタクト電極6’と、からなるゲートコンタクト部102と、を有する半導体装置111を用いることにより、上記課題を解決できる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】簡易な手順で、位置あわせ精度の高い横型電界効果トランジスタを含む半導体装置を得る。

【解決手段】半導体装置100は、ゲート電極110上に、ゲート長方向の少なくとも一方側に櫛歯を有する櫛形の櫛形絶縁膜150を形成する工程と、櫛形絶縁膜150をマスクとして、半導体基板101に第1導電型の不純物イオンを注入してゲート電極110のゲート幅方向に沿って、第1導電型の不純物拡散領域と第2導電型の不純物拡散領域とがそれぞれ一定幅で交互に配置された超接合構造のドリフト領域172を形成する工程と、櫛形絶縁膜150の両側方に形成され、櫛形絶縁膜150の櫛歯の間の領域を埋め込むサイドウォール152を形成する工程と、サイドウォール152をマスクとして、ソース領域116aおよびドレイン領域116bを形成する工程と、を含む。

(もっと読む)

半導体装置とその製造方法

【課題】柱状半導体層が微細化されて高集積化されても、コンタクト抵抗の増加を抑制する構造の半導体装置を提供する。

【解決手段】半導体装置は、基板(半導体基板1)と、半導体基板1上に設けられた、半導体柱状部(柱状半導体層3)と、の天面に接するように設けられた、柱状半導体層3と同径以下のコンタクト柱状部(コンタクト層7)と、この天面に設けられた凹部をと備えるものである。

(もっと読む)

161 - 180 / 812

[ Back to top ]