Fターム[5F140AA39]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 目的 (9,335) | 微細化 (812)

Fターム[5F140AA39]に分類される特許

141 - 160 / 812

半導体記憶装置

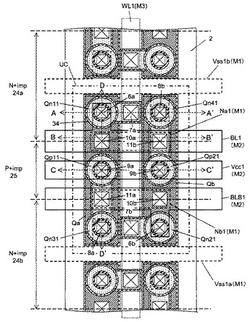

【課題】縦型トランジスタSGTで構成されたCMOS型6T−SRAMにおいて、小さいSRAMセル面積と安定した動作マージンを実現する。

【解決手段】6個のMOSトランジスタを用いて構成されたスタティック型メモリセルにおいて、前記メモリセルを構成するMOSトランジスタは、基板上に形成され、ドレイン、ゲート、ソースが垂直方向に配置され、ゲートが柱状半導体層を取り囲む構造を有し、前記基板は第1の導電型を持つ第1の活性領域と第2の導電型を持つ第2の活性領域からなり、それらが基板表面に形成されたシリサイド層を通して互いに接続されることにより小さい面積のSRAMセルを実現する。また、基板上に配置される第1のウェルと同一の導電型を持つドレイン拡散層のそれぞれを第1のウェルと反対の導電型を持ち、第1のウェルより浅い第2のウェル及び第3のウェルで囲むことにより、基板へのリークを抑制する。

(もっと読む)

半導体装置及びその製造方法

【課題】導電層を自己整合的に形成する場合において、第1の拡散層コンタクトプラグのコンタクトマージンを比較的大きく取る。

【解決手段】半導体装置10は、第1のシリコンピラー14Aと、第1のシリコンピラー14Aの上面に設けられ、導電性材料が充填されたスルーホール30aを有する層間絶縁膜30と、スルーホール30aの上側開口部に設けられた第1の拡散層コンタクトプラグDC1とを備え、スルーホール30aの下側開口部の面積は前記第1のシリコンピラー14Aの上面の面積に等しくなっているとともに、スルーホール30aの上側開口部の面積はスルーホール30aの下側開口部の面積より大きくなっており、それによって、スルーホール30a内の導電性材料の第1の拡散層コンタクトプラグDC1との接続面の面積が第1のシリコンピラー14Aの上面の面積より大きくなっている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】素子分離構造の面積を増大させることなく、素子分離構造の表面の後退量を低減させる。

【解決手段】半導体基板11の表面よりも低い位置に埋め込み絶縁層12を埋め込み、埋め込み絶縁層12と材料の異なるキャップ絶縁層13を半導体基板11と埋め込み絶縁層12と間の段差12aの肩の部分にかからないようにして埋め込み絶縁層12上に形成する。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】本発明は、薄膜トランジスタのソース領域やドレイン領域へのコンタクトを確実

にした半導体装置を提供するものである。

【解決手段】本発明における半導体装置において、半導体層上の絶縁膜およびゲイト電極

上に形成された第1の層間絶縁膜と、前記第1の層間絶縁膜の上に形成された第2の層間

絶縁膜と、前記第2の層間絶縁膜、前記第1の層間絶縁膜、および前記絶縁膜に設けられ

たコンタクトホールとを有する。前記第1の絶縁層の膜厚は、前記積層の絶縁膜の合計膜

厚の1/3以下に形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】EOTの増大及びキャリア移動度の低下を抑制しつつ、半導体基板表面に形成されている酸化膜と高誘電率絶縁膜との界面に、しきい値電圧を低減する電気双極子を形成可能な金属を添加する。

【解決手段】半導体基板100上にゲート絶縁膜140を介してゲート電極150が形成されている。ゲート絶縁膜140は、酸素含有絶縁膜101と、第1の金属を含む高誘電率絶縁膜102とを有する。高誘電率絶縁膜102は、第1の金属とは異なる第2の金属をさらに含む。高誘電率絶縁膜102における第2の金属の組成比が最大になる位置は、高誘電率絶縁膜102と酸素含有絶縁膜101との界面及び高誘電率絶縁膜102とゲート電極150との界面のそれぞれから離れている。

(もっと読む)

半導体装置の製造方法

【課題】ハーフピッチサイズが32nm以下のCMISデバイスを有する半導体装置において、nチャネル型電界効果トランジスタおよびpチャネル型電界効果トランジスタのそれぞれの閾値電圧を適切に設定することのできる技術を提供する。

【解決手段】pMIS形成領域に、主としてAlが拡散した高誘電体膜5h(例えばHfO2膜)により構成されるゲート絶縁膜5ならびに下層メタルゲート電極6Dと上層メタルゲート電極6Uとの積層膜からなるメタルゲート電極6を有するpMIS100pを形成し、nMIS形成領域に、主としてLa(ランタン)が拡散した高誘電体膜5h(例えばHfO2膜)により構成されるゲート絶縁膜11ならびに上層メタルゲート電極6Uからなるメタルゲート電極12を有するnMIS100nを形成する。

(もっと読む)

非対称型半導体デバイス及び製造方法

【課題】 非対称型半導体デバイス、及びその製造の際にスペーサ・スキームを用いる方法を提供する

【解決手段】 高kゲート誘電体の表面上に配置された非対称型ゲート・スタックを含む半構造体が提供される。非対称型ゲート・スタックは、第1の部分と第2の部分とを含み、第1の部分は、第2の部分とは異なる閾値電圧を有する。本発明の非対称型ゲート・スタックの第1の部分は、下から上に、閾値電圧調整材料及び少なくとも第1の導電性スペーサを含み、本発明の非対称型ゲート・スタックの第2の部分は、ゲート誘電体の上の少なくとも第2の導電性スペーサを含む。幾つかの実施形態において、第2の導電性スペーサは、下にある高kゲート誘電体と直接接触しており、他の実施形態においては、第1及び第2の導電性スペーサは、前記閾値電圧調整材料と直接接触している。

(もっと読む)

半導体装置の製造方法

【課題】短いゲート長を加工可能にする半導体装置の製造方法を提供すること。

【解決手段】半導体装置の製造方法の一形態は、シリコン基板2上にシリコン酸化膜34を形成し、酸化膜34上に所定幅T1を有する多結晶シリコン膜35aを形成し、少なくとも多結晶シリコン膜35aの両側部を酸化し、所定幅T1よりも狭い幅を有する酸化膜34の部分を多結晶シリコン膜35aの下に残すように、酸化膜34を、多結晶シリコン膜35aの酸化された部分と共にエッチングし、酸化された部分がエッチングされた多結晶シリコン膜35aをマスクとして、多結晶シリコン膜35aの両側のシリコン基板2の部分に不純物をイオン注入し、多結晶シリコン膜35aの両側に側壁絶縁膜14を形成し、側壁絶縁膜14が形成された多結晶シリコン膜35aをマスクとして、多結晶シリコン膜35aの両側のシリコン基板2の部分に不純物をイオン注入する、工程を有する。

(もっと読む)

半導体装置

【課題】小型の静電破壊保護トランジスタを有する半導体装置を提供する。

【解決手段】第1導電型の半導体層12に、ゲート絶縁膜13を介して形成されたゲート電極14と、ゲート電極14のゲート幅方向Yに沿って形成された第2導電型の第1不純物拡散層15と、ゲート幅方向Yに沿って第1不純物拡散層15と対向配置された本体部16aと、本体部16bからゲート電極14と反対側に突出した複数の凸部16bとを有し、ゲート電極14のゲート長方向Xの幅Wd1が第1不純物拡散層15のゲート長方向Xの幅Ws1より大きい第2導電型の第2不純物拡散層16と、を備えた絶縁ゲート電界効果トランジスタ17を具備する。

(もっと読む)

半導体デバイスとその形成方法(高k金属ゲートCMOS)

【課題】 金属酸化膜半導体電界効果トランジスタ内にデバイス性能を改善するゲート構造体を提供する。

【解決手段】 基板のp型デバイス領域の上にGe含有層を形成することを含む、半導体デバイスを形成する方法が提供される。その後、基板の第2の部分内に第1の誘電体層が形成され、基板の第2の部分内の第1の誘電層及び基板の第1の部分の上を覆うように、第2の誘電体層が形成される。次に、基板のp型デバイス領域及びn型デバイス領域の上にゲート構造体を形成することができ、n型デバイス領域へのゲート構造体は希土類金属を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】ウェル電位固定用のウェル給電用素子を設ける際に、縦型MOSトランジスタ間に素子分離用の埋込絶縁層を必要とせず、素子分離用の埋込絶縁層の形成に必要な面積を削減して、半導体装置の高集積化を図る。

【解決手段】半導体基板1に形成された第1導電型のウェル2内に、ウェル給電用素子Xと縦型MOSトランジスタYとが備えられ、ウェル給電用素子Xは、ウェル2と同じ導電型のボディ領域からなるピラー部P1を有し、ピラー部P1の上部には、第1導電型のウェル2の濃度よりも高い濃度を有する第1導電型の第1不純物拡散層13を備え、縦型MOSトランジスタYは、ウェル2と同じ導電型のボディ領域からなるピラー部P2を有し、かつ縦型MOSトランジスタYのピラー部P2の上部には、第2導電型の第2不純物拡散層7を備えることを特徴とする半導体装置を採用する。

(もっと読む)

半導体装置

【課題】デジタル回路と高周波回路とを混載した半導体装置において、デジタル回路の微細化を進めつつ、高周波回路の配線間容量を小さくする。

【解決手段】高周波回路100の第1トランジスタ120,140の第1ゲート電極124,144から第1コンタクト162,166までの距離aは、デジタル回路200の第2トランジスタ220,240の第2ゲート電極224,244から第2コンタクト262,266までの距離bより大きい。第1コンタクト162,166は第1トランジスタ120,140のドレイン126,146に接続しており、第2コンタクト262,266は第2トランジスタ220,240のドレイン226,246に接続している。

(もっと読む)

調整した垂直窒素濃度分布を具備する窒化ゲート誘電体層を有する電界効果トランジスタの構成及び製造

【課題】 絶縁ゲート電界効果トランジスタ(110,114又は122)のゲート誘電体層(500,566又は700)は、垂直濃度分布を有する窒素を含有している。

【解決手段】 該垂直濃度分布は、上側に位置しているゲート電極(502,568又は702)内のボロンが該ゲート誘電体層を介して下側のチャンネルゾーン(484,554又は684)内に著しく浸透することを防止し同時に該ゲート誘電体層から下側に存在する半導体ボディ内への窒素の移動を回避するために特別に調整されている。該チャンネルゾーン内の不所望のボロンから及び該半導体ボディにおける不所望の窒素から発生する場合がある損傷は実質的に回避される。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】高集積であり且つビット線を埋め込む必要のない3次元トランジスタを有する半導体記憶装置を提供する。

【解決手段】ゲートトレンチを介して両側に位置する第1及び第2の拡散層とゲートトレンチの底面に形成された第3の拡散層とを有する活性領域と、第1及び第2の拡散層にそれぞれ接続された第1及び第2の記憶素子と、第3の拡散層に接続されたビット線と、ゲート絶縁膜を介してゲートトレンチの第1の側面を覆い、第1の拡散層と第3の拡散層との間にチャネルを形成する第1のゲート電極と、ゲート絶縁膜を介してゲートトレンチの第2の側面を覆い、第2の拡散層と第3の拡散層との間にチャネルを形成する第2のゲート電極とを備える。本発明によれば、ゲートトレンチの両側面にそれぞれ別のトランジスタが形成されることから、従来の2倍の集積度が得られる。

(もっと読む)

ソース/ドレインゾーンに沿って調節したポケット部分を具備する非対称的電界効果トランジスタを有する半導体構成体の構成及び製造

【課題】 半導体ボディの上部表面に沿って設けられている非対称的絶縁ゲート電界効果トランジスタ(100U又は102U)は、該トランジスタボディ物質のチャンネルゾーン(244又は284)によって横方向に分離された第1及び第2ソース/ドレインゾーン(240及び242又は280及び282)を包含している。

【解決手段】 ゲート電極(262又は302)がチャンネルゾーン上方でゲート誘電体層(260又は300)の上側に位置している。該ボディ物質の横方向に隣接した物質よりも一層高度にドープした該ボディ物質のポケット部分(250又は290)が該S/Dゾーンの内のほぼ第1のもののみに沿って該チャンネルゾーン内に延在している。該ポケット部分の垂直ドーパント分布は、互いに離隔されている夫々の位置(PH−1乃至PH−3)において複数個の局所的最大(316−1乃至316−3)に到達すべく調節されている。該調節は、典型的に、該ポケット部分の垂直方向ドーパント分布が上部半導体表面近くで比較的平坦であるように実施される。その結果、該トランジスタのリーク電流は減少されている。

(もっと読む)

半導体装置及びその製造方法

【課題】 リーク電流の低減を実現しながらも従来に比べて更に素子サイズを縮小させることが可能な、高耐圧MOSトランジスタを実現する。

【解決手段】 P型ウェル10上に、チャネル領域chを隔てて、ドレイン領域12及びドレイン側ドリフト領域7を含むN型の第一不純物拡散領域と、ソース領域12及びそース側ドリフト領域8を含むN型の第二不純物拡散領域が形成されている。また、第一不純物拡散領域の一部上方、前記チャネル領域の上方、及び前記第二不純物拡散領域の一部上方にわたってゲート酸化膜6を介してゲート電極20が形成されている。ゲート電極20は、N型にドープされており、第一及び第二不純物拡散領域の上方に位置する部分の電極20bの不純物濃度が、前記チャネル領域の上方に位置する部分20aの不純物濃度よりも低濃度である。

(もっと読む)

半導体装置

【課題】対基板耐圧が向上しチップシュリンクも実現可能な、DTI構造を有する半導体装置を提供する。

【解決手段】例えばP型の基板1と、この基板1上に形成されたN型のEPI層2と、基板1とEPI層2とにわたって形成されたN型の第1の埋め込み層(埋め込み層3)と、この第1の埋め込み層の下に形成され埋め込み層3よりも不純物濃度の低いN型の第2の埋め込み層(埋め込み層12)と、EPI層2の表面から埋め込み層12、埋め込み層3を貫通して基板1内に達するDTI4と、を備えた半導体装置。

(もっと読む)

半導体装置

【課題】チャネル幅が狭い場合においても、eWFが十分に低減された閾値電圧が低い半導体装置を実現できようにする。

【解決手段】半導体装置は、素子分離領域102により分離された活性領域103を有する半導体基板101と、活性領域103の上に形成されたゲート絶縁膜111と、ゲート絶縁膜111の上に形成されたゲート電極121とを備えている。ゲート絶縁膜111は、シリコン及び酸素を除く第1の元素が拡散している。素子分離領域102は、第1の素子分離膜102Aと、第1の素子分離膜102Aよりもゲート絶縁膜111側に形成され且つ第1の素子分離膜102Aと比べて第1の元素が拡散しにくい第2の素子分離膜102Bとを有している。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極を形成するときのハードマスクを除去するときにゲート絶縁膜の側面がエッチングされることを抑制し、かつ、サイドウォールの上端がゲート電極の上面より上に位置することを抑制する。

【解決手段】ゲート絶縁膜110上に、ゲート電極126となる導電膜120を形成する。次いで、導電膜120上に、ハードマスクパターン70を形成する。次いで、ハードマスクパターン70をマスクとして導電膜120を選択的に除去することにより、ゲート電極126を形成する。次いで、ゲート電極126の側面に第1のサイドウォール140を形成する。次いで、ハードマスクパターン70をウェットエッチングにより除去する。ハードマスクパターン70を形成した後、第1のサイドウォール140を形成する前に、ハードマスクパターン70の側面52を、上に行くにつれてハードマスクパターン70の幅が狭くなる方向に傾斜させる。

(もっと読む)

半導体装置

【課題】半導体デバイスに対する多様な要求に対し、柔軟に対応することができる半導体デバイスを提供する。

【解決手段】基板(2)と、ゲート絶縁膜(6)を介して基板(2)の上に設けられるゲート電極(3)と、ゲート電極(3)に隣接して配置されるサイドウォール(5)とを具備する半導体装置(1)を構成する。ゲート電極(3)は、引き出し電極部分(3−2)と実効ゲート電極部分(3−1)とを備えることが好ましい。また、引き出し電極部分(3−2)は、第1方向に沿って延伸する素子分離(9)の上に形成され、第1方向に沿った第1側面(16)(17)を有する部分とする。実効ゲート電極部分(3−1)は、素子分離(9)で分離される領域の上に形成され、第1側面(16)(17)を含む面に交差する面に沿った第2側面を有する部分とする。サイドウォール(5)は、第1側面(16)(17)を覆うことなく第2側面を覆うものとする。

(もっと読む)

141 - 160 / 812

[ Back to top ]