Fターム[5F140AA39]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 目的 (9,335) | 微細化 (812)

Fターム[5F140AA39]に分類される特許

121 - 140 / 812

半導体装置の製造方法および半導体装置

【課題】縦型MOSトランジスタを備えた半導体装置を形成する際のゲート電極とコンタクトプラグとの短絡を防止することが可能な半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、前記半導体基板上にシリコン窒化膜(SiN膜)からなるマスク窒化膜のパターンを形成したのちに、溝および半導体ピラーを前記半導体基板に形成する第一工程と、前記マスク窒化膜を残存させたまま、前記溝を覆うゲート絶縁膜を形成したのちに前記半導体ピラーよりも低い高さのゲート電極を形成する第二工程と、前記溝を覆うように、シリコン酸窒化膜(SiON膜)からなるライナー膜を形成したのちに、前記ライナー膜上を覆い、かつ、前記溝内を充填するように層間膜(SOD膜)を形成する第三工程と、前記マスク窒化膜をエッチングにより選択的に除去する第四工程と、を採用する。

(もっと読む)

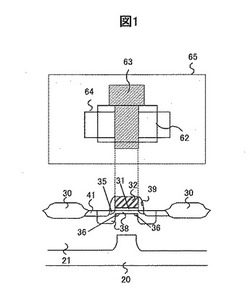

半導体装置及びその製造方法

【課題】 MOSトランジスタの製造工程を削減し、さらには寄生MOSの敷居値電圧が低下するのを抑制する。

【解決手段】 本発明の半導体装置の製造方法は、ゲート電極形成後にウェル拡散層とは逆導電型のチャネル形成用の不純物をイオン注入する製造方法において、フィールド酸化膜30にチャネル形成用の不純物をイオン注入しない製造方法である。従って、本発明の半導体装置は、フィールド酸化膜30にチャネル形成用の不純物がイオン注入されていない構造となる。

(もっと読む)

半導体装置の製造方法

【課題】トレンチ内に形成されたビット線の底面からのリーク電流を低減する。また、トレンチのアスペクト比を大きく増加させることなく、その後の工程でトレンチ内の空間に安定して成膜して、高アスペクト比による加工性の低下といった問題が生じない半導体装置を提供する。

【解決手段】半導体基板内にトレンチを形成する。このトレンチ内壁の底面上に第一の絶縁膜を形成する。また、トレンチ内壁の側面上に熱酸化により第一の絶縁膜よりも膜厚が薄い第二の絶縁膜を形成する。トレンチ内の第一の絶縁膜上に、ビット線を形成する。

(もっと読む)

半導体素子

半導体素子(例えば、フリップチップ)は、介在層によってドレインコンタクトから分離されたサブストレートを含む。前記介在層を通じて延びる前記素子の動作時において、トレンチ状のフィードスルー要素を用いて、前記ドレインコンタクトおよび前記サブストレートを電気的に接続する。 (もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

【課題】

幅広い電子デバイスのアレイ及びシステムにおける電力消費を低減する一式の新たな構造及び方法が提供される。一部の構造及び方法は、大部分が、既存のバルクCMOSのプロセスフロー及び製造技術を再利用することで実現され、半導体産業及びより広いエレクトロニクス産業がコスト及びリスクを伴って代替技術へ切り替わることを回避可能にする。一部の構造及び方法は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することと、チャネル領域にドーパントを有するFETの閾値電圧VTがより正確に設定されることとを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有することができ、それにより、DDCトランジスタにおける電力消費の有意義な動的制御が可能になる。様々な効果を達成するようDDCを構成する手法が数多く存在し得る。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極の下部からゲート電極の形成されていない基板上の領域に斜め方向のイオン注入を行って形成される不純物拡散領域を有する半導体装置において、半導体装置のサイズを従来に比して縮小化することができる半導体装置を提供する。

【解決手段】N型半導体層13の表面に形成されるP型のベース領域21と、ベース領域21内に形成されるP+型ソース領域22およびN+型ソース領域23を有するソース領域と、N型半導体層13の表面にベース領域21から離れて形成されるN+型のドレイン領域26と、ソース領域とドレイン領域26との間にゲート絶縁膜41を介して形成されるゲート電極42と、ドレイン領域26からゲート電極42の下部にかけて、ドレイン領域26に隣接して形成されるN型のドリフト領域と、を備え、ゲート電極42とゲート絶縁膜41との積層体のソース領域側側面の高さが、ドレイン領域側側面の高さよりも高く形成される。

(もっと読む)

電界効果トランジスタの製造方法

【課題】ゲート長が短い電界効果トランジスタを低コストで製造できる電界効果トランジスタの製造方法を提供すること。

【解決手段】基板上に、窒化物系化合物半導体からなるチャネル層および該チャネル層上に積層した上部層を含む半導体層を形成する工程と、半導体層の一部領域を少なくとも上部層からチャネル層に到る深さまでエッチングして、該チャネル層の表面の一部を底面部とし、エッチングによって露出した半導体層の側面を側壁部とする段差部を形成する工程と、段差部を含む半導体層の表面を覆うようにマスク層を形成し、該マスク層をエッチバックして該段差部のマスク層を残留させたマスク部を形成する工程と、イオン注入法によって、底面部のマスク部を除く領域にコンタクト領域を形成する工程と、マスク部を除去した後に、少なくとも段差部の底面部と側壁部とを覆うようにゲート絶縁膜およびゲート電極を順次形成する工程と、を含む。

(もっと読む)

多結晶シリコン・ゲート上のサリサイドの抵抗を改善するための方法およびデバイス

【課題】幅の狭いポリサイドゲートにおけるシリサイドの抵抗が改善されたゲート電極構造の製造方法を提供する。

【解決手段】リセスが形成されたシリコン酸化膜からなる厚い内部スペーサ、およびシリコン窒化膜からなる厚い外部スペーサを有する多結晶シリコンゲートを形成する。多結晶シリコン上にチタンをデポジションし、アニールによりチタンシリサイド層260を形成する。チタンシリサイド層は多結晶シリコンより幅広く形成され、シリコン酸化膜からなる厚い内部スペーサによって制約を受けず、応力を受けない。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極のテーパ形状の傾斜度を緩やかにすることができるようにして、ゲート電極の破損が起こらないようにしながら、確実にさらなる微細化を実現した下部電極を形成できるようにする。

【解決手段】ソース電極2及びドレイン電極3を有する半導体領域1上に絶縁膜4を形成し、絶縁膜4上に複数のレジスト層5,6,7を含む積層レジスト8を形成し、積層レジスト8の最下層以外のレジスト層6,7に開口9を形成し、最下層のレジスト層5にリフロー用開口10を形成し、熱処理を施してリフロー用開口10に露出している最下層のレジスト層5の一部PTcをリフローさせ、リフローさせることによって最下層のレジスト層5の表面に形成された傾斜面11に連なるように最下層のレジスト層5に第1ゲート下部開口12Aを形成し、開口9、傾斜面11及び第1ゲート下部開口12Aの形状に応じた形状を持つゲート電極13を形成する。

(もっと読む)

絶縁膜およびその製造方法、半導体装置、ならびにデータ処理システム

【課題】誘電率が大きく、電極間に挟んで用いてもリーク電流値の小さい絶縁膜を提供する。

【解決手段】結晶化した酸化ジルコニウムからなる酸化ジルコニウム膜の2つと、非晶質であって、前記結晶化した酸化ジルコニウムよりも大きい誘電率を有する材料からなる結晶粒界分断膜とを有し、前記結晶粒界分断膜が、前記2つの酸化ジルコニウム膜に挟まれている絶縁膜を形成する。例えば、上部電極と下部電極の間に容量絶縁膜を有するキャパシタ素子で構成されたメモリセルを備える半導体装置における容量絶縁膜や、コントロールゲート電極とフローティングゲート電極の間にインターゲート絶縁膜を有する不揮発性メモリ素子を備えた半導体装置におけるインターゲート絶縁膜として好適である。

(もっと読む)

半導体装置及びその製造方法

【課題】トレンチゲート型FIN−FETにおいて、微細化に対してもFIN型トランジスタの利点を十分に発揮し、また、活性領域において十分なコンタクト面積を確保し、オン電流の低下を抑制したトレンチゲート型FIN−FETを提供する。

【解決手段】チャネル領域のFIN幅(162)を活性領域の幅(161)よりも狭くする。

(もっと読む)

電磁気素子の製造方法

【課題】レジスト残渣に起因するリーク電流の増大を生じさせることがなく、微細パターンの形成が可能であり、電極のエッジ部分の絶縁膜が薄くなることに起因するリーク電流の増大を抑制することが可能な電磁気素子の製造方法を提供すること。

【解決手段】基板上に、12(CaxSr1-x)O・7Al2O3(0≦x≦1)を含む絶縁膜を形成する絶縁膜形成工程と、絶縁膜の上にアンモニウム塩アルカリ溶液を含む現像液で現像可能な第1フォトレジストを塗布し、第1フォトマスクパターンに応じて第1フォトレジストを露光する第1フォトレジストパターン形成工程と、第1フォトレジストをアンモニウム塩アルカリ溶液を含む現像液に接触させ、第1フォトレジストの可溶部分の溶解と同時に、絶縁膜をエッチングする現像・エッチング工程とを備えた電磁気素子の製造方法。

(もっと読む)

半導体装置

【課題】高耐圧の電界効果トランジスタを有する半導体装置のキンク現象を抑制または防止する。

【解決手段】高耐圧pMISQHp1のチャネル領域のゲート幅方向の両端の溝型の分離部3と半導体基板1Sとの境界領域に、高耐圧pMISQHp1のソースおよびドレイン用のp+型の半導体領域P1,P1とは逆の導電型のn+型の半導体領域NVkを、高耐圧pMISQHp1の電界緩和機能を持つp−型の半導体領域PV1,PV1(特にドレイン側)に接しないように、そのp−型の半導体領域PV1,PV1から離れた位置に配置した。このn+型の半導体領域NVkは、溝型の分離部3よりも深い位置まで延在されている。

(もっと読む)

不純物活性化方法、半導体装置の製造方法

【課題】低いシート抵抗を得る不純物活性化方法、および、ソース・ドレイン拡張部を均一な深さで再現性よく形成する製造方法を提供。

【解決手段】半導体基板21において半導体基板21よりも不純物濃度が高いボロンイオン注入層43が形成されており、ボロンイオン注入層43にパルス幅が10〜1000フェムト秒のパルスレーザー光を照射して、ボロンイオン注入層43を活性化させる。パルスレーザー光におけるパルス幅、レーザーフルーエンスおよび照射パルス数を含む照射条件を変更することにより、パルスレーザー光照射後のボロンイオン注入層43のシート抵抗を制御する。

(もっと読む)

半導体装置

【課題】 従来の比例縮小側(係数α、α>1)を適用した平面型MOSTのしきい電圧のばらつきの標準偏差σ(VT)が、微細化とともに、すなわちαを大きくするとともに大きくなり、動作電圧が低くできないという問題がある。

【解決手段】 フィンの高さをチャンネル長よりも高くしたFinFET構造によって上記の問題を解決する。

(もっと読む)

半導体装置の製造方法

【課題】微細化が進んでも適切な歪を生じさせることができる半導体装置の製造方法を提供する。

【解決手段】nチャネルトランジスタ形成予定領域51nを覆う部分を残しながら絶縁膜6のエッチバックを行うことにより、pチャネルトランジスタ形成予定領域51p内のゲート電極4の側方にサイドウォール6aを形成する。サイドウォール6aをマスクとして半導体基板1の表面にp型不純物を導入してp型不純物導入領域8pを形成し、サイドウォール6aをマスクとしてp型不純物導入領域8pの表面に溝9を形成する。溝9内にSiGe層10を成長させる。絶縁膜6のエッチバックを行うことにより、nチャネルトランジスタ形成予定領域51n内のゲート電極4の側方にサイドウォールを形成し、nチャネルトランジスタ形成予定領域51n内において、このサイドウォールをマスクとして半導体基板1の表面にn型不純物を導入してn型不純物導入領域を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】同一の工程で、同一半導体基板上に異なる構造のトランジスタを形成する半導体装置の提供。

【解決手段】半導体基板上に第一及び第二のゲート電極40,41を形成する工程と、第一のゲート電極の側壁面に第一の絶縁層122を形成するとともに、第二のゲート電極のゲート幅方向両側の半導体基板上にエピタキシャル成長層9aを形成する工程と、第二のゲート電極の側壁面に第二の絶縁層を形成する工程と、第一の絶縁層及び第二の絶縁層を覆うように第三の絶縁層を形成する工程と、第二の絶縁層を覆う第三の絶縁層を除去する工程と、第一のゲート電極のゲート幅方向両側の半導体基板及びエピタキシャル成長層にそれぞれ不純物を拡散させて、第一及び第二の不純物拡散領域6,8を形成する工程と、第一及び第二の不純物拡散領域にコンタクトプラグ12,15を接続させる工程と、を具備してなることを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置および降伏電圧の決定方法

【課題】 統合型のインテリジェントスイッチデバイス、複統合型の入力信号・伝達ICまたは統合型のパワーICなどに用いられる横型MOSFETにおいて、複雑な分離構造を用いずに、より小さいチップ面積でESD耐量およびサージ耐量を高くすること。

【解決手段】 同一基板上に形成され、並列接続されたトランジスタおよびダイオードを備えた半導体装置において、前記トランジスタの降伏動作時の抵抗より前記ダイオードの降伏動作時の抵抗を小さく、かつ、前記トランジスタの二次降伏電流より前記ダイオードの二次降伏電流を大きくする。

(もっと読む)

超高品質シリコン含有化合物層の形成方法

【課題】ALDがCVDに比べて優れたコンフォーミティ(coformality)、成膜速度及び均一性を備えた気相堆積方法を提供する。

【解決手段】シリコンナイトライド層を含む、超高品質シリコン含有化合物層を形成するため、複数の順次的なステップ140が、反応チャンバー中で実施される。好ましい実施態様において、シリコン前駆物質としてトリシランを用いて、シリコン層が基板上に堆積100される。シリコン前駆物質は、反応チャンバーから除去される110。その後、シリコンナイトライド層が、シリコン層を窒化すること120によって形成される。窒素反応物質は、反応チャンバーから除去される110。これらのステップ100、110、120及び130を繰り返すことによって、所望の厚さのシリコンナイトライド層が形成される。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極中の不純物がゲート絶縁膜を突き抜けてチャネル領域に拡

散するのを抑制し、ソース・ドレイン領域の不純物イオンが部分的にチャネル領

域方向に異常拡散するのを防ぐ。

【解決手段】ゲート絶縁膜3上に、ポリシリコン膜4を被着してゲート電極5

パターンにパターンニングした後、ソース・ドレイン領域9を形成する前に、窒

素を含む雰囲気中で窒化処理を行って、ゲート電極5端部付近のゲート絶縁膜3

中に新たに窒素を導入する。または、ゲート電極5のパターンニング後、ソース

・ドレイン領域9を形成する前に、酸化処理を行うことによってゲート電極5の

パターンニングの際に生じるダメージや汚染の一部を酸化膜中に取り込んで基板

から除去する。その後、窒化処理を行うことにより、酸化処理によってゲート電

極5端部付近に形成され、ダメージを含む酸化膜に積極的に窒素を導入する。

(もっと読む)

121 - 140 / 812

[ Back to top ]