Fターム[5F140AC23]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 動作、用途、素子構造 (4,642) | 縦型トランジスタ(縦型DMOSなど) (291)

Fターム[5F140AC23]の下位に属するFターム

縦型IGBT (35)

Fターム[5F140AC23]に分類される特許

1 - 20 / 256

半導体装置の製造方法

【課題】縦型トランジスタにおける上部拡散層の深さ方向のばらつきを低減することのできる半導体装置の製造方法を提供する。

【解決手段】本発明は表面が平坦なシリコン層からなる上部拡散層11を形成しようとするものであり、具体的には、ファセットを有するシリコン層を選択的に過剰成長させた後、層間絶縁膜7表面に形成されたシリコン層をCMPで擦り切ってシリコン層の表面を平坦化する。シリコン層の成長は、シリコン層を単結晶シリコンで選択的にエピタキシャル成長させる。この場合、ファセットが生じるので、最も成長が遅いファセットが層間絶縁膜表面より上方に位置するまで充分過剰に成長させる。

(もっと読む)

半導体装置の製造方法

【課題】縦型トランジスタのソース又はドレイン用の拡散層を形成するにあたって形成されるシリコン膜に表面凹凸を発生させない半導体装置の製造方法を提供する。

【解決手段】複数の半導体ピラーを形成する工程と、隣り合う前記半導体ピラーで挟まれた溝の側面を覆うように絶縁膜を形成する工程と、前記絶縁膜の前記溝の底部に近い領域に側面開口を形成する工程と、前記溝の内部を覆うようにシリコン膜からなる被覆膜を形成する工程と、前記被覆膜上に前記半導体ピラー内へ拡散させる不純物で構成された不純物層を形成する工程と、前記不純物を、前記側面開口を塞ぐように形成されている前記被覆膜を通して前記半導体ピラー内に熱拡散させてソース又はドレイン用の拡散層を形成する工程と、を含む。前記被覆膜の成膜温度を510℃より高く度550℃未満の範囲とすることにより、非晶質状態のシリコン膜を形成する。

(もっと読む)

電界効果トランジスタの製造方法および電界効果トランジスタ

【課題】ドーピング密度を増やすことなく、高濃度キャリア走行部を形成でき、高い移動度と低いオン抵抗を実現できる電界効果トランジスタの製造方法および電界効果トランジスタを提供する。

【解決手段】この電界効果トランジスタ1は、窒素ドープn型SiCドリフト層12のキャリア走行部14を挟むように形成されたソース13とドレイン15とを備える。ソース13とドレイン15は、エッチングによってキャリア走行部14に隣接して形成された段部16,17を有する。キャリア走行部14は、段部16,17の段差面16A,17Aに紫外光を照射することによって段部16,17から延びるように形成された積層欠陥部18を有する。積層欠陥部18は、3C‐SiCの結晶構造を持ち、量子井戸構造のようにふるまうことからキャリアがここに多数閉じ込められる。

(もっと読む)

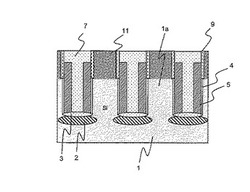

半導体装置およびその製造方法

【課題】同一平面上に形成された2つの配線が互いにショートするのを回避すること。

【解決手段】第1の方向(X)に複数本並べて配置された活性領域(50)の各々は、第1の方向(X)と直交する第2の方向(Y)に離間して配置された2つの縦型トランジスタ(51)と、この2つの縦型トランジスタ(51)の間に位置する縦型のゲート電極用ダミーピラー(1a)と、から成る。半導体装置(100)は、複数本の活性領域(50)の中央に位置するゲート電極用ダミーピラー(1a)へ給電するために第1の方向(X)へ延在して配置されたゲート給電配線(23)と、2つの縦型トランジスタ(51)間を接続するために、第2の方向(Y)に延在し、かつゲート給電配線(23)を迂回するように構成されたトランジスタ間接続配線(21、10A、16)と、を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】トランジスタ間接続配線が吊りワード線と短絡してしまうのを回避すること。

【解決手段】第1の方向(X)に複数本並べて配置された活性領域(50)の各々は、第1の方向(X)と直交する第2の方向(Y)に離間して配置された2つの縦型トランジスタ(51)と、この2つの縦型トランジスタ(51)の間に位置するピラー(1a)と、から成る。半導体装置(100)は、複数本の活性領域(50)の中央の位置で、第1の方向(X)へ延在して配置された吊りワード線(23)と、2つの縦型トランジスタ(51)間を接続するために、第2の方向(Y)に延在し、かつ吊りワード線(23)を迂回するように構成されたトランジスタ間接続配線(21、10A、16)と、を備える。

(もっと読む)

半導体装置

【課題】トンネル型FETのオン電流とオフ電流との比と、単位基板面積あたりのオン電流を増大させる。

【解決手段】実施形態によれば、半導体装置は、半導体基板と、前記半導体基板上に絶縁膜を介して形成されたゲート電極と、前記ゲート電極の側面に形成されたゲート絶縁膜とを備える。さらに、前記装置は、前記半導体基板上に順に積層された第1導電型の下部主端子層と、中間層と、第2導電型の上部主端子層とを有し、前記ゲート絶縁膜を介して前記ゲート電極の側面に形成された積層体とを備える。さらに、前記上部主端子層は、前記ゲート電極の側面に、前記ゲート絶縁膜と半導体層を介して形成されている。

(もっと読む)

半導体装置の製造方法

【課題】エピタキシャル成長後に不純物を導入するためのイオン注入工程を省略する。また、エピタキシャル成長層の厚さがばらついた場合であっても、ピラー部にまで不純物が導入されることによるトランジスタ特性の変動を防止する。

【解決手段】基板の主面にシリコンピラーを形成した後、シリコンピラーの下の基板内に、シリコンピラーと逆導電型の第1の拡散層を形成する。シリコンピラーの側面にゲート絶縁膜を介してゲート電極を形成する。次に、シリコンピラーの上面上に不純物を含むシリコンをエピタキシャル成長させることで、シリコンピラーと逆導電型の第2の拡散層を形成する。

(もっと読む)

半導体装置

【課題】トランジスタの電流駆動力増大を図りつつ、オフリーク電流を低減させる。

【解決手段】半導体突出部2は、半導体基板1上に形成されている。ソース/ドレイン層5、6は、半導体突出部2の上下方向に設けられている。ゲート電極7、8は、半導体突出部2の側面にゲート絶縁膜4を介して設けられている。チャネル領域3は、半導体突出部2の側面に設けられ、ドレイン層6側とソース層5側とでポテンシャルの高さが異なっている。

(もっと読む)

半導体装置及びその駆動方法

【課題】閾値電圧(Vth)の経時的に変動する現象を抑制することで、高信頼性を保つことが可能なMIS型半導体装置を提供する。

【解決手段】本発明は、半導体ボディ領域とゲート絶縁膜の間に半導体ボディ領域とは逆の半導体極性のチャネル層を有するMIS型半導体装置であり、当該半導体装置のフラットバンド電圧Vfbを−10ボルト以下とすることにより、半導体ボディ領域表面近傍に誘起されるキャリア電荷密度を当該半導体装置の動作保証範囲内において所定量以下に抑制する。

(もっと読む)

半導体装置

【課題】微細CMOSと中高耐圧MOSFETとの混載を前提とする集積回路(半導体装置)において、中高耐圧MOSFETのチャネル長やしきい値電圧のばらつきを抑制して、設計仕様どおりの安定した回路動作の実現や出力電流密度の向上を図ることができる技術を提供する。

【解決手段】本発明における特徴は、チャネル領域CHの幅(チャネル長)を小さくしたことにある。具体的には、ゲート電極Gと平面的に重なるチャネル領域CHの幅をLとし、ゲート電極Gの厚さをtとした場合、チャネル領域CHの幅Lが、ゲート電極Gの厚さtの1/5倍以上1倍以下になるようにチャネル領域CHを形成する。これにより、チャネル領域CHの幅Lを小さくすることができ、しきい値電圧のばらつきを小さくすることができる。

(もっと読む)

炭化珪素半導体を用いたMOS構造およびその酸化膜形成方法

【課題】 SiO2/SiC界面における界面準位自体を低減することが出来るSiC半導体を用いたMOS構造、およびその酸化膜の形成方法を提供する。

【解決手段】 SiC半導体基板1を処理炉内に用意し、処理炉内を比較的低い700℃に設定して、SiC半導体基板1の基板表面を酸素ガス雰囲気中にさらす。この熱酸化により、SiC半導体基板1の基板表面には、SiO2から成る中間層2が約1nmの極薄い厚さで形成される。次に、中間層2上にSiO2膜を約50nmの厚さに堆積して、SiO2から成る堆積層3を形成する。次に、SiC半導体基板1が酸化しない温度および時間で、堆積層3をアニーリングする。このアニーリングは、赤外線ランプなどの急速加熱装置により、SiO2膜の融点である1200℃に近い、この1200℃の融点よりも低い例えば1000〜1100℃程度の温度で、短時間に急速に行われる。

(もっと読む)

半導体装置、金属膜の製造方法及び半導体装置の製造方法

【課題】高集積化することができる半導体装置、金属膜の製造方法及び半導体装置の製造方法を提供することである。

【解決手段】実施形態に係る半導体装置は、半導体基板と、前記半導体基板に形成され、ヒ素を含むヒ素拡散層と、前記ヒ素拡散層上に形成された金属膜と、を備える。前記金属膜は、タングステン、チタン、ルテニウム、ハフニウム及びタンタルからなる群より選択された少なくとも1種の金属、並びにヒ素を含む。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】チャネル移動度の低下を抑制しつつ閾値電圧を制御する炭化珪素半導体装置の製造方法の提供を目的とする。

【解決手段】本発明の炭化珪素半導体装置の製造方法は、(b)二酸化珪素膜が形成された炭化珪素基板を窒化処理する工程と、(c)窒化処理された炭化珪素基板を水蒸気を含んだ酸素雰囲気で熱処理する工程とを備える。工程(c)は、(c1)窒化処理された炭化珪素基板を投入した熱処理炉の温度を不活性ガス雰囲気中で昇温又は降温する工程を含む。工程(c1)は、窒化処理直後のチャネル移動度をμch、昇温又は降温開始時刻をt=0、熱処理開始時刻をt=t1、熱処理終了時刻をt=t2、熱処理炉からの基板取出時刻をt=t3、ボルツマン定数をk、時刻tにおける熱処理炉の温度をT(K)とした場合に、式(1)により求められる炭化珪素基板中のチャネル移動度の低下率が10%以下となるように昇温速度及び/又は降温速度を決定する。

(もっと読む)

半導体装置の製造方法

【課題】界面準位密度およびフラットバンド電圧がともに良好な界面特性を有する半導体装置の製造方法を提供すること。

【解決手段】まず、炭化珪素基板1の表面を洗浄する(ステップS1)。つぎに、原料ガスをECRプラズマ化し、原料ガスに含まれる原子を炭化珪素基板1に照射することで、炭化珪素基板1の表面にシリコン窒化膜2を成長させる(ステップS2)。つぎに、ECRプラズマ化学気相成長法により、シリコン窒化膜2の表面にシリコン酸化膜3を堆積する(ステップS3)。つぎに、窒素雰囲気中で、シリコン窒化膜2およびシリコン酸化膜3が形成された炭化珪素基板1のアニール処理を行う(ステップS4)。

(もっと読む)

半導体素子及び半導体素子の製造方法

【課題】ドレイン電極とドレイン層とのコンタクト抵抗を低減できる半導体素子及び半導体素子の製造方法を提供する。

【解決手段】半導体素子は、第1導電型のドレイン層と、ドレイン層上に形成された第1導電型のドリフト層と、ドリフト層上に選択的に形成された第2導電型のベース層と、ベース層上に選択的に形成された第1導電型のソース層と、ゲート絶縁膜を介して、ドリフト層、ベース層及びソース層に跨って形成されたゲート電極と、ベース層及びソース層に電気的に接続されたソース電極と、ドリフト層を貫通して、底部の少なくとも一部がドレイン層にまで達する第1のトレンチ内に形成され、ドレイン層と電気的に接続されたドレイン電極と、を備え、底部には、凹凸が形成されている。

(もっと読む)

半導体装置

【課題】横型構造のパワートランジスタにおいて、寄生サイリスタのラッチアップ耐量を改善するとともに、ターンオフ時間を短縮する。

【解決手段】エミッタ電極(21)下部に設けられるn+エミッタ層(6)を、所定の間隔で互いに離れて配置される単位領域(60)で構成する。単位領域においてエミッタ電極とのコンタクトを取るとともに、pベース層(5)よりも高濃度でp+層(45)を少なくともエミッタ層の下方に設ける。

(もっと読む)

ドリフト領域とドリフト制御領域とを有する半導体素子

【課題】低いオン抵抗を有するドリフト経路/ドリフト領域を有する、パワー半導体素子を提供する。

【解決手段】半導体基材内に第1の伝導型のドリフト領域2と、半導体基材内にドリフト領域2に隣接して配置され半導体材料からなるドリフト制御領域3と、ドリフト領域2とドリフト制御領域3の間に配置された蓄積誘電体4と、基材領域8と、基材領域8から分離され蓄積誘電体4に隣接するドレイン領域5と、基材領域8によりドリフト領域2から分離されるソース領域9と、ゲート誘電体16により半導体基材から絶縁されソース領域9からドリフト領域2に到るまで基材領域8に隣接して伸びたゲート電極15と、ドレイン領域5と接したドレイン電極11と、ドレイン領域5と相補的にドープされた半導体領域27とを含み、半導体領域27はドレイン電極11とドリフト領域2の間に配置されドレイン電極11に隣接する。

(もっと読む)

シンクロナス整流器或いは電圧クランプ用の3端子パワーMOSFETスイッチ

【課題】パワー変換器に於けるシンクロナス整流器として適するMOSFETスイッチを提供する。

【解決手段】互いに接続されソース及びボディが、ドレンよりはより正の側に高い電圧にバイアスされたN−チャネルパワーMOSFETを製造する。ゲートはスイッチ(1184)により制御され、ゲートを、ソース及び当該MOSFETのチャネルを完全にオンにするのに十分な電圧(VCP)のいずれか一方に選択的に接続する。ゲートがソースに接続されたとき、デバイスは、比較的低い電圧でオンし、従来のPN接合よりは低い導通抵抗を有する「擬似ショットキー」ダイオードとして機能する。ゲートが、前記した正の電圧に接続されたとき、MOSFETのチャネルは完全にオンとなる。このMOSFETスイッチは、電力損及び“break-before-make”時間に於ける蓄積電荷を低減する。

(もっと読む)

半導体装置

【課題】 オン抵抗の増大を抑制しつつ、耐圧の低下を抑制する技術を提供する。

【解決手段】 ノーマリオフ型の半導体装置100は、ヘテロ接合を構成する半導体層16と、第1リセス部8と、第1リセス部8よりも浅い第2リセス部4と、ゲート部5を備えている。半導体層16は、第1半導体層12と、第1半導体層12上に設けられているとともに第1半導体層12よりもバンドギャップが広い第2半導体層14を有している。第2リセス部4は、第2半導体層14を貫通していない。第2リセス部4の下方に位置する第2チャネル部C2は、第1リセス部8の下方に位置する第1チャネル部C1よりも電流経路20の上流側に配置されている上流側第2チャネル部C2uを有する。

(もっと読む)

炭化珪素半導体基板、炭化珪素半導体装置、炭化珪素半導体基板の製造方法および炭化珪素半導体装置の製造方法

【課題】高品質な単結晶SiC基板の使用量を減らすことが可能であり、信頼性を向上させることができるSiC半導体装置の製造方法を提供することを目的とする。

【解決手段】支持基板1として、単結晶SiCと異なる材料を用いて構成され、かつ活性層3を形成する工程および半導体素子の構成要素4〜10、14〜17を形成する工程における温度以上の耐熱性を有するものを用い、接合工程では、半導体素子の動作温度以下の温度で直接接合する。このような製造方法では、支持基板1と単結晶SiC基板11とを半導体素子の動作温度以下の温度で接合しているため、支持基板1と単結晶SiC基板11との接合界面で発生する応力を小さくすることができ、SiC半導体装置が使用される際に半導体素子に印加される応力を小さくすることができる。すなわち、SiC半導体装置の信頼性が低下することを抑制することができる。

(もっと読む)

1 - 20 / 256

[ Back to top ]