Fターム[5F140AC30]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 動作、用途、素子構造 (4,642) | 素子配置 (40)

Fターム[5F140AC30]に分類される特許

1 - 20 / 40

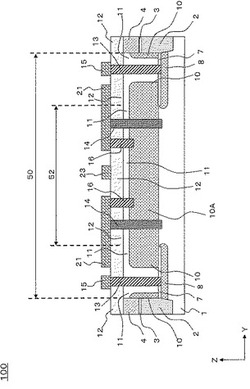

半導体装置およびその製造方法

【課題】同一平面上に形成された2つの配線が互いにショートするのを回避すること。

【解決手段】第1の方向(X)に複数本並べて配置された活性領域(50)の各々は、第1の方向(X)と直交する第2の方向(Y)に離間して配置された2つの縦型トランジスタ(51)と、この2つの縦型トランジスタ(51)の間に位置する縦型のゲート電極用ダミーピラー(1a)と、から成る。半導体装置(100)は、複数本の活性領域(50)の中央に位置するゲート電極用ダミーピラー(1a)へ給電するために第1の方向(X)へ延在して配置されたゲート給電配線(23)と、2つの縦型トランジスタ(51)間を接続するために、第2の方向(Y)に延在し、かつゲート給電配線(23)を迂回するように構成されたトランジスタ間接続配線(21、10A、16)と、を備える。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】装置面積を増大させることなく、保護素子を有する半導体装置を提供する。

【解決手段】P型のIII族窒化物半導体からなる第1P型層200と、第1P型層200の一部上には、ゲート絶縁膜420およびゲート電極440とが設けられている。第1P型層200内のうち、ゲート電極440の両脇には、N型のソース領域340およびドレイン領域320が設けられている。また、第1P型層200の下には、N型のIII族窒化物半導体からなる第1N型層100が設けられている。基板内には、N型のIII族窒化物半導体とオーミック接続する材料からなるオーミック接続部(たとえばN型GaN層520)が、ソース領域340および第1N型層100と接するように設けられている。また、ドレイン電極600は、ドレイン領域320および第1P型層200と接するように設けられている。

(もっと読む)

半導体装置とその製造方法

【課題】基板の反りとドレイン抵抗を低減させながら、半導体装置側面のバリや半導体装置の損傷を抑制することを目的とする。

【解決手段】半導体基板1裏面の表面電極であるソース電極2、ドレイン電極3の裏面に相当する領域に窪み部6を設け、ダイシング領域以外の窪み部6や窪み部6間に金属層5を形成することにより、基板の反りとドレイン抵抗を低減させながら、半導体装置側面のバリや半導体装置の損傷を抑制することができる。

(もっと読む)

半導体装置

【課題】放熱効率が高く低コストでの実装が可能な半導体装置を提供する。

【解決手段】第1の方向に延在するゲート電極を有する複数のトランジスタを有し、複数のトランジスタが第1の方向と交差する第2の方向に配置されたトランジスタアレイ54と、トランジスタアレイの第1の方向に配置され、複数のトランジスタのソース領域に電気的に接続されたパッド電極50とを有する。

(もっと読む)

半導体装置

【課題】複雑な形状を有しながらも応力分布のばらつきが少ない活性領域を有する半導体装置を提供する。

【解決手段】一実施の形態による半導体装置は、素子分離領域を有する基板と、前記素子分離領域に分離された、不純物拡散領域を有する前記基板上の複数の四角形の活性領域と、前記複数の活性領域の集合からなり、段差を含む輪郭形状を有する大活性領域とを有する。前記複数の活性領域の前記不純物拡散領域のうち、前記素子分離領域を挟んで向かい合う不純物拡散領域は、電気的に接続される。

(もっと読む)

電力増幅器

【課題】 電力増幅器に発生するホットキャリアの影響を抑制する。

【解決手段】 一つの実施形態の電力増幅器には、半導体層に形成され、少なくとも1つ以上から構成され、電力増幅動作する第1のグロースリングゲート構造体と、半導体層に形成され、第1のグロースリングゲート構造体を取り囲むように隣接配置され、第1の構造体が電力増幅動作するときに、逆バイアスが印加されて空乏化領域が形成され、第1の構造体を周囲からアイソレートする複数の第2のグロースリングゲート構造体とが設けられる。

(もっと読む)

絶縁ゲート型半導体素子及び絶縁ゲート型半導体集積回路

【課題】耐放射線性を有する絶縁ゲート型半導体素子、絶縁ゲート型半導体集積回路を提供する。

【解決手段】一部がチャネル領域をなすp型の半導体層11と、半導体層11の上部に活性領域21Bを定義する素子分離絶縁膜21と、チャネル領域にキャリア注入口を介してキャリアを注入するn型の第1主電極領域12と、チャネル領域から、キャリアを排出するキャリア排出口を有するn型の第2主電極領域13と、活性領域21Bの上に設けられたゲート絶縁膜22と、ゲート絶縁膜22の上に設けられ、第1主電極領域12と第2主電極領域13との間を流れるキャリアの流路に直交する主制御部、主制御部に交わる2本のガード部241,242を有してπ字型をなすゲート電極24と、第2主電極領域13のゲート幅方向の両端側に設けられたp型のリーク阻止領域61,62とを備える。

(もっと読む)

静電気放電保護装置及び方法

【課題】静電気放電保護装置及び方法を提供する。

【解決手段】本発明の実施例は、静電気放電(ESD)保護装置、及び、ESD保護装置を形成する方法に関する。一実施例は、ESD保護装置で、基板に配置されたpウェルと、基板に配置されたnウェルと、基板中のpウェルとnウェルの間に配置された高電圧nウェル(HVNW)と、pウェルに配置されたソースn+領域と、nウェルに配置された複数のドレインn+領域と、からなる。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置におけるトランジスタの熱破壊を防止し得るとともに、安全動作領域(SOA)を拡大しトランジスタ設計の自由度を高め得る半導体装置及びその製造方法を提供すること。

【解決手段】 トランジスタセルを並列にチップ内に均一に配置した半導体装置において、チップの面中央部にトランジスタセルの不動作領域を形成する。不動作領域を形成手段として、1)ソースとドレインのn型拡散層を設けない方法 2)ソースとドレインのコンタクト窓を開けない方法 3)ゲート電極を分岐してソースに接続する方法を採る。また、不動作領域の形成に代えて当該領域のトランジスタセルの閾値電圧を高くして動作電流を低くする手段を採ることもできる。

(もっと読む)

半導体装置

【課題】トランジスタ対を有する半導体装置において、回路面積の増大を抑えつつ、対をなすトランジスタの特性のアンバランスを抑制する。

【解決手段】トランジスタ1a,1bは活性領域パターンが互いに同一である領域A1a,A1bを有し、トランジスタ2a,2bは活性領域パターンが互いに同一である領域A2a,A2bを有する。トランジスタ2a,2bの活性領域13a,13bは、チャネル長方向の長さがトランジスタ1a,1bの活性領域11a,11bよりも長く、領域A2a,A2bは領域A1a,A1bよりもチャネル長方向の幅が狭い。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】インパクトイオン化領域にてキャリアがゲート絶縁膜に入り込むことがない半導体装置とその製造方法を提供する。

【解決手段】トランジスタ部分22と、ダイオード部分23を具備し、トランジスタ部分22は、第1導電型又は真性の半導体領域であるチャネル形成領域6と、チャネル形成領域6に接するゲート絶縁膜7と、チャネルを形成させるゲート電極8と、第2導電型あり、チャネル形成領域6に接し、ドレイン電圧が供給されるドレイン領域4と、第2導電型であり、チャネル形成領域6を介してドレイン領域4に対向し、チャネル形成領域6にチャネルが形成されたときにチャネル形成領域6を介してドレイン電圧が供給されるソース領域5とを含み、ダイオード部分23は、ソース領域5に電気的に接続されており、ソース領域5にドレイン電圧が供給されたときに、ダイオード部分23はインパクトイオン化現象が発生する領域を含む。

(もっと読む)

ESD保護素子及びその製造方法

【課題】LSI製造工程の最終段階においても、内部素子の基本性能を変えることなく、内部素子と同一プロセスで形成されたESD保護素子のブレークダウン電圧を調整可能とすることを目的とする。

【解決手段】MOS構造のドレイン領域とMOS構造を囲む素子分離領域との間にドレイン領域に接してこれとPN接合を形成する接合形成領域を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】ニッケルシリサイド層上の絶縁膜の応力を規定することで、膜剥がれの防止を可能とする。

【解決手段】半導体基板11に形成された素子分離領域12と、前記素子分離領域12で分離された前記半導体基板11の第1素子形成領域13に形成されたP型電界効果トランジスタ2と、前記素子分離領域12で分離された前記半導体基板11にニッケルシリサイド層29が形成され、該ニッケルシリサイド層29上からヒ素イオン注入されたN型基板領域14と、前記P型電界効果トランジスタ2上を被覆する圧縮応力を有する第1絶縁膜41と、前記N型基板領域14上を被覆していて引張応力もしくは前記圧縮応力よりも小さい圧縮応力を有する第2絶縁膜42とを有することを特徴とする。

(もっと読む)

高耐圧半導体スイッチング素子

【課題】センス比のコレクタ電流依存性をスイッチング素子自体の構造により制御する。

【解決手段】P型のベース領域2の表面部に、少なくとも1つのN型のエミッタ領域3及びエミッタ領域3と離隔した少なくとも1つのN型のセンス領域5が選択的に形成されている。エミッタ領域3及びセンス領域5は、コレクタ領域7からベース領域2に向かう第1の方向に対して垂直な第2の方向に並ぶように配置されている。センス比がコレクタ電流の変化に対応して所望の変化を生じるように、第2の方向におけるセンス領域5、エミッタ領域3、センス領域5に隣接する部分のベース領域2、及びエミッタ領域3に隣接する部分のベース領域2のそれぞれの幅が設定されている。

(もっと読む)

半導体装置

【課題】MOSトランジスタを有する半導体装置であって、エリアパッド下のMOSトランジスタの特性変動を抑制することが可能な半導体装置を提供する。

【解決手段】MOSトランジスタとエリアパッドを有する半導体装置10であって、結晶方位面<110>を表面とするシリコンを材料とする半導体チップ11と、ソース領域、ゲート領域及びドレイン領域がシリコンの結晶方位<110>の方向に並び、半導体チップ11内に形成される複数のMOSトランジスタ12と、半導体チップ11上のエリアパッドとして2次元状に形成された複数の接合用電極パッド13と、複数の接合用電極パッド13それぞれの上に形成された接合用バンプ14とを備え、複数の接合用電極パッド13は、その中心点が結晶方位<110>の方向に対して斜めの方向に並ぶことを特徴とする。

(もっと読む)

半導体集積回路装置

【課題】素子分離部の分離幅を調整することによって、所望する特性を有するMISFETを得ることのできる技術を提供する。

【解決手段】素子分離部4の分離幅Laおよび分離幅La’を相対的に狭くすることにより、第2MISFETQ2のチャネル領域へ及ぼす応力の影響を大きくして、しきい値電圧の変化を相対的に大きくし、素子分離部4の分離幅Lbおよび分離幅Lb’を相対的に広くすることにより、第4MISFETQ4のチャネル領域へ及ぼす応力の影響を小さくして、しきい値電圧の変化を相対的に小さくする。

(もっと読む)

窒化物半導体素子

【課題】ノーマリオフ動作を実現することができるとともに、所望のゲート閾値電圧を実現することができる、窒化物半導体素子(HEMT)を提供すること。

【解決手段】このHEMTは、真性GaN層3およびn型AlGaN層4が積層された窒化物半導体積層構造部2を備えている。窒化物半導体積層構造部2は、ストライプ状の線状部10と、島状の合流部11とを備えている。複数本の線状部10は、隣接する線状部10との間に形成されたストライプ状のトレンチ6によって、互いに分離されている。線状部10においてトレンチ6内に露出した積層境界7には、ゲート絶縁膜12を介してゲート電極13が対向している。また、n型AlGaN層4には、ソース側合流部11Sおよびドレイン側合流部11Dにおいて、ソース電極14およびドレイン電極15がそれぞれ接触形成されている。

(もっと読む)

高周波電力増幅器および携帯型無線端末

【課題】動作時の出力低下が少なく、熱雑音の影響が少なく、高周波動作が安定で、かつ信頼性に優れた高周波電力増幅器および携帯型無線端末を提供することを可能にする。

【解決手段】半導体基板上に並列に配置され、それぞれがソース電極、ゲート電極、およびドレイン電極を有する複数のMOSトランジスタと、前記複数のMOSトランジスタのうち隣接するMOSトランジスタ間に設けられた短絡した導体からなる閉ループと、を備え、前記複数のMOSトランジスタのソース電極、ゲート電極、およびドレイン電極はそれぞれ並列に接続されている。

(もっと読む)

半導体装置

【課題】ドレイン電圧のオーバーシュートを低減してノイズとスイッチング損失の増大を抑制することが可能な半導体装置であって、特に、高速スイッチングが可能な横型MOSトランジスタを用いた、小型で安価な半導体装置を提供することを目的としている。

【解決手段】半導体基板10の表層部に、横型MOSトランジスタ21が形成されてなる半導体装置であって、横型MOSトランジスタ21のゲート駆動信号ラインに、横型MOSトランジスタ21のドレイン(D)と逆の導電型の多結晶シリコン抵抗体50が挿入配置され、絶縁膜4を介して、横型MOSトランジスタ21のドレイン電圧が多結晶シリコン抵抗体50に印加されてなる半導体装置100とする。

(もっと読む)

半導体装置

【課題】従来の半導体装置では、半導体素子が自己加熱により熱破壊するという問題があった。

【解決手段】本発明の半導体装置では、MOSトランジスタ1の中央領域に非活性領域6が配置されている。非活性領域6には、ドレイン領域3、ソース領域4及びゲート電極5が配置されていない。この構造により、非活性領域6では、MOSトランジスタ1の電流が流れることがなく、自己加熱による温度上昇が大幅に低減される。そして、MOSトランジスタ1が、自己加熱により熱破壊することを抑止することができる。

(もっと読む)

1 - 20 / 40

[ Back to top ]