Fターム[5F140AC36]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 動作、用途、素子構造 (4,642) | 薄膜トランジスタ、TFT、SOI、SOS (1,150)

Fターム[5F140AC36]に分類される特許

61 - 80 / 1,150

半導体シリコン膜及び半導体デバイス、並びにそれらの製造方法

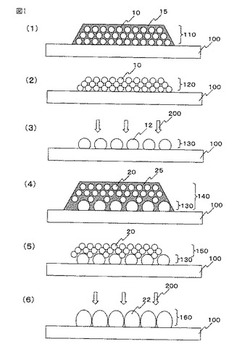

【課題】本発明の目的は、新規な半導体シリコン膜及びそのような半導体シリコン膜を有する半導体デバイス、並びにそれらの製造方法を提供することである。

【解決手段】本発明の半導体シリコン膜(160)は、複数の細長シリコン粒子(22)が短軸方向に隣接してなる半導体シリコン膜である。ここでは、細長シリコン粒子(22)は、複数のシリコン粒子の焼結体である。また、このような半導体シリコン膜(160)を製造する本発明の方法は、第1のシリコン粒子分散体を、基材(100)上に塗布し、乾燥し、光(200)を照射して、第1の半導体シリコン膜(130)を形成する工程、第2のシリコン粒子分散体を、第1の半導体シリコン膜(130)に塗布し、乾燥し、光(200)を照射する工程を含む。ここで、この方法では、第1のシリコン粒子分散体の第1のシリコン粒子の分散が5nm2以上である。

(もっと読む)

二重仕事関数金属ゲート構造体及びその製造方法

【課題】二重金属ゲートを有する構造体において金属膜の仕事関数を調整する為の改善した方法および半導体素子を提供する。

【解決手段】半導体素子は単一金属膜に対し、NMOSにおいてはフッ素、PMOSにおいては炭素をそれぞれ選択的にドーピングすることによって形成される二重仕事関数の金属ゲート電極108’、109’を有する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】ゲート電極の側壁側にサイドウォールを精度よく形成することが可能な半導体装置の製造方法及び半導体装置を提供することを目的とする。

【解決手段】まず、SOI基板5の一方面側においてゲート電極34上及びゲート電極34の周囲の領域に第1絶縁膜40を形成する。次に、第1絶縁膜40上に積層させる構成で第1絶縁膜40とは材質の異なる第2絶縁膜42を形成する。そして、第1絶縁膜40及び第2絶縁膜42におけるゲート電極34の側壁34a側の部分を残しつつ、第2絶縁膜42よりも第1絶縁膜40のほうが、エッチング速度が遅くなるように第1絶縁膜40及び第2絶縁膜42を除去し、ゲート電極34の側壁34a側にサイドウォール45を形成する。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】FETのソース領域にショットキー電極を形成し、ゲート電極をソース電極の一部領域と窒化物半導体領域の一部に形成し、ドレイン電極と該ソース電極との間にフローティングガードリングを設けることによって、ノーマリ−オフで動作する半導体素子を提供する。

【解決手段】内部に2次元電子ガス(2DEG)チャネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ショットキー接合されたソース電極60と、ドレイン電極50とソース電極60との間で窒化物半導体層30にショットキー接合されたフローティングガードリング75と、ドレイン電極50とソース電極60との間及びソース電極60の少なくとも一部上にかけて形成された誘電層40と、誘電層40上に形成され、一部が、誘電層40を挟んでソース電極60のドレイン方向のエッジ部分上に形成されたゲート電極70とを含む。

(もっと読む)

電界効果トランジスタ

【課題】歪みチャネルを用いた場合のリーク電流を低減することができ、不良の発生を抑制して歩留まりの向上をはかる。

【解決手段】電界効果トランジスタであって、半導体基板10上に垂直に形成され、且つ第1の領域が第2の領域よりも高く形成された半導体フィン31と、第1の領域の両側面にゲート絶縁膜40を介して設けられたゲート電極50と、第2の領域に第1の領域の上端よりも低い位置まで設けられた、合金半導体からなるソース・ドレイン下地層63,73と、下地層63,73上に第1の領域の上部を挟むように設けられた、下地層63,73とは格子定数の異なるソース・ドレイン領域60,70とを備えている。チャネル領域には応力が付与され、下地層63,73は、空乏層が収まる厚さよりも厚く、熱平衡状態で結晶にミスフィット転位が導入される熱平衡臨界膜厚よりも薄く形成されている。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】FETのソース領域にショットキー電極を形成し、内部にオミックパターン電極を備え、ゲート電極をソース電極の一部領域と窒化物半導体領域の一部に形成することによって、ノーマリ−オフ動作すると共に高耐圧及び高電流で動作可能な、半導体素子及び製造方法を提供する。

【解決手段】内部に2次元電子ガス(2DEG)チャネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ドレイン電極50と離間され、窒化物半導体層30にショットキー接合されるソース電極60と、ドレイン電極50とソース電極60との間の窒化物半導体層30上及びソース電極60の少なくとも一部上にかけて形成された誘電層40と、ドレイン電極50と離間されるように誘電層40上に配設され、一部が誘電層40を挟んでソース電極60のドレイン方向のエッジ部分上部に形成されたゲート電極70とを含む。

(もっと読む)

半導体装置

【課題】オン抵抗が低く、かつ、Vthが高い半導体装置を提供する。

【解決手段】基板102の上方に、III−V族化合物半導体で形成されたバックバリア層106と、バックバリア層106上に、バックバリア層106よりバンドギャップエネルギーが小さいIII−V族化合物半導体で形成され、バックバリア層106の上方の少なくとも一部に設けられたリセス部122において、他の部分より膜厚が薄いチャネル層108と、チャネル層108にオーミック接合された第1の電極116,118と、少なくともリセス部においてチャネル層の上方に形成された第2の電極120と、を備える半導体装置を提供する。

(もっと読む)

III−V族トランジスタとIV族ダイオードを含む積層複合デバイス

【課題】III−V族トランジスタとIV族ダイオードからなる積層複合デバイスを提供する。

【解決手段】積層複合デバイスはIV族ダイオードと該IV族ダイオードの上に積層されたIII−V族トランジスタとを備える。IV族ダイオードのカソードがIII−V族トランジスタのソースと接触され、IV族ダイオードのアノードがIII−V族トランジスタのゲートに結合されて前記複合デバイスパッケージの底面上の複合アノードを与え、III−V族トランジスタのドレインが複合デバイスパッケージの底面に対向する上面上の複合カソードを与える。

(もっと読む)

半導体装置とその製造方法

【課題】 エッチングによるダメージを抑制しながら、ヘテロ接合面の近傍に負イオンを導入する技術を提供する。

【解決手段】 導入領域8上に保護膜30を形成する保護膜形成工程と、保護膜形成工程の後に、導入領域8を負イオンを含むプラズマに曝すプラズマ工程を備えている。保護膜30は、プラズマに対するエッチング速度が導入領域8よりも小さい。保護膜30には、負イオンを通過させることが可能な材料が用いられている。プラズマ中の負イオンは、保護膜30を通過し、導入領域8に導入される。

(もっと読む)

絶縁膜の製造方法

【課題】質量密度の高い絶縁膜の製造方法を提案すること。

【解決手段】絶縁膜の製造方法は、基板の上に絶縁膜を形成するステップと、その絶縁膜を処理するステップとを備えている。絶縁膜は、SiとOとを含んでおり、たとえばSiO2膜である。第2のステップでは、絶縁膜の温度を551℃以上574℃以下として、活性状態の希ガスと活性状態の酸素とを絶縁膜に供給する。

(もっと読む)

微細構造物の製造方法、該微細構造物の製造方法により製造される微細構造物、及び該微細構造物を有する電界効果型半導体素子

【課題】10nm程度の溝を有する微細構造物を安価で簡便かつ高精度に作製可能な微細構造物の製造方法、該微細構造物の製造方法により製造される微細構造物、及び該微細構造物を有する電界効果型半導体素子を提供すること。

【解決手段】本発明の微細構造物の製造方法は、トップダウン形成法により、基板上に少なくとも2つの凸状の形状からなる第1の構造体を形成する第1の構造体形成工程と、ボトムアップ形成法により、前記第1の構造体が形成された基板上に形成材料を堆積させ、隣接する前記第1の構造体の中間位置に凹状の溝を有する第2の構造体を形成する第2の構造体形成工程と、を含むことを特徴とする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】歩留まりに優れた半導体装置を提供する。

【解決手段】ゲート電極140は素子形成領域104に形成されている。サイドウォール層160は、ゲート電極140の側壁を覆っている。拡散領域170は素子形成領域104に位置する基板100に形成され、トランジスタ110のソース及びドレインとなる。絶縁層200は、素子形成領域104上、及びゲート電極140上に形成されている。コンタクト210は絶縁層200に形成され、拡散領域170に接続している。ゲート電極140のうちコンタクト210と隣に位置する部分は、サイドウォール層160より低く形成されている。絶縁層200は、ゲート電極140のうちコンタクト210と隣に位置する部分上かつ、サイドウォール層160同士の間に形成されている間隙に埋設される。

(もっと読む)

半導体装置

【課題】長期に亘って信頼性の高い横型MISFETを有する半導体装置を提供する。

【解決手段】本発明に係る半導体装置1は、半導体基板11上に形成された半導体層13と、半導体層13に溝状に形成され、その内壁が絶縁膜31で被覆され、絶縁膜31の内部にゲート電極32が埋設されたトレンチ溝30と、半導体層13上に、トレンチ溝30と少なくとも一部が対向配置する位置に形成されたゲート配線51と、ゲート配線51を挟むように半導体層13上に形成されたソース電極52、及びドレイン電極53とを具備する。半導体層13におけるオン動作時の電流経路は、ソース電極52とドレイン電極53の間の半導体層13の表面領域を実質的に経由せず、上記トレンチ溝30の側面近傍を経由する。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】ゲート絶縁膜界面材料としてGeO2 を用いた場合においてもGeO2 層の劣化を抑制することができ、素子の信頼性向上をはかると共に、プロセスの歩留まり向上をはかる。

【解決手段】本発明の実施形態による電界効果トランジスタは、Geを含む基板10上の一部に設けられた、少なくともGeO2 層を含むゲート絶縁膜20と、ゲート絶縁膜20上に設けられたゲート電極30と、ゲート電極30下のチャネル領域を挟んで前記基板に設けられたソース/ドレイン領域50と、前記ゲート絶縁膜20の両側部に形成された窒素含有領域25と、を備えた。

(もっと読む)

電界効果トランジスタ

【課題】急峻なS値特性を有するとともに、ソース/ドレイン領域が同じ導電型となる対称構造を有する電界効果トランジスタを提供する。

【解決手段】本実施形態による電界効果トランジスタは、半導体層と、前記半導体層に離間して設けられたソース領域およびドレイン領域と、前記ソース領域と前記ドレイン領域との間の前記半導体層上に設けられたゲート絶縁膜と、前記ゲート絶縁膜上に設けられたゲート電極と、前記ソース領域および前記ドレイン領域側の前記ゲート電極の少なくとも一方の側面に設けられた高誘電体のゲート側壁と、を備え、前記ソース領域および前記ドレイン領域は前記ゲート電極の対応する側面から離れている。

(もっと読む)

窒化物系半導体デバイス及びその製造方法

【課題】大電流かつ高耐圧な窒化物系半導体デバイスを提供する。

【解決手段】基板10と、基板10の上方に形成された電子走行層30と、電子走行層30上に形成された、電子走行層30とバンドギャップエネルギーの異なる電子供給層40と、電子供給層40上に形成されたドレイン電極80と、ドレイン電極80に流れる電流を制御するゲート電極70と、ゲート電極70をはさんでドレイン電極80の反対側に形成されたソース電極90とを備え、ゲート電極70とドレイン電極80との間の電子走行層30の表面には、2次元電子ガスの濃度が他の領域より低い複数の低濃度領域32が、互いに離れて形成されている、窒化物系半導体デバイス100。

(もっと読む)

半導体素子及び半導体素子形成方法

【課題】ゲルマニウムをチャネル材料とする金属/ゲルマニウムからなるソース/ドレイン構造を有する半導体素子を提供する。

【解決手段】半導体と金属とが接合してソース/ドレイン構造を形成する半導体素子において、ゲルマニウム(Ge)を3価元素(又は5価元素)でドーピングしたp型ゲルマニウム(又はn型ゲルマニウム)をチャネル2の材料とし、当該p型ゲルマニウム(又はn型ゲルマニウム)の任意の結晶面における原子配置と同一の原子配置である結晶面を有する金属3を、前記同一の原子配置である結晶面で接合して界面を形成し、当該形成された界面を用いたソース/ドレイン構造を有する。

(もっと読む)

窒化物半導体装置およびその製造方法

【課題】窒化物半導体を用いたノーマリーオフ動作の電界効果型トランジスタにおいて、閾値電圧が制御でき、十分な素子特性が得られるようにする。

【解決手段】c軸方向に結晶成長された窒化物半導体から構成されて主表面が極性面とされた第1領域121,第1領域121より厚く形成された第2領域122,および、第1領域121と第2領域122との間に形成されて主表面が半極性面とされた第3領域123を備える半導体層101を備える。また、窒化物半導体装置は、第1領域121における半導体層101の上に形成されたドレイン電極102と、第2領域122における半導体層101の上に形成されたソース電極103と、第3領域123における半導体層101の上に形成されたゲート電極104とを備える。

(もっと読む)

半導体装置の製造方法

【課題】チャネル領域に歪みを加える領域内の格子位置に存在する炭素量を多くすることができる半導体装置の製造方法を提供する。

【解決手段】半導体基板のうちゲート電極5両側にエクステンション領域7s、7d、ポケット領域8s、8dを形成し、ゲート電極5側面にサイドウォール9を形成し、半導体基板1のうちサイドウォール9、ゲート電極5から露出した領域をエッチングして凹部1s、1dを形成し、凹部1s、1d内に第3不純物を含む半導体層11s,11dを形成し、第1熱処理により第3不純物を活性化してゲート電極5の両側方にソース/ドレイン領域11s,11dを形成し、半導体層11s,11d内に炭素を有する第4不純物をイオン注入して半導体層11s,11dをアモルファス領域13s,13dとなし、第2熱処理によりアモルファス領域13s,13d内結晶の格子位置での炭素の結合性を高めてゲート電極5の両側方に歪発生領域14s,14dを形成する工程を有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【目的】水素終端よりも強い界面終端構造を有する半導体装置を提供することを目的の1つとする。

【構成】実施形態の半導体装置は、絶縁膜とSi半導体部とを備えている。絶縁膜は、酸化物と窒化物と酸窒化物とのいずれかを用いて形成される。Si半導体部202は、前記絶縁膜下に配置され、硫黄(S)とセレン(Se)とテルル(Te)とのうち少なくとも1種の元素が前記絶縁膜との界面に存在する、シリコン(Si)を用いて形成される。

(もっと読む)

61 - 80 / 1,150

[ Back to top ]