Fターム[5F140AC36]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 動作、用途、素子構造 (4,642) | 薄膜トランジスタ、TFT、SOI、SOS (1,150)

Fターム[5F140AC36]に分類される特許

101 - 120 / 1,150

半導体装置

【課題】トンネルトランジスタにおいて、その寄生容量を低減したゲート電極を提供する。

【解決手段】ゲート絶縁膜201を介して形成されたゲート電極202を挟むように形成された、第1導電型のソース領域121及び前記第1導電型とは逆導電型の第2導電型のドレイン領域122と、基板101内において前記ソース領域121と前記ドレイン領域122との間に形成された、第2導電型のチャネル領域123とを備える。そして、前記ゲート絶縁膜201は、前記ソース領域上に位置し、チャネル幅方向に平行な第1のエッジE1と、前記チャネル領域上又は前記ソース領域上に位置し、チャネル幅方向に平行な第2のエッジE2とを有し、第1の膜厚を有する第1の絶縁膜部分を有する。さらに、前記ゲート絶縁膜201は、前記第1の絶縁膜部分に対して前記ドレイン領域側に位置し、前記第1の膜厚よりも厚い第2の膜厚を有する第2の絶縁膜部分を有する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】工程増を最小限とした簡便な手法で、素子形成領域における化合物半導体と同時に、しかもその結晶性を損なうことなく確実な素子分離を実現し、信頼性の高い化合物半導体装置を実現する。

【解決手段】Si基板1上の素子分離領域に初期層3を選択的に形成し、初期層3上を含むSi基板1上の全面に化合物半導体の積層構造4を形成して、積層構造4は、素子分離領域では初期層3と共に素子分離構造4Bとなり、素子形成領域ではソース電極5、ドレイン電極6及びゲート電極7が形成される素子形成層4Aとなる。

(もっと読む)

半導体装置

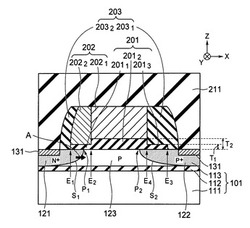

【課題】バンド間トンネリングが横方向に起こる構造を有し、バンド間トンネリングが起こる領域が大きいトンネルトランジスタを備える半導体装置を提供する。

【解決手段】第1上面S1と、第1上面S1よりも高さの低い第2上面S2と、第1上面と第2上面との間に存在する段差側面S3と、を有する段差が形成された基板。さらに、基板の段差側面S3と第2上面S2とに連続して形成されたゲート絶縁膜と、基板の段差側面S3に形成されたゲート絶縁膜に接するよう、第2上面S2上にゲート絶縁膜131を介して形成されたゲート電極132とを備える。さらに、基板内において、第1上面の下方に形成された第1導電型のソース領域121と、第2上面の下方に形成された第2導電型のドレイン領域122と、段差側面S3とソース領域122との間に形成された第2導電型の側方拡散領域123とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極とボディ領域とを接続したトランジスタを有する半導体装置に関し、動作速度を向上し消費電力を低減しうる半導体装置及びその製造方法を提供する。

【解決手段】第1の素子分離絶縁膜と、第1の素子分離絶縁膜により画定され、第1の素子分離絶縁膜よりも浅いウェルと、ウェル内に形成され、ウェルよりも浅く、ウェルの第1の部分とウェルの第2の部分とを画定する第2の素子分離絶縁膜と、第1の部分上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、第2の部分においてウェルに電気的に接続され、ゲート電極とウェルとを電気的に接続する配線層とを有し、第2の素子分離絶縁膜下の領域のウェルの電気抵抗が、ウェルの他の領域の同じ深さにおける電気抵抗よりも低くなっている。

(もっと読む)

フィンを含む半導体構造およびその形成方法

【課題】フィン高さの改良を図れるフィンの形成方法を提供すること。

【解決手段】実施形態のフィン形成の方法は、まず、半導体基板上に多層構造を形成する。前記半導体構造は、前記半導体基板上の第1の層、前記第1の層上の第2の層および前記第2の層上の第3の層を具備する。次に、前記半導体基板および前記半導体構造の複数の部分からなる複数のフィンを形成するために、前記半導体基板の複数の上部および前記半導体構造の複数の部分を除去する。次に、前記第2の層および前記第3の層の酸化速度を前記第1の層よりも酸化速度よりも小さくしながら、前記第1の層を選択的に酸化する。次に、前記選択的な酸化の後に前記複数のフィン間の空隙を絶縁材料で充填する。そして、フィンを露出させるために少なくとも前記絶縁材料の一部をリセスし、前記フィンの少なくとも一つの側面または前記フィンの上面をチャネル領域にする。

(もっと読む)

窒化ガリウム系半導体装置および半導体装置の製造方法

【課題】窒化ガリウム系半導体のドライエッチングに、塩素系ガスを用いたICP−RIEを用いると、誘電結合型プラズマは、温度が高いので、エッチングされた面に凹凸ができ、半導体にダメージを与え、塩素が残留する。

【解決手段】窒化ガリウム系半導体からなる第1の半導体層を形成する第1半導体層形成工程と、第1の半導体層の一部を、臭素系ガスを用いて、マイクロ波プラズマプロセスでドライエッチングして、リセス部を形成するリセス部形成工程と、を備え、窒化ガリウム系半導体装置を製造する半導体装置の製造方法を提供する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】窒化金属膜から放出される窒素がゲート絶縁膜に到達することを抑制する。

【解決手段】この半導体装置は、半導体基板100、第1ゲート絶縁膜110、シリコン含有第2ゲート絶縁膜122、及び第1ゲート電極を備えている。第1ゲート絶縁膜110は半導体基板100上に形成されており、酸化シリコン又は酸窒化シリコンよりも比誘電率が高い材料から構成されている。シリコン含有第2ゲート絶縁膜122は、第1ゲート絶縁膜110上に形成されている。第1ゲート電極はシリコン含有第2ゲート絶縁膜122上に形成されており、窒化金属層124を有している。第1ゲート絶縁膜110、シリコン含有第2ゲート絶縁膜122、及び窒化金属層124は、pMOSFETの一部を構成している。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル形成時のひずみ緩和の抑制を可能にすると共に、更にひずみを印加することを可能にする。

【解決手段】基板1と、基板上に形成されひずみを有する第1半導体層3と、第1半導体層3上に離間して設けられ、第1半導体層3と格子定数が異なる第2および第3半導体層8と、第2半導体層と第3半導体層8との間の第1半導体層3上に設けられたゲート絶縁膜4と、ゲート絶縁膜4上に設けられたゲート電極5と、を備え、第2半導体層および第3半導体層8直下の第1半導体層3の外表面領域をシリサイド3a、8aとする。

(もっと読む)

半導体装置

【課題】短チャネルでもオフ特性の優れたトランジスタ等の半導体装置を提供する。

【解決手段】ソース102aの周囲をエクステンション領域103aおよびハロー領域105a、ドレイン102bの周囲をエクステンション領域103bおよびハロー領域105bで取り囲むように配置し、また、不純物濃度の低い基板101がソース102a、ドレイン102bと接しない構造とする。さらに、ゲート絶縁物109を介して高仕事関数電極104を設け、基板101の表面近傍にエクステンション領域103aおよびエクステンション領域103bより侵入する電子を排除する。このような構造とすることにより、短チャネルでもチャネル領域の不純物濃度を低下させることができ、良好なトランジスタ特性を得ることができる。

(もっと読む)

電界効果型トランジスター

【課題】ダイヤモンドFETにおいて、ドレイン電流特性を改善すること。

【解決手段】ダイヤモンド結晶層1の上に、高濃度ホウ素ドープダイヤモンド薄膜層102を成長する(図1(a))。次に、ソース電極およびドレイン電極として、Ti層131A、131B、Au層132A、132Bを順に蒸着する(図1(b))。次に、400℃でアニールを行いTiをダイヤモンドと反応させて、TiC層133A、133Bを形成する(図1(c))。最後に、ゲート部にAl2O3膜141を形成し、その上にAlゲート電極42を蒸着する(図1(d))。作製したダイヤモンドFETのドレイン電流特性は、ゲート電圧−3Vにおける最大ドレイン電流密度が600mA/mmとなり、従来技術による場合の約6倍に増加した。温度依存性に関しては、従来技術では室温から150℃付近でドレイン電流密度は急激に減少したが、本発明では900℃まで安定して動作した。

(もっと読む)

マイクロローディング効果を軽減するためのSiGe埋め込みダミーパターンを備えたSiGe装置

【課題】SiGe装置を取り囲んで、SiGeのエピタキシャル成長時にマイクロローディング効果を軽減できるように特別に設計されたSiGe埋め込みダミーパターンを備えた改良されたSiGe装置を提供する。

【解決手段】マイクロローディング効果を軽減するためのダミーパターンを備えた半導体装置は、内部領域200と外部領域400の間に中間環状領域300が設けられた半導体基板1と、基板上、内部領域200に設けられたSiGe装置100と、基板上、中間環状領域300に設けられた複数のダミーパターン20とを含む。複数のダミーパターン20のうち少なくとも1つがSiGeを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート絶縁膜をHigh−k材料で構成し、ゲート電極をメタル材料で構成するHK/MGトランジスタと、抵抗素子とを同一基板に有する半導体装置において、安定したHK/MGトランジスタの動作特性を得ることのできる技術を提供する。

【解決手段】TiN膜と多結晶Si膜との積層膜からなるHK/MGトランジスタのゲート電極を形成し、同様に、TiN膜と多結晶Si膜との積層膜からなる抵抗素子を形成した後、抵抗素子の側壁に形成したオフセットサイドウォール9aおよびサイドウォール9の一部を除去し、そのオフセットサイドウォール9aおよびサイドウォール9が除去された箇所から薬液を浸入させることによりTiN膜を除去して空洞18を形成し、多結晶Si膜のみからなる抵抗部RESを形成する。

(もっと読む)

横型素子を有する半導体装置

【課題】高速スイッチング動作を行う場合でも、アバランシェブレークダウンを抑制でき、スイッチング損失低減や素子破壊を抑制することが可能な構成とする。

【解決手段】横型FWD7などの横型素子において、SRFP21の全抵抗Rの抵抗値を90kΩ〜90MΩ、好ましくは270kΩ〜27MΩ、より好ましくは900kΩ〜9MΩとすることにより、2ndピーク時のアノード電流IAなどの電流が大きくなることを抑制できる。これにより、高速スイッチング動作を行う場合でもアバランシェブレークダウンを抑制でき、横型FWD7のスイッチング損失低減や素子破壊を抑制することが可能となる。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化しても高い性能を実現可能な半導体装置を提供する。

【解決手段】実施の形態の半導体装置は、半導体基板と、半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、ゲート電極の両側に形成された第1のゲート側壁と、半導体基板上に形成され、ゲート電極との間に第1のゲート側壁を挟むソース・ドレイン半導体層と、を備える。さらに、ゲート電極の両側に、第1のゲート側壁上およびソース・ドレイン半導体層上に形成され、第1のゲート側壁との境界がゲート電極の側面で終端し、第1のゲート側壁よりもヤング率が小さく、かつ、低誘電率の第2のゲート側壁、を備える。

(もっと読む)

シリサイド化金属ゲートの形成のための方法

【課題】シリサイド化金属ゲートと、シリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物と、同ゲート構造物を製造する方法と、を提供する。

【解決手段】シリサイド化金属ゲートと、シリサイド化金属ゲートに接するシリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物を提供する。詳しくは、広義に、第一の厚さを有する第一のシリサイド金属のシリサイド化金属ゲートと、隣接する第二の厚さを有する第二の金属のシリサイド化ソース領域およびドレイン領域とを含み、第二の厚さは第一の厚さより薄く、シリサイド化ソース領域およびドレイン領域は少なくともシリサイド化金属ゲートを含むゲート領域の端に位置合わせした半導体構造物を提供する。さらに、シリサイド化金属ゲートと、シリサイド化金属ゲートに接するシリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物を製造する方法も提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性の劣化及び素子のばらつきを抑制しつつ、所望の閾値電圧を実現する。

【解決手段】実施形態による複数の閾値電圧を有する半導体装置500は、基板502と、第1の閾値電圧を有する基板上の第1のトランジスタ510と、第2の閾値電圧を有する基板上の第2のトランジスタ530とを具備する。第1のトランジスタは、基板の第1のチャネル領域上に形成された第1の界面層516と、第1の界面層上に形成された第1のゲート誘電体層518と、第1のゲート誘電体層上に形成された第1のゲート電極520,522とを具備する。第2のトランジスタは、基板の第2のチャネル領域上に形成された第2の界面層536と、第2の界面層上に形成された第2のゲート誘電体層538と、第2のゲート誘電体層上に形成された第2のゲート電極540,542とを具備する。第2の界面層は第1の界面層内になくかつSi、O及びNと異なる添加元素を有する。第1及び第2の閾値電圧は異なる。第1及び第2のトランジスタは同一の導電型である。

(もっと読む)

半導体装置の製造方法

【課題】MOSトランジスタの形成工程を利用して、トレンチアイソレーションを形成できるようにした半導体装置の製造方法を提供する。

【解決手段】シリコン基板1にDTI層20とMOSトランジスタとを有する半導体装置の製造方法であって、シリコン基板1に深いトレンチを形成し、トレンチが形成されたシリコン基板1に熱酸化を施して、PMOSトランジスタ50のゲート酸化膜13を形成すると同時に、トレンチの内側面にSiO2膜14を形成する。次に、トレンチを埋め込むようにシリコン基板1上にポリシリコン膜15を堆積し、このポリシリコン膜15をパターニングする。これにより、PMOSトランジスタ50のゲート電極17を形成すると同時に、トレンチ内にSiO2膜14とポリシリコン膜18とを含むDTI層20を形成する。

(もっと読む)

半導体装置の製造方法

【課題】n型FET及びp型FET(電界効果トランジスター)のうち、一方のFETの電流駆動能力の低下を抑制し、他方のFETの電流駆動能力の向上を図る。

【解決手段】n型FET及びp型FETを覆うように、第1の膜を形成する工程と、その後、p型(n型)FET上の前記第1の膜に対して、イオン注入法によって選択的に不純物を打ち込む工程とを有し、n型(p型)FETのチャネル形成領域には、n型(p型)FET上の前記第1の膜によって、主として、n型(p型)FETのゲート電極のゲート長方向に引張(圧縮)応力が発生しており、不純物を打ち込む工程によって、前記p型(n型)FETのチャネル形成領域に発生する引張(圧縮)応力は、n型(p型)FETのチャネル形成領域に発生する引張(圧縮)応力よりも小さくなっている。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート絶縁膜をHigh−k材料で構成し、ゲート電極をメタル材料で構成するHK/MGトランジスタを有する半導体装置において、安定した動作特性を得ることのできる技術を提供する。

【解決手段】素子分離部2で囲まれた活性領域14に位置し、後の工程でコア用nMISのゲートGが形成される領域Ga1のみに、Nch用ゲートスタック構造NGを構成する積層膜を形成し、上記領域Ga1以外の領域NGa1には、Pch用ゲートスタック構造PGを構成する積層膜を形成する。これにより、コア用nMISのゲートGが形成される領域Ga1へ素子分離部2から引き寄せられる酸素原子の供給量を減少させる。

(もっと読む)

半導体装置及びその製造方法、電源装置

【課題】半導体装置において、セルフターンオンが発生しないようにし、安定した動作を実現する。

【解決手段】半導体装置を、基板1と、基板の上方に設けられ、電子走行層6及び電子供給層7を含む半導体積層構造2と、半導体積層構造の上方に設けられたゲート電極3、ソース電極4及びドレイン電極5と、ゲート電極、ソース電極及びドレイン電極の上方に設けられ、ゲート電極、ソース電極及びドレイン電極のそれぞれに接続されたゲートパッド10、ソースパッド11及びドレインパッド12と、ゲートパッド、ソースパッド及びドレインパッドの下方に設けられた導電層1とを備えるものとし、ゲートパッドとソースパッドとの間の距離を、ゲートパッドとドレインパッドとの間の距離よりも小さくする。

(もっと読む)

101 - 120 / 1,150

[ Back to top ]