Fターム[5F140BA01]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 基板材料 (9,253) | 4族 (5,747)

Fターム[5F140BA01]の下位に属するFターム

Fターム[5F140BA01]に分類される特許

161 - 180 / 4,025

撮像装置の製造方法

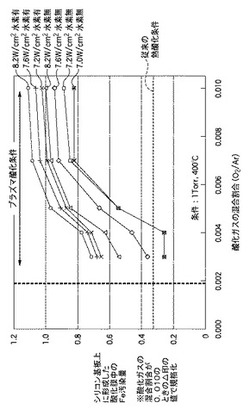

【課題】プラズマ酸化によりシリコン基板上に形成される酸化膜の金属汚染量を低減すること。

【解決手段】酸化膜の形成方法は、不活性ガスと、前記不活性ガスに対する混合割合が0よりも大きく且つ0.007以下である酸化ガスと、を含む混合ガスからプラズマを生成する工程と、前記プラズマを用いてシリコン基板の表面に酸化膜を形成する工程と、を含む。

(もっと読む)

化合物半導体装置の製造方法

【課題】 短チャンネル効果が抑制され、メタルS/Dを有するInGaAs−MOSFETの低消費電力化をはかり得る化合物半導体装置を製造する。

【解決手段】 InGaAsをチャネルに用いた化合物半導体装置の製造方法であって、基板上のInGaAs層10上に、ゲート絶縁膜11を介してゲート電極12を形成した後、ゲート電極12の両側に露出するInGaAs層10上に、厚さ5.5nm以下のNi膜14を形成する。次いで、250℃以下の温度で熱処理を施すことにより、Ni膜14とInGaAs層10とを反応させて、ショットキー・ソース/ドレインとなるNi−InGaAs合金層15を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】nチャネル型MISFETのしきい値を調整する目的でLaなどが導入された高誘電率膜を含むゲート絶縁膜と、その上部のメタルゲート電極との積層構造を有する半導体装置において、ゲート電極のゲート幅を縮小した際、基板側からメタルゲート電極の底面に酸化種が拡散してnチャネル型MISFETの仕事関数が上昇することを防ぐ。

【解決手段】HfおよびLn含有絶縁膜5bとその上部のメタルゲート電極である金属膜9との間に、酸化種の拡散を防ぐためにAl含有膜8cを形成する。

(もっと読む)

半導体装置

【課題】チャネル形成領域に対しトランジスタの電流駆動能力を向上させる方向に応力をかけ、さらに電流駆動能力が向上し、性能が向上された半導体装置を提供する。

【解決手段】半導体基板(1a,1b)の活性領域(1c,1d)が素子分離絶縁膜(2,6a)で区画され、チャネル形成領域、ゲート絶縁膜、ゲート電極(8a,8b)、ソース・ドレイン領域及び被覆応力膜を有するNTrとPTrを有し、活性領域におけるゲート長方向が<100>方向であり、素子分離絶縁膜としてNTrにおけるソース・ドレイン領域の両端部に第1の引張応力膜6aが形成され、ソース・ドレイン領域の両端部以外に第1の圧縮応力膜2が形成され、PTrの素子分離絶縁膜は第1の圧縮応力膜2が形成され、被覆応力膜としてNTrに第2の引張応力膜が形成され、PTrに第2の圧縮応力膜が形成されている構成とする。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】携帯電話などに使用されるハイパワーアンプの出力段は、多数のLDMOSFETセルを集積し、通常、複数のLDMOSFETを構成するLDMOSFET部を有する。このLDMOSFETセルにおいては、裏面のソース電極と表面のソース領域との間の抵抗を低減するために、半導体基板に高濃度にボロンドープされたポリシリコンプラグが埋め込まれている。本願発明者らが、このポリシリコンプラグについて、検討したところによって、熱処理に起因してポリシリコンプラグの固相エピタキシャル成長により、ポリシリコンプラグが収縮し、それによってシリコン基板に歪が発生し、リーク不良等の原因となることが明らかとなった。

【解決手段】本願発明は、LDMOSFETを有する半導体集積回路装置において、半導体基板に埋め込まれたシリコン系導電プラグのボロン濃度が、固溶限界内に於いて、8.1x1020atom/cm3以上である。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】窒化物半導体装置の、ソース・ドレイン間のオン抵抗を低減する。

【解決手段】ソース・ドレイン間を走行する窒化物半導体層と下地となる窒化物半導体層の間に、両窒化物半導体層より電子親和力が大きく、下地となる窒化物半導体よりも格子定数の大きい材料を形成する。その結果、ゲート電圧の印加によりゲート絶縁膜の下方に形成されるチャネルと、ゲート部以外で形成される二次元電子ガスを、深さ方向において近づけることができ、オン抵抗の低減が可能となる。

(もっと読む)

半導体基板の製造方法および半導体基板

【課題】高性能なIII−V族MISFETの実現を可能にする、より効果的なIII−V族化合物半導体表面のパッシベーション技術を提供する。

【解決手段】エピタキシャル成長により化合物半導体層をベース基板上に形成するステップと、前記化合物半導体層の表面をセレン化合物を含む洗浄液で洗浄するステップと、前記化合物半導体層の上に絶縁層を形成するステップと、を有する半導体基板の製造方法を提供する。前記セレン化合物として、セレン酸化物が挙げられる。前記セレン酸化物として、H2SeO3が挙げられる。前記洗浄液が、水、アンモニアおよびエタノールからなる群から選択された1以上の物質をさらに含んでもよい。前記化合物半導体層の表面がInxGa1−xAs(0≦x≦1)からなる場合、前記絶縁層がAl2O3からなるものであることが好ましく、Al2O3は、ALD法により形成されることが好ましい。

(もっと読む)

半導体装置とその製造方法

【課題】 単純で容易な実装手段によりMOSFETの閾値電圧を制御することが可能な半導体装置とその製造方法を提供する。

【解決手段】 一実施形態によれば、電界効果トランジスタは、STI(浅いトレンチ分離)を含んでいる半導体基板402と、p−FET401及びn−FET403と、p−FET401が形成される基板の窪み内のシリコン・ゲルマニウム層800と、n−FET部上とシリコン・ゲルマニウム層上に設けられた、ハフニウム化合物とレアアース化合物を含むゲート誘電体414, 432と、ゲート誘電体414, 432上にそれぞれ配置された互いに同じ材料を含むゲート電極416, 434とを具備している。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】絶縁破壊耐性に優れた化合物半導体積層構造を備えて基板の絶縁破壊の十分な抑止を実現し、ピンチオフ状態とする際にもリーク電流が極めて少ない信頼性の高い化合物半導体装置を実現する。

【解決手段】Si基板1上に形成された化合物半導体積層構造2は、その厚みが10μm以下であって、AlNからなる厚い第1のバッファ層を有しており、III族元素(Ga,Al)の総原子数のうち、Al原子の比率が50%以上とされ、換言すれば、V族元素のNとの化学結合(Ga−N,Al−N)の総数のうち、Al−Nが50%以上とされる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】高耐圧トランジスタ形成に適した半導体装置の新規な製造方法を提供する。

【解決手段】

半導体装置の製造方法は、シリコン基板に第1導電型第1領域と、第1領域に接する第2導電型第2領域を形成し、ゲート絶縁膜を形成し、第1領域と第2領域とに跨がるゲート電極を形成し、ゲート電極上から第2領域上に延在する絶縁膜を形成し、ゲート電極をマスクとし第2導電型不純物を注入してソース領域およびドレイン領域を形成し、ゲート電極および絶縁膜を覆って金属層を形成し熱処理を行って、ソース領域、ドレイン領域及びゲート電極にシリサイドを形成し、層間絶縁膜にソース領域、ドレイン領域、ゲート電極に達する第1、第2、第3コンタクトホール、及び絶縁膜に達する孔を形成し、第1〜第3コンタクトホール及び孔に導電材料を埋め込み、第1〜第3導電ビアと、孔の内部に配置された導電部材とを形成する。

(もっと読む)

半導体装置、金属膜の製造方法及び半導体装置の製造方法

【課題】高集積化することができる半導体装置、金属膜の製造方法及び半導体装置の製造方法を提供することである。

【解決手段】実施形態に係る半導体装置は、半導体基板と、前記半導体基板に形成され、ヒ素を含むヒ素拡散層と、前記ヒ素拡散層上に形成された金属膜と、を備える。前記金属膜は、タングステン、チタン、ルテニウム、ハフニウム及びタンタルからなる群より選択された少なくとも1種の金属、並びにヒ素を含む。

(もっと読む)

エンハンスメント型III−V族高電子移動度トランジスタ(HEMT)および製造方法

【課題】ノーマリオフ型、すなわちエンハンスメント型トランジスタであるIII族窒化物HEMTを提供する。

【解決手段】エンハンスメント型高電子移動度トランジスタ(HEMT)400はIII−V族半導体412上に位置するIII−V族バリア層414を含むヘテロ接合416、およびIII−V族バリア層414上に形成され、P型III−V族ゲート層452を含むゲート構造462を具える。P型III−V族ゲート層452によりゲート構造462下での2次元電子ガス(2DEG)の発生を防ぐ。エンハンスメント型HEMT400を製造する方法は、基板402を設け、基板402にIII−V族半導体412を形成し、III−V族半導体412上にIII−V族バリア層414を形成し、III−V族バリア層414上にP型III−V族ゲート層452を含むゲート構造462を形成する。

(もっと読む)

横型半導体装置

【課題】抵抗性フィールドプレート部のレイアウトの自由度を高める技術を提供すること。

【解決手段】コーナー範囲に設けられている中間抵抗性フィールドプレート部34は、カソード領域28とアノード領域23の間で往復を繰返して形成されている。直線範囲に設けられている中間抵抗性フィールドプレート部34も、カソード領域28とアノード領域23の間で往復を繰返して形成されている。コーナ範囲に設けられている中間抵抗性フィールドプレート部34と直線範囲に設けられている中間抵抗性フィールドプレート部34は接していない。

(もっと読む)

シリコンに対する誘電材料の選択エッチング方法及びシステム

【課題】 本発明はドライプラズマエッチングを用いた基板のエッチング方法に関する。

【解決手段】 ドライプラズマエッチングシステム内で誘電体層をシリコン及びポリシリコンに対して選択的な均一エッチングを行う方法及びシステムが記載されている。エッチング用化学は、たとえばCH2F2やCHF3のようなフルオロハイドロカーボンを有する。高いエッチング選択性及び受容可能な均一性は、CH2F2の流速やドライプラズマエッチングシステムと結合する出力を含むプロセス条件を選択することによって実現されて良い。それにより、エッチングプラズマ中での活性エッチングラジカルとポリマー生成ラジカルとの適切なバランスがとられる。

(もっと読む)

ノーマリーオフ型高電子移動度トランジスタ

【課題】 ノーマリーオフ型高電子移動度トランジスタを提供する。

【解決手段】 ノーマリーオフ型トランジスタは、III−V半導体材料の第1の領域、第1の領域上のIII−V半導体材料の第2の領域、第2の領域上のIII−V半導体材料の第3の領域、および第3の領域の少なくとも1つの側壁に隣接するゲート電極を含む。第1の領域はトランジスタのチャネルを提供する。第2の領域は第1の領域のバンドギャップより大きなバンドギャップを有し、チャネル内に2D電子ガス(2DEG)を引き起こす。第2の領域は第1の領域と第3の領域との間に挿入される。第3の領域は、トランジスタのゲートを提供し、トランジスタが正の閾値電圧を有するようにチャネル内の2DEGを空乏化するのに十分な厚さを有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】ゲート電極とコンタクトとの間の短絡の発生を抑制する。

【解決手段】基板(2)に設けられた第1拡散領域(3)と、基板(2)に設けられた第2拡散領域(3)と、第1拡散領域(3)に接続された第1コンタクト(11)と、第2拡散領域(3)に接続された第2コンタクト(11)と、第1拡散領域(3)と第2拡散領域(3)の間に設けられたチャネル領域と、ゲート絶縁膜(6)を介してチャネル領域の上に設けられたゲート電極(5)とを具備する半導体装置を構成する。ゲート電極(5)は、第1コンタクト(11)と第2コンタクト(11)とに挟まれた第1領域(A−A’)と、第1領域と異なる第2領域(B−B’)とを備える。第1領域(A−A’)は、第1コンタクト側の第1側面と、第2コンタクト側の第2側面とを含む。第1側面は、第1コンタクトから離れる方向に傾斜する。第2側面は、第2コンタクトから離れる方向に傾斜する。

(もっと読む)

仮想ボディ・コンタクト型トライゲート

【課題】FETデバイスにおける閾値電圧をより良く制御できるデバイスの提供。

【解決手段】基板101と、基板101の上のSiGe層103と、SiGe層上の半導体層105と、基板、SiGe層及び半導体層に隣接した絶縁層109aと、絶縁層に隣接した一対の第1のゲート構造体111と、絶縁層上の第2のゲート構造体113とを含む電界効果トランジスタ(FET)と、FETを形成する方法である。絶縁層は、SiGe層の側面、並びに半導体層の上面、半導体層の下面及び導体層の側面に隣接していることが好ましい。SiGe層は、炭素を含むことが好ましい。一対の第1のゲート構造体が、第2のゲート構造体に対して実質的に横断方向にあることが好ましい。さらに、第1のゲート構造体の対は、絶縁層によりカプセル封入されることが好ましい。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、チャネル抵抗を減少させてオン電流を増加させることが可能で、かつ各トランジスタを独立して、安定して動作させることの可能な半導体装置及びその製造方法を提供する。

【解決手段】ゲート電極用溝18の底部18cから活性領域の一部が突き出すように形成されたフィン部15と、ゲート電極用溝18及びフィン部15の表面を覆うゲート絶縁膜21と、ゲート電極用溝18の下部に埋め込まれ、ゲート絶縁膜21を介してフィン部15を跨ぐように形成されたゲート電極22と、第1の不純物拡散領域28と、第2の不純物拡散領域29と、フィン部15の表面に設けられた準位形成領域30と、を備える半導体装置10を選択する。

(もっと読む)

半導体装置

【課題】従来の半導体装置においては、シリコンエピタキシャル層に結晶欠陥が生じ易いという問題がある。

【解決手段】半導体装置1は、シリコン基板10、歪み付与層20、シリコン層30、FET40、および素子分離領域50を備えている。シリコン基板10上には、歪み付与層20が設けられている。歪み付与層20上には、シリコン層30が設けられている。歪み付与層20は、シリコン層30中のFET40のチャネル部に格子歪みを生じさせる。シリコン層30中には、FET40が設けられている。FET40は、ソース・ドレイン領域42、SD extension領域43、ゲート電極44およびサイドウォール46を含んでいる。ソース・ドレイン領域42と上述の歪み付与層20とは、互いに離間している。FET40の周囲には、素子分離領域50が設けられている。素子分離領域50は、シリコン層30を貫通して歪み付与層20まで達している。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】安定に動作する半導体装置を提供する。

【解決手段】本明細書に開示する半導体装置は、基板11内に形成された第1導電型のウェル13と、ウェル13上にゲート絶縁膜17を介して配置されるゲート電極18と、ゲート電極18を挟んで基板11内に対向して配置される第2導電型のソース領域15及びドレイン領域16と、基板11内にソース領域15と隣接して配置され、ウェル1に電気的に接続される第1導電型のウェルタップ19と、ウェル13とウェルタップ19とに接し、ウェル13よりも不純物濃度が高く、第1導電型を有するポケット領域20と、を備える。

(もっと読む)

161 - 180 / 4,025

[ Back to top ]