Fターム[5F140BA05]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 基板材料 (9,253) | 4族 (5,747) | SiGe (619)

Fターム[5F140BA05]に分類される特許

601 - 619 / 619

半導体装置及び半導体装置の製造方法

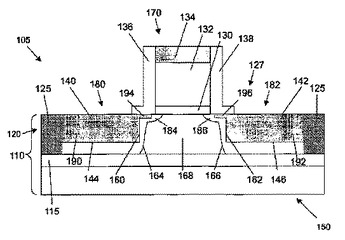

本発明は、半導体装置(105)及びこの装置の製造方法に関する。本発明の好ましい実施例は、シリコン半導体基板(110)、酸化膜層(115)及び活性層(120)を含む半導体装置(105)である。活性層では、絶縁領域(125)及び活性領域(127)が形成された。活性領域(127)は、ソース(180)、ドレイン(182)及び基体(168)を含む。ソース(180)及びドレイン(182)は、ソースエクステンション(184)及びドレインエクステンション(186)も含む。活性層(120)はゲート(170)を有する。ゲート(170)の両側にL字型側壁スペーサが位置する。ソース(180)及びドレイン(182)は、シリサイド領域(190、192)も含む。これらの領域の特徴は、側壁(136、138)の下に位置されたエクステンション(194、196)を有することである。これらのエクステンション(194、196)は、半導体装置(105)の性能を著しく改善するように、ソース(194)及びドレイン(196)の直列抵抗を大きく低減する。  (もっと読む)

(もっと読む)

CMOS用歪トランジスタの集積化

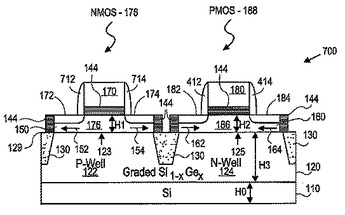

【解決手段】CMOSデバイスに関連する本発明の様々な実施形態は、(1)選択的に蒸着されたシリコン材料が、第1の領域における傾斜シリコンゲルマニウム基板材料の格子面間隔より小さい、シリコン材料の格子面間隔によって引き起こされる引っ張り歪を経験するべく、傾斜シリコンゲルマニウム基板の第1の領域上に選択的に蒸着されたシリコン材料のNMOSチャンネル、および(2)選択的に蒸着されたシリコンゲルマニウム材料が、第2の領域における傾斜シリコンゲルマニウム基板の格子面間隔よりも大きい、選択的に蒸着されたシリコンゲルマニウム材料の格子面間隔によって引き起こされる圧縮歪を経験すべく、基板の第2の領域上に選択的に蒸着されたシリコンゲルマニウム材料のPMOSチャンネルを有する。

(もっと読む)

(もっと読む)

MIS型電界効果トランジスタ

下地SiGe層1上に歪みSi層2をエピタキシャル成長させ、ゲート絶縁膜3aとゲート電極4aを形成した後、ゲート電極4aをマスクにして、下地SiGe層1及び歪みSi層2に不純物をイオン注入し(図2(a))、活性化のための熱処理を行ってソース・ドレイン領域6を形成する(図2(b)、(c))。このとき、歪みSi層2の膜厚は、最終的なMISFETのソース・ドレイン領域6の不純物濃度が最大となる深さをTp(=Rp)としたとき、2Tp以下にする。 (もっと読む)

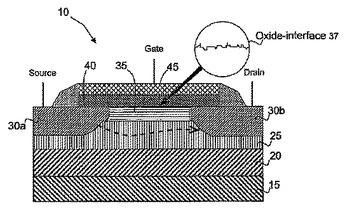

ヘテロ構造を有した電界効果トランジスタ、およびその製造方法

本発明は、ヘテロ構造を有した電界効果トランジスタに関する。当該ヘテロ構造では、キャリア材料上に歪み単結晶半導体層(4)が形成されている。当該キャリア材料は、最上層として、第1の半導体材料(Si)からなる緩和単結晶半導体層(3)を備えている。上記緩和単結晶半導体層は半導体合金(GexSi1−x)を含んでいて、第2の半導体材料の比率xは自由に設定できる。さらに、上記歪み半導体層(4)上に、ゲート絶縁層(5)およびゲート層(6)が形成される。この場合、非ドープチャネル領域(K)を構成するために、少なくとも歪み半導体層(4)において、ドレイン/ソース領域(D、S)が上記ゲート層に対して横向きに形成される。Ge比率xを自由に設定できる可能性によって、閾値電圧を任意に設定でき、これによって最新の論理半導体部品を実現することができる。  (もっと読む)

(もっと読む)

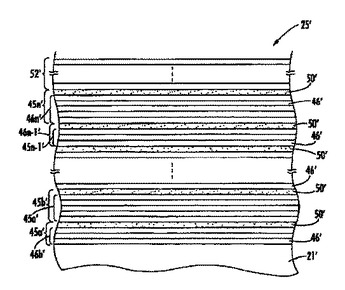

完全に量子井戸が空乏化した低出力のマルチチャネルCMOSFET

マルチチャネル半導体デバイスは、完全に、または部分的に量子井戸が空乏化(排除)(depleted)されており、CMOSFETのようなULSIデバイスにおいて特に役立つ。マルチチャネル領域(15)は、最上部のチャネル領域上に、例えばゲート絶縁膜(14c)により分離されるゲート電極が形成された状態で、基板(12)上に形成される。マルチチャネル領域(15)およびゲート電極(16)の垂直方向の積み重なりが、デバイスによって占有されるシリコン領域を増加させることなく、半導体デバイス中の駆動電流を増加させることができる。  (もっと読む)

(もっと読む)

FETゲート電極用のCVDタンタル化合物(TaおよびNを含む化合物の化学的気相堆積方法および半導体電界効果デバイス)

【課題】電界効果デバイスのゲート材料を提供すること。

【解決手段】電界効果デバイスのゲート材料として用いられるTaおよびNの化合物であって、さらに別の元素を含む可能性があり、約20mΩcmより小さな比抵抗を有し、約0.9より大きなN対Taの元素比を有する化合物が開示される。そのような化合物の代表的な実施態様であるTaSiNは、誘電体層および高k誘電体層を含むSiO2上の一般的なCMOSプロセス温度で安定であり、n型Siの仕事関数に近い仕事関数を有する。第3アミルイミドトリス(ジメチルアミド)Ta(TAIMATA)などのアルキルイミドトリス(ジアルキルアミド)Ta化学種をTa前駆体として用いる化学的気相堆積方法によって、金属性Ta−N化合物を堆積する。この堆積は共形であり、これらのTa−N金属化合物のCMOSプロセスフローへの融通の利く導入を可能にする。TaNまたはTaSiNを用いて加工されたデバイスは、ほぼ理想的な特性を示す。

(もっと読む)

CMOSデバイスのための歪みSiを形成する方法及び構造体

【課題】 チャネルのNFET及びPFETにおいて、それぞれ大きい引張応力及び圧縮応力を生成するように、費用対効果が大きく、簡単化された方法を提供すること。

【解決手段】 n型デバイス及びp型デバイスを含むデバイスの製造方法である。本発明の一態様において、方法は、半導体基板の部分をドープするステップと、半導体基板のドープされた部分の少なくとも一部を除去することによって、該半導体基板内にギャップを形成するステップとを含む。この方法はさらに、半導体基板内のギャップの少なくとも一部に歪み層を成長させるステップをさらに含む。n型デバイスの場合には、歪み層は、少なくともn型デバイスのチャネルのほぼ真下にある部分の上に成長される。p型デバイスの場合には、歪み層は、少なくともp型デバイスのソース領域又はドレイン領域のほぼ真下にあり、p型デバイスのチャネルのほぼ下にはない部分の上に成長される。

(もっと読む)

半導体装置の製造方法

シリコン基板(101)上に、RTO法によりシリコン酸化物からなる下地層(103)を形成する。このとき、下地層(103)の膜厚を1.5nm以上とする。次に、下地層(103)上に、CVD法によりハフニウム窒化物を0.5乃至1.0nmの厚さに堆積させ、金属化合物層(104)とする。次に、水素雰囲気中において熱処理を施し、金属化合物層(104)から下地層(103)中にハフニウム元素を拡散させてシリケート化させ、ゲート絶縁膜(106)を形成する。その後、酸化雰囲気中において熱処理を行う。このとき、シリコン基板(101)とゲート絶縁膜(106)との界面には、ハフニウム元素が到達しないようにする。  (もっと読む)

(もっと読む)

等方性エッチングプロセスを使ったショットキーバリアMOSFET製造方法

【課題】電流の流れを調整するトランジスタデバイスの組立て方法において、更なる駆動電流を可能にし、デバイスの動作を最適化するプロセスを提供すること。

【解決手段】本発明の一実施形態における方法は、チャンネル領域に対するショットキーバリア接合位置のより良い制御を与えるために、メタルソースドレイン接触の形成に先行して等方性エッチングプロセスを利用する。このショットキーバリア10接合の配置の制御性からの改善により、更なる駆動電流を可能にし、デバイスの動作を最適化する。

(もっと読む)

ストレインド・シリコン電圧制御発振器(VCO)

ストレインド・シリコン電圧制御発振器(VCO)は、ストレインド・シリコン層を有する第1Pチャネル金属酸化膜半導体(PMOS)装置を含み、ストレインド・シリコン層を有する第2PMOS装置に結合される。  (もっと読む)

(もっと読む)

格子定数の異なる材料を用いる半導体構造及び同構造の形成方法

半導体構造体(10)は、第1格子定数を有する第1緩和半導体材料から構成された基板を含む。半導体デバイス層(34)は基板を覆い、該半導体デバイス層は第1格子定数とは異なる第2格子定数を有する第2緩和半導体材料(22)を含む。加えて、誘電体層が基板と半導体デバイス層との間に介在され、該誘電体層は第1格子定数と第2格子定数間の遷移のため、誘電体層内に配置されたプログラムされた遷移帯を含む。該プログラムされた遷移帯は複数層を含み、該複数層の隣接する層は異なる格子定数を有し、隣接する層の1つが欠陥を形成するのに必要な第1限界厚さを超える第1厚さを有し、隣接する層の別の層が第2限界厚さを超えない第2厚さを有する。複数層の各隣接する層は、遷移帯内の欠陥を促進してプログラムされた遷移帯の縁部に移行させて終端させる境界面を形成する。また、該半導体構造を製造する方法も開示される。

(もっと読む)

(もっと読む)

Geベース材料上のゲルマニウム酸窒化物層の生成

【課題】 Geベース材料上にゲルマニウム酸窒化物層を生成すること。

【解決手段】 ゲート誘電体として用いるために、6nmより薄い等価酸化物厚をもつ薄いゲルマニウム酸窒化物層をGeベース材料上に生成する方法が開示される。この方法は二ステップのプロセスを含む。第一に、窒素がGeベース材料の表面層に組込まれる。第二に、窒素組込みステップ後に酸化ステップが続く。本方法は、MOSトランジスタなどのGeベース電界効果デバイスのための高品質ゲート誘電体の厚さに対する優れた制御をもたらす。薄いゲルマニウム酸窒化物ゲート誘電体を有するデバイスの構造及びこのようなデバイスから作られるプロセッサも同様に開示される。

(もっと読む)

酸化物−窒化物スタックゲート誘電体

半導体構造体を作製する方法は、基板上に酸化物層を形成する段階と、酸化物層上に窒化ケイ素層を形成する段階と、各層をNO中でアニールする段階と、各層をアンモニア中でアニールする段階とを含む。酸化物層と窒化ケイ素層とを併せた等価酸化膜厚は、最大25オングストロームである。 (もっと読む)

LDMOSトランジスタを有する電子装置

本発明のLDMOSトランジスタは、段付きシールド構造及び/又は第1及び第2ドレイン延長領域を具備し、前記第1ドレイン延長領域は、前記第2ドレイン延長領域よりも高いドーパント濃度を有し、前記シールドによって被われている。

(もっと読む)

(もっと読む)

空洞を有するシリコン基板上の高移動度MISFET半導体装置及びその製造方法

MISFETの高性能化を実現する高移動度歪みシリコン構造に、低欠陥かつ低コストで移動度を向上した半導体装置を提供する。MISFETの高性能化を実現する高移動度歪みシリコン構造として、空洞を有するシリコン基板上に、格子緩和シリコン・ゲルマニウム膜/濃度傾斜シリコン・ゲルマニウム膜を形成し、さらにその上に歪みシリコン膜を形成する。これにより、空洞近傍の格子の束縛が緩み、自由度が増すことにより、シリコン・ゲルマニウム膜の薄膜化が実現できるため、低欠陥かつ低コストで移動度を向上した半導体装置を提供できる。 (もっと読む)

集積化金属珪化物ゲート電極を有するトランジスタの形成方法

集積化した金属珪化物トランジスタゲート電極を有するトランジスタを半導体アセンブリ内に形成する方法を提供する。トランジスタゲートは部分的に、金属を溝内に存在させた状態でエピタキシャルシリコンと反応させることにより製造する。前記溝内で前記金属珪化物上にトランジスタゲート分離キャップ層を形成する。任意ではあるが溝スペーサを設けて所定の製造処理の臨界的な寸法上の制約を低減させ、従って、形状寸法が臨界的な寸法よりも小さいトランジスタを形成しうるようにすることができる。  (もっと読む)

(もっと読む)

半導体基板におけるドーパントの拡散を低速化する方法およびこれにより製造されたデバイス

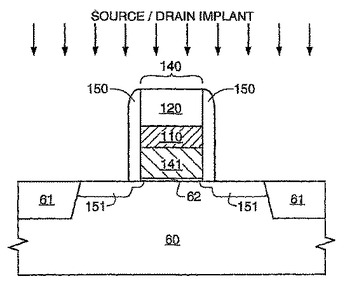

【課題】 ひずみSi/Si1-XGeXデバイス基板において、極めて浅い接合を形成する方法およびそれによって得られる半導体構造を提供する。

【解決手段】 半導体デバイスを形成する方法(およびその結果として得られる構造)は、基板上に、ドーパントおよび少なくとも1つの種を注入するステップと、基板をアニールするステップであって、少なくとも1つの種が、基板のアニールの間のトーパントの拡散を遅らせるステップと、を含む。

(もっと読む)

バンド設計超格子を有する半導体装置

半導体装置は、複数の積層された層群を有する超格子を有する。超格子の各層群は、基本半導体部分を定形する複数の積層された基本半導体分子層と、該基本半導体部分上のエネルギーバンド調整層と、を有する。さらにエネルギーバンド調整層は、少なくとも一つの非半導体分子層を有し、この層は、連接する基本半導体部分の結晶格子内に閉じ込められる。従って超格子は、平行な方向において、エネルギーバンド調整層がない場合に比べて大きな電荷キャリア移動度を有する。  (もっと読む)

(もっと読む)

絶縁ゲート型電界効果トランジスタを含む半導体装置及びその製造方法

【課題】シリコン基板上のSi1−xGex層を用いた素子構造において、電流駆動能力の高いMISFETを含む半導体装置及びその製造方法を提供することにある。

【解決手段】シリコン基板101上に、Si1−xGex層103を形成し、このSi1−xGex層103にMISFETを形成する。ソース層及びドレイン領域106,107の接合深さを、前記Si1−xGex層103とシリコン層とが接する面を越えないようにする。

(もっと読む)

601 - 619 / 619

[ Back to top ]