Fターム[5F140BA05]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 基板材料 (9,253) | 4族 (5,747) | SiGe (619)

Fターム[5F140BA05]に分類される特許

141 - 160 / 619

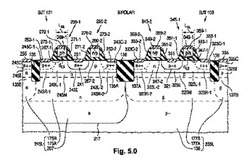

非単結晶半導体間隔部分がベース・リンク長を制御するバイポーラ接合トランジスタを有する半導体構成体の構成及び製造

【課題】 半導体構成体がバイポーラトランジスタ(101)及び間隔構成体(265−1又は265−2)を包含している。

【解決手段】 該トランジスタはエミッタ(241)、ベース(243)、コレクタ(245)を有している。該ベースはベースコンタクト部分(243−1)、該エミッタの下側で且つ該コレクタの物質上方に位置されているイントリンシックベース部分(243I−1)、該イントリンシックベース部分とベースコンタクト部分との間に延在しているベースリンク部分(243L−1)を包含している。該間隔構成体は、間隔コンポーネント及び上部半導体表面に沿って延在する分離用誘電体層(267−1又は267−2)を包含している。該間隔コンポーネントは、該ベースリンク部分の上方で該誘電体層上に位置されており、好適には多結晶半導体物質であるほぼ非単結晶の半導体物質の横方向間隔部分(269−1又は269−2)を包含している。該横方向間隔部分の両側の第1及び第2下部端部(305−1及び307−1)は該ベースリンク部分の両側の第1及び第2上部端部(297−1及び299−1)に対して横方向に適合し、その長さを決定し且つそれにより制御する。

(もっと読む)

量子井戸デバイスにおける平行伝導を改善する装置及び方法

平行伝導を改善する量子井戸デバイスを提供する方法及び装置の実施形態が主に記載される。その他の実施形態についても、記載及び特許請求される。 (もっと読む)

ゲート・ダイオード構造及びゲート・ダイオード構造の製造方法

【課題】改善された特性と強化された機能とを備えたダイオード構造とその製造方法が望まれている。

【解決手段】ゲート・ダイオード構造及びSOI基板(SOI)等の上にゲート・ダイオード構造を製造する方法であって、緩和下地層(34‘)を用いる。緩和下地層は歪下地層(34)から形成される。歪下地層(34)は典型的にはゲート・ダイオード構造と同時に形成される電界効果型トランジスタに用いられる。緩和下地層は歪下地層(34)のイオン注入処理のような処理により形成される。反応性イオンエッチング方法を用いてゲート・ダイオード構造から歪下地層を除去するときのゲート・ダイオードの損傷がないので、歪下地層に比較して、緩和下地層はゲート・ダイオード構造の理想値を改善する。

(もっと読む)

半導体素子及び半導体装置

【課題】高い電流駆動力を有するn型半導体素子を提供する。

【解決手段】第1の主面を有し、III族の不純物を含み、1.2<N<10を満たすNを用いて(11N)面と表される、ないしはそれと結晶学的に等価な第1の面方位のみを前記第1の主面に有する、シリコンとゲルマニウムとの混晶層と、前記第1の主面上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成されたゲート電極と、前記混晶層の[110]方向ないしそれと結晶学的に等価な方向に、前記ゲート電極を挟む様に形成され、V族の不純物を含む半導体よりなるソース・ドレイン領域と、を有し、前記混晶層は面内方向に圧縮歪みが印加されていることを特徴とする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】横方向の寸法の増大を抑制しつつ、横型二重拡散電界効果トランジスタのソースとドレインとの間の電界を緩和する。

【解決手段】N型ドリフト層17には、埋込絶縁層14下に配置されたP−ダンパ層19を形成するとともに、P−ダンパ層19を取り囲むように配置されたN−ダンパ層18を形成し、N−ダンパ層18およびP−ダンパ層19にて埋込絶縁層14下が空乏化されるように不純物濃度を設定する。

(もっと読む)

高誘電率ゲート絶縁膜を備えた電界効果トランジスタを有する半導体装置及びその製造方法

【課題】高誘電率ゲート絶縁膜を用いるFET及びその製造方法において、閾値電圧の制御性を向上する。

【解決手段】基板101上に高誘電率ゲート絶縁膜110、その上にゲート電極111aを形成する。少なくともゲート電極111aをマスクとして基板101にN型不純物を導入し、N型イクステンション領域113を形成する。少なくともゲート電極111aをマスクとして、基板101におけるN型イクステンション領域113の下にP型不純物を導入し、P型ポケット領域114を形成する。N型イクステンション領域113に対するN型不純物のうちのAsの導入量を、当該Asと高誘電率ゲート絶縁膜110中の元素との結合によって生じる異常な短チャネル効果が実質的に抑制される臨界点以下である範囲に設定する。臨界点は、高誘電率ゲート絶縁膜110の膜厚に基づいて算出される。

(もっと読む)

半導体装置

【課題】電気的性質が良好なhigh−k膜/Geゲートスタック構造を有する半導体装置を提供する。

【解決手段】Geを主成分とする半導体領域(10)と、前記半導体領域上に形成された絶縁膜(11)と、前記絶縁膜上に形成された金属膜(12)とを具備する半導体装置である。前記絶縁膜は、少なくとも1種の希土類元素(MR)と、TiおよびZrから選択される少なくとも1種のIV族元素(MIV)と、酸素とを含むことを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】偏析不純物による仕事関数の制御の可能な半導体装置または半導体装置の製造方法を提供する。

【解決手段】半導体装置は、半導体基板10と、半導体基板10上に設けられた絶縁膜(HfSiON膜30)と、絶縁膜30上にフルシリサイド電極(NiSi51)と、フルシリサイド電極51に接するように、絶縁膜30とフルシリサイド電極51の間に設けられたバリア膜(SiOC膜40)と、を備え、SiOC膜40と接するフルシリサイド電極51の部分に、N型またはP型いずれかの不純物60が偏析し、SiOC膜40は、シリコン酸窒化膜の誘電率以下の誘電率を有し、以下の(a)、(b)および(c)を主成分として含み、((a)シリコン(Si)、(b)炭素(C)、(c)酸素(O)または窒素(N))、HfSiON膜30またはNiSiフルシリサイド電極51を構成する金属元素を主成分としてバリア膜の少なくとも内部に含まないもの。

(もっと読む)

半導体デバイスの形成方法及びエッチング・マスク

【課題】 フィン型FETデバイス及びこれの製造方法を提供する。

【解決手段】 半導体デバイスは、基板を準備しそして基板上に半導体含有層を形成することにより形成される。次いで、複数個の開口を有するマスクが、半導体含有層上に形成され、ここでマスクの複数個の開口のうち互いに隣接する開口は、最小構造寸法だけ離されている。その後、半導体含有層の第1部分にドーパントを導入するために、角度付けしたイオン注入が行われ、ここでドーパントがほぼ存在しない残りの部分がマスクの下側に存在する。サブリソグラフィック寸法のパターンを形成するために、半導体含有層のうちドーパントを含む第1部分がこの半導体層のうちドーパントをほぼ含まない残りの部分に対して選択的に除去され、そしてサブリソグラフィック寸法のフィン構造を生じるために、パターンが基板に転写される。

(もっと読む)

キャパシタ構造及び半導体素子

【課題】キャパシタ構造において、電極間を流れる電流を抑制しつつ電極間の絶縁層を極限まで薄層化する。

【解決手段】ゲート電極Si層10と対向する電極としてのチャネルSi層30との間に所望の電圧を印加した際に、少なくともどちらか一方の電極物質でキャリアが存在しうるエネルギー範囲に存在する両電極物質の全エネルギーバンドについて、少なくとも片方の電極の該当エネルギーバンドの一部に関して、対向して配置した面の面方向の運動量の一致するエネルギーバンドがもう一方の電極の同一エネルギーのエネルギーバンドに存在しないように接合面及び接合面に垂直な軸に関する相対的回転角度を選択することで、電極間のキャリアの透過を抑制する。本発明のキャパシタ構造では、面方向の運動量が一致しないエネルギーバンドが存在するため、このエネルギーバンドが関与するキャリアの透過による電流を抑制することができる。

(もっと読む)

半導体装置の製造方法

【課題】所望のシリサイド膜を形成しつつ、半導体装置の生産性を向上することが可能な半導体装置の製造方法を提供する。

【解決手段】第1の圧力の不活性雰囲気中において、第1の加熱温度の第1の加熱処理により、ソース・ドレイン拡散層のシリコンとソース・ドレイン拡散層上の金属とを反応させて、ソース・ドレイン拡散層の上部をシリサイド化してシリサイド膜を形成し、第2の圧力の酸化性雰囲気において、第2の加熱温度の第2の加熱処理により、素子分離絶縁膜の上の金属膜の少なくとも表面を選択的に酸化して、金属酸化膜を形成し、第1の加熱温度および第2の加熱温度よりも高い第3の加熱温度の第3の加熱処理により、シリサイド膜のシリコンの濃度を増加し、素子分離絶縁膜上の金属酸化膜および金属膜の未反応部分を選択的に除去する。

(もっと読む)

減少させられたゲート電極ピッチを有する非対称トランジスタのための段階的なウエル注入

【解決手段】

洗練された半導体デバイスにおいて、非対称ウエル注入に基いて非対称トランジスタ構造が得られる一方で傾斜注入プロセスは回避し得る。この目的のために、段階的なレジストマスクのような段階的な注入マスクが形成されてよく、段階的な注入マスクは、非対称トランジスタのソース側と比較してドレイン側で高いイオン遮断能力を有していてよい。例えば、非対称構造は、高度な性能向上を伴う非傾斜注入プロセスに基いて得ことができ、また考慮されている技術標準にかかわりなく完成され得る。

(もっと読む)

電界効果トランジスタ

【課題】歪みチャネルを用いた場合のリーク電流を低減することができ、不良の発生を抑制して歩留まりの向上をはかる。

【解決手段】半導体基板10上に設けられた、基板10とは格子定数の異なる合金半導体からなる下地層20と、下地層20上に設けられた、下地層20とは格子定数が異なり、チャネル長方向及びチャネル幅方向の一方に引っ張り応力、他方に圧縮応力が付与されたチャネル半導体層30と、チャネル半導体層30を挟むように下地層20上に設けられたソース・ドレイン領域60,70と、チャネル半導体層30上にゲート絶縁膜40を介して設けられたゲート電極50とを備えた電界効果トランジスタであって、下地層20は、ソース・ドレイン領域60,70の下部に形成される空乏層61,71が下地層20内に収まる厚さよりも厚く形成され、且つ熱平衡臨界膜厚よりも薄く形成されている。

(もっと読む)

半導体装置

【課題】ソース・ドレイン領域のエクステンション領域の不純物濃度プロファイルが急峻なp型トランジスタを有する半導体装置を提供する。

【解決手段】本発明の一態様に係る半導体装置1aは、半導体基板2上に形成された結晶層13と、結晶層13上にゲート絶縁膜14を介して形成されたゲート電極15と、半導体基板2と結晶層13との間に形成された、ゲート電極15の下方の領域において第1の不純物を含むC含有Si系結晶からなる不純物拡散抑制層12と、半導体基板2、不純物拡散抑制層12、および結晶層13内のゲート電極15の両側に形成され、結晶層13内にエクステンション領域を有する、p導電型を有する第2の不純物を含むp型ソース・ドレイン領域17と、を有し、C含有Si系結晶は第2の不純物の拡散を抑制する機能を有し、第1の不純物は、C含有Si系結晶内の固定電荷の発生を抑制する機能を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】キャップ膜としてのランタン酸化膜の膜厚の増加を抑えつつ、閾値電圧の低減化を図れる、窒化チタン膜を含むメタルゲート電極/Hfを含有するゲート絶縁膜のゲートスタック構造を有するMOSFETを備えた半導体装置を適用すること。

【解決手段】P型半導体領域105を含む半導体基板101と、P型半導体領域101に形成されたNチャネルMOSFETとを具備してなり、前記NチャネルMOSトランジスタは、半導体基板101上に形成され、ハフニウムを含有するゲート絶縁膜108と、ゲート絶縁膜109上に形成され、膜厚が所定値以下のランタン酸化膜109と、ランタン酸化膜109上に形成され、N/Ti原子数比が1未満の窒化チタン膜110を含むゲート電極とを具備してなることを特徴とする。

(もっと読む)

集積回路構造及びその製造方法

【課題】得られるフィンFETのゲルマニウム百分率を高くしてゲルマニウム膜の欠陥を少なくすることにより、フィンFETの駆動電流を高め、ゲルマニウム含有膜の形成に用いるSTI領域を形成するピッチに余裕を持たせる集積回路構造及びその製造方法を提供する。

【解決手段】集積回路構造の製造方法は、半導体基板20を準備する工程と、半導体基板20の中に、第1の絶縁領域と第2の絶縁領域とを互いに対向するように形成する工程と、互いに隣接した第1の絶縁領域と第2の絶縁領域との間に設けられた底部と、半導体基板20に接触した底面と、を有する水平プレート42と、水平プレート42に隣接するように上方に設けられたフィン40とを有する逆T形のエピタキシャル半導体領域を形成する工程と、フィン40の頂面及び側壁の頂部にゲート誘電体46を形成する工程と、ゲート誘電体46の上にゲート電極48を形成する工程と、を含む。

(もっと読む)

半導体装置の製造方法

【課題】Siウェハ中にダメージを発生させないフラッシュランプアニール法を提供すること。

【解決手段】単結晶Si領域を含むSiウェハの上方に、複数のフラッシュランプを含むフラッシュランプ光源を配置する工程と、前記光源から放射された光により前記Siウェハを加熱する第1の加熱処理および第2の加熱処理を含む工程であって、前記第1の加熱処理および前記第2の加熱処理のそれぞれにおいて、前記光により前記Siウェハ上に形成される光強度分布が、前記単結晶Si領域の結晶方位とは異なる方向において強度が最大値となる分布が形成されるように、前記Siウェハを加熱し、かつ、前記第1の加熱処理時における前記複数のフラッシュランプの配列方向と前記第2の加熱処理時における前記複数のフラッシュランプの配列方向とが異なる前記工程とを有し、前記単結晶Si領域の前記結晶方位が、前記単結晶Si領域の劈開面の面方位であること。

(もっと読む)

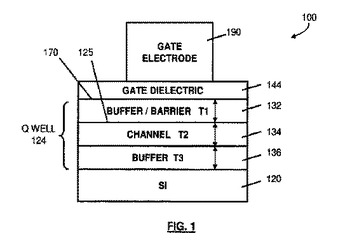

金属ソース/ドレイン及びコンフォーマル再成長ソース/ドレインにより発生される一軸性歪みを有する量子井戸MOSFETチャネル

開示の実施形態は、MOSチャネル領域に一軸性歪みを与える金属ソース/ドレイン及びコンフォーマル再成長ソース/ドレインを備えた、歪みトランジスタ量子井戸(QW)チャネル領域を含む。チャネル層の除去された部分が、チャネル材料の格子間隔とは異なる格子間隔を有するジャンクション材料で充填されることで、量子井戸の頂部バリア層及び底部バッファ層によってチャネル層に発生される二軸性歪みに加えて、一軸性歪みがチャネルに発生される。  (もっと読む)

(もっと読む)

半導体基板の製造方法、半導体基板、電子デバイスの製造方法、および反応装置

【課題】耐熱性の低い部分を有する基板に加熱処理をして半導体基板を製造する。

【解決手段】単結晶層を有し熱処理される被熱処理部と、熱処理で加えられる熱から保護されるべき被保護部とを備えるベース基板を熱処理して半導体基板を製造する方法であって、被保護部の上方に、ベース基板に照射される電磁波から被保護部を保護する保護層を設ける段階と、ベース基板の全体に電磁波を照射することにより被熱処理部をアニールする段階とを備える半導体基板の製造方法を提供する。

(もっと読む)

半導体基板の製造方法、半導体基板、電子デバイスの製造方法、および反応装置

【課題】耐熱性の低い部分を有する基板であっても加熱処理が可能となる、基板の熱処理方法を提供する。

【解決手段】熱処理される被熱処理部を備えるベース基板を熱処理して半導体基板を製造する方法であって、電磁波を吸収して熱を発生し、被熱処理部を選択的に加熱する被加熱部をベース基板上に設ける段階と、ベース基板に電磁波を照射する段階と、被加熱部が電磁波を吸収することにより発生する熱によって、被熱処理部の格子欠陥密度を低減する段階とを備える半導体基板の製造方法を提供する。

(もっと読む)

141 - 160 / 619

[ Back to top ]