Fターム[5F140BA05]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 基板材料 (9,253) | 4族 (5,747) | SiGe (619)

Fターム[5F140BA05]に分類される特許

61 - 80 / 619

半導体装置および半導体装置の製造方法

【課題】ゲート電極に注入された不純物に起因するゲートリークを低減させる。

【解決手段】ゲート電極14が形成されたアクティブ領域による被覆率が50%以上かつその面積が0.02mm2以上の領域において、多結晶シリコン膜14´に炭素15を導入してから、多結晶シリコン膜14´にリン16を導入し、多結晶シリコン膜14´をパターニングすることにより、ゲート絶縁膜13上にゲート電極14を形成する。

(もっと読む)

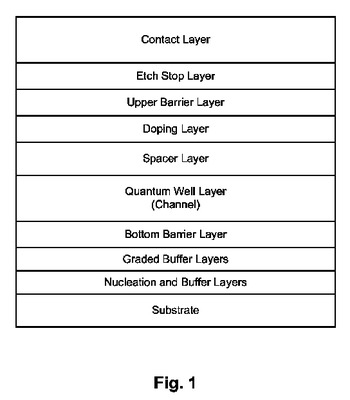

半導体装置の製造方法

【課題】ポリシリコンゲート電極の意図しないフルシリサイド化を防止する。

【解決手段】基板17上に、ゲート絶縁膜12およびシリコン層10をこの順に積層した積層体(10、12)を形成する工程と、積層体(10、12)の側壁沿いにSiN膜を有するオフセットスペーサ13を形成する工程と、その後、シリコン層10の上面を、薬液を用いて洗浄する工程と、その後、少なくともシリコン層10の上面を覆う金属膜19を形成する工程と、その後、加熱する工程と、を有し、オフセットスペーサ13が有するSiN膜は、ALD法を用いて450℃以上で成膜されたSiN膜、または、1Gpa以上の引張/圧縮応力を有するSiN膜であり、前記薬液は、重量比率で、HF/H2O=1/100以上であるDHF、または、バッファードフッ酸である半導体装置の製造方法を提供する。

(もっと読む)

半導体装置の製造方法

【課題】 フィン型MISトランジスタ、プレーナ型MISトランジスタ及び抵抗素子を集積化した半導体装置において、的確な製造方法を提供する。

【解決手段】 フィン部10aを形成する工程と、フィン部の側面に第1のゲート絶縁膜14及び第1のゲート電極膜15を形成する工程と、フィン部並びにフィン部の側面に形成された第1のゲート絶縁膜及び第1のゲート電極膜を囲み、第1のゲート電極膜に接する半導体導電部16aを形成する工程と、半導体導電部上並びにプレーナ型MISトランジスタ形成領域及び抵抗素子形成領域に、第2のゲート絶縁膜20及び第2のゲート電極膜21を形成する工程と、半導体導電部上及び抵抗素子形成領域に形成された第2のゲート絶縁膜及び第2のゲート電極膜を除去する工程と、半導体導電部上並びにプレーナ型MISトランジスタ形成領域及び抵抗素子形成領域に、抵抗素子用の半導体膜を形成する工程とを備える。

(もっと読む)

フィン型FETを有する半導体装置およびその製造方法

【課題】横方向延伸を減少し、素子サイズを小さくすることができる半導体装置を提供する。

【解決手段】半導体基板上に延伸し、STI領域を間に有する第1および第2のフィンを形成する。STI領域の上面と第1および第2のフィンの上面の間の寸法を第1の高さとし、STI領域の第1と第2のフィンとの間の間隙内に誘電材料を堆積し、STI領域の上面上に上面を有して、誘電材料の上面と第1および第2のフィンの上面との寸法を第2の高さとし、第2の高さは、第1の高さより低くなるように誘電材料を堆積した後、第1および第2のフィン上でそれぞれ誘電体の上方に、第1および第2のフィン延伸をエピタキシャル成長で形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】トンネルFETの閾値ばらつきの抑制をはかる。

【解決手段】Si1-x Gex (0<x≦1)の第1の半導体層13上にゲート絶縁膜21を介して形成されたゲート電極22と、Geを主成分とする第2の半導体と金属との化合物で形成されたソース電極24と、第1の半導体と金属との化合物で形成されたドレイン電極25と、ソース電極24と第1の半導体層13との間に形成されたSi薄膜26とを具備した半導体装置であって、ゲート電極22に対しソース電極24のゲート側端部とドレイン電極25のゲート側端部とは非対称の位置関係にあり、ドレイン電極25のゲート側の端部の方がソース電極24のゲート側の端部よりも、ゲート電極22の端部からゲート外側方向に遠く離れている。

(もっと読む)

半導体装置及びその製造方法

【課題】貼り合わせSOI基板を使用せずに、容易なプロセスにより、高速なMIS電界効果トランジスタを提供する。

【解決手段】p型のSi基板1上に、一部に空孔4を有するシリコン酸化膜2が設けられ、空孔4を挟んでシリコン酸化膜2上に延在したp型のSOIC基板(Si)5が設けられ、シリコン窒化膜3により素子分離されている。空孔4に自己整合して、SOIC基板5上にゲート酸化膜10を介してゲート電極11が設けられ、ゲート電極11の側壁にサイドウォール12が設けられ、SOIC基板5には、ゲート電極11に自己整合してn型ソースドレイン領域(7、8)及びサイドウォール12に自己整合してn型ソースドレイン領域(6、9)が設けられ、n型ソースドレイン領域には、バリアメタル15を有する導電プラグ16を介してバリアメタル18を有するCu配線19が接続されている構造からなるNチャネルのMIS電界効果トランジスタ。

(もっと読む)

半導体装置及びその製造方法

【課題】低容量且つ高温特性が良好な素子分離領域を有する高速なMIS電界効果トランジスタを提供する。

【解決手段】半導体基板1にウエル領域2が設けられ、ウエル領域2内には上部、下部及び側面にシリコン酸化膜3を有し、内部が空孔4に形成されたトレンチ素子分離領域が選択的に設けられ、トレンチ素子分離領域により画定されたウエル領域2が設けられた半導体基板1上にゲート酸化膜9を介してゲート電極10が設けられ、ゲート電極10の側壁にサイドウォール11が設けられ、ウエル領域2が設けられた半導体基板1には、ゲート電極10に自己整合して低濃度のソースドレイン領域(6、7)及びサイドウォール11に自己整合して高濃度のソースドレイン領域(5、8)が設けられ、高濃度のソースドレイン領域にはそれぞれバリアメタル14を有する導電プラグ15を介してバリアメタル17を有する配線18が接続されている構造からなるMIS電界効果トランジスタ。

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

幅広い電子デバイスのアレイ及びシステムにおける電力消費を低減する一式の新たな構造及び方法が提供される。これらの構造及び方法の一部は、大部分が、既存のバルクCMOSのプロセスフロー及び製造技術を再利用することで実現され、半導体産業及びより広いエレクトロニクス産業がコスト及びリスクを伴って代替技術へ切り替わることを回避可能にする。これらの構造及び方法の一部は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することと、チャネル領域にドーパントを有するFETの閾値電圧VTがより正確に設定されることとを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有することができ、それにより、DDCトランジスタにおける電力消費の有意義な動的制御が可能になる。様々な効果を達成するようDDCを構成する手法が数多く存在し得るとともに、ここに提示される更なる構造及び方法は、更なる利益を生み出すように単独あるいはDDCとともに使用され得る。  (もっと読む)

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

幅広い電子デバイスのアレイ及びシステムにおける電力消費を低減する一式の新たな構造及び方法が提供される。これらの構造及び方法の一部は、大部分が、既存のバルクCMOSのプロセスフロー及び製造技術を再利用することで実現され、半導体産業及びより広いエレクトロニクス産業がコスト及びリスクを伴って代替技術へ切り替わることを回避可能にする。これらの構造及び方法の一部は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することと、チャネル領域にドーパントを有するFETの閾値電圧VTがより正確に設定されることとを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有することができ、それにより、DDCトランジスタにおける電力消費の有意義な動的制御が可能になる。  (もっと読む)

(もっと読む)

二種類の仕事関数メタルを備える半導体装置

【課題】高誘電率ゲート絶縁膜を備える半導体装置の閾値電圧を適切に制御すること。

【解決手段】半導体装置の形成方法は、仕事関数メタルを含むダミーメタルゲート層をベース絶縁膜の直上に形成することと、アニーリングによって仕事関数メタルをベース絶縁膜中に拡散させることと、ウェットエッチングによってダミーメタルゲート層を除去することと、ベース絶縁膜211、212上に高誘電率ゲート絶縁膜213、213を形成することと、高誘電率ゲート絶縁膜213上にメタルゲート214、215を形成することと、を含む。

(もっと読む)

電界効果型トランジスタ、半導体メモリ、表示素子、画像表示装置及びシステム

【課題】比誘電率が高くリーク電流の少ない絶縁膜を提供する。

【解決手段】基板と、前記基板上に形成されたソース電極、ドレイン電極、及びゲート電極と、前記ゲート電極に所定の電圧を印加することによりソース電極とドレイン電極との間にチャネルが形成される半導体層を有し、前記ゲート電極と前記半導体層の間にゲート絶縁層と、を備え、前記ゲート絶縁層は、アルカリ土類金属の中から選ばれた1または2種類以上の元素と、Ga、Sc、Y、及びCeを除くランタノイドの中から選ばれた1または2種類以上の元素とを含むアモルファス複合金属酸化物絶縁膜により形成されていることを特徴とする電界効果型トランジスタを提供することにより上記課題を解決する。

(もっと読む)

半導体装置及びその製造方法

【課題】側面に(110)面が形成されたGe若しくはSiGeのフィン構造を実現することができ、FinFET等の素子特性の向上に寄与する。

【解決手段】Ge若しくはSiGeのフィン構造部を有する半導体装置であって、Si基板10の表面部に、一方向に長いストライプ領域を挟むように埋め込み形成され且つ基板表面よりも高い位置まで形成された素子分離絶縁膜12と、ストライプ領域上に形成され、且つ最上面が前記素子分離絶縁膜の最上面よりも低い位置にあるSiGeバッファ層14と、バッファ層14上に形成され、該層14よりも一方向と直交する方向の幅が狭く基板面と垂直な(110)面を有するGeフィン構造16と、を備えた。

(もっと読む)

最適化されたチャンネル領域を有するMOSトランジスタを具備する半導体素子

【課題】 MOSトランジスタを備える半導体素子を提供する。

【解決手段】 半導体素子は、半導体基板の所定領域に形成されて活性領域を区画する素子分離膜を有する。第1活性領域9a及び第2活性領域9bは(100)面の中心上面9t及び中心上面9tから素子分離膜14に向けて延びる傾斜エッジ面9eを有する。第1活性領域9a及び第2活性領域9bの中心上面9t及び傾斜エッジ面9eは第1半導体パターン15a及び第2半導体パターン15bで覆われる。第1半導体パターン15a及び第2半導体パターン15bは中心上面9tに平行な(100)面の平坦な上面15t及び平坦な上面に実質的に垂直な側壁15sを有する。第1半導体パターン15a及び第2半導体パターン15bの上部を通って側壁に交差する方向に第1ゲートパターン26a及び第2ゲートパターン26bが配置される。

(もっと読む)

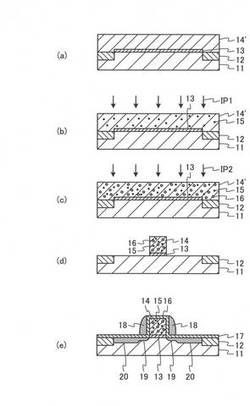

ゲルマニウムベースの量子井戸デバイス

量子井戸トランジスタは、ゲルマニウムの量子井戸チャネル領域を有する。シリコンを含有したエッチング停止領域が、チャネル近くへのゲート誘電体の配置を容易にする。III−V族材料のバリア層がチャネルに歪みを付与する。チャネル領域の上及び下の傾斜シリコンゲルマニウム層によって性能が向上される。複数のゲート誘電体材料によって、high−k値のゲート誘電体の使用が可能になる。  (もっと読む)

(もっと読む)

単結晶ゲルマニウムまたはシリコンゲルマニウムを形成する方法

【課題】基板中に形成されたトレンチ中に、単結晶のゲルマニウムまたはシリコンゲルマニウムを形成する改良された方法を提供する。

【解決手段】誘電体分離3(例えばSTI)を有する基板1を準備する工程と、基板材料1(例えばSi)のトレンチエッチング4を行う工程と、トレンチ4内への充填層5(例えばGe)の選択成長を行う工程と、略溶融温度での充填層6の加熱により、充填層5(例えばGe)の再結晶化7により達成される。

(もっと読む)

量子井戸トランジスタへのコンタクトを形成する方法

半導体へテロ構造内に形成されたデバイスへの低抵抗自己整合コンタクトを供する方法が開示されている。当該方法はたとえば、III-V族及びSiGe/Ge材料系において作製される量子井戸トランジスタのゲート、ソース、及びドレイン領域へのコンタクトを形成するのに用いられてよい。ゲートへのソース/ドレインコンタクト間に比較的大きな空間を生成してしまう従来のコンタクト作製処理の流れとは異なり、当該方法により供されたソースとドレインのコンタクトは自己整合され、各コンタクトは、ゲート電極に対して位置合わせされ、かつ、スペーサ材料を介して前記ゲート電極から分離される。  (もっと読む)

(もっと読む)

非平面ゲルマニウム量子井戸デバイス

非平面(ノンプレーナ)ゲルマニウム量子井戸構造を形成する技術が開示される。量子井戸構造は、IV族又はIII−V族の半導体材料を用いて実現されることができ、ゲルマニウムフィン構造を含む。一例において、非平面量子井戸デバイスが提供され、このデバイスは、基板(例えば、シリコン上にSiGe又はGaAsのバッファを有する)と、IV族又はIII−V族材料のバリア層(例えば、SiGe、GaAs又はAlGaAs)と、ドーピング層(例えば、デルタ/変調ドープされる)と、アンドープのゲルマニウム量子井戸層とを有する量子井戸構造を含む。アンドープのゲルマニウムフィン構造が量子井戸構造内に形成され、該フィン構造上に頂部バリア層が堆積される。ゲートメタルが、フィン構造を横切って堆積される。ドレイン/ソース領域がフィン構造のそれぞれのエンドに形成され得る。  (もっと読む)

(もっと読む)

FinFETとトライゲートデバイス用のラップアラウンド型コンタクト

サブストレートとサブストレートの上に形成された半導体ボディを有する半導体デバイスである。半導体ボディはソース領域とドレイン領域を有している。ソース領域、ドレイン領域、またはその組み合わせは、第一の側面、第二の側面、及び上面を有している。第一の側面は第二の側面と向かい合っており、上面は底面と向かい合っている。ソース領域、ドレイン領域、またはその組み合わせは、実質的に全ての第一の側面の上に、実質的に全ての第二の側面の上に、そして上面の上に、形成されたメタル層を有している。  (もっと読む)

(もっと読む)

ドープされたエピタキシャル領域を有する半導体装置およびその製造方法

本発明の実施例として、半導体装置上のエピタキシャル領域を示した。ある実施例では、エピタキシャル領域は、成膜−エッチングプロセスを経て基板に成膜される。周期的な成膜−エッチングプロセスの間に、スペーサの下側に形成されるキャビティは、エピタキシャルキャップ層によって埋め戻される。エピタキシャル領域およびエピタキシャルキャップ層は、チャネル領域での電子移動度を改善し、短チャネル効果が抑制され、寄生抵抗が低下する。  (もっと読む)

(もっと読む)

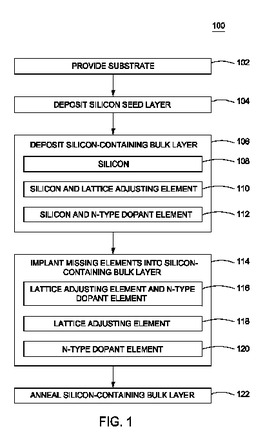

NMOSエピ層の形成方法

制御されたチャネル歪みおよび接合抵抗を有するNMOSトランジスタ、およびその製造方法が、本明細書で提供される。いくつかの実施形態において、NMOSトランジスタを形成するための方法は、(a)p型シリコン区域を有する基板を準備すること、(b)p型シリコン区域の上にシリコンシード層を堆積すること、(c)シリコン、シリコンおよび格子調整元素またはシリコンおよびn型ドーパントを備えるシリコン含有バルク層をシリコンシード層の上に堆積すること、(d)(c)で堆積されたシリコン含有バルク層に欠けている格子調整元素またはn型ドーパントのうちの少なくとも1つをシリコン含有バルク層の中に注入すること、(e)(d)の注入の後、シリコン含有バルク層をエネルギービームを用いてアニールすることを含むことができる。いくつかの実施形態において、基板は、その中に画定されたソース/ドレイン区域を有する、部分的に製造されたNMOSトランジスタデバイスを備えることができる。  (もっと読む)

(もっと読む)

61 - 80 / 619

[ Back to top ]