Fターム[5F140BA05]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 基板材料 (9,253) | 4族 (5,747) | SiGe (619)

Fターム[5F140BA05]に分類される特許

21 - 40 / 619

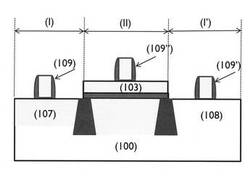

ハイブリッドMOSFETデバイスの製造方法およびそれにより得られるハイブリッドMOSFET

【課題】第1および第2のチャネル材料をそれぞれ有する第1MOSFETと第2MOSFETを含むハイブリッドMOSFETデバイスの製造方法を提供する。

【解決手段】III−Vオン絶縁体スタックは、続いて第1基板に接続される第2基板の上に形成される。III−V層103および絶縁体層は第1領域から選択的に除去されて、これにより第1基板の半導体層が露出する。第1MOSFETの第1ゲートスタック109は第1領域の露出した半導体層上に形成される。第2MOSFETの第2ゲートスタック109’は第2領域のIII−V層の上に形成される。

(もっと読む)

ゲート電極が駆動する電界効果型トランジスタおよびそれを有するセンサデバイス

【課題】 ゲート電極が可動な電界効果型トランジスタを提供する。

【解決手段】 半導体層と、前記半導体層内に少なくとも2つの活性領域と、前記活性領域に接するソース電極およびドレイン電極と、前記ソース電極と前記ドレイン電極との間の半導体層の上に絶縁層とゲート電極とを有する電界効果型トランジスタであって、

前記電界効果型トランジスタは前記ゲート電極および前記絶縁層の間に配置される、分子を吸着するための吸着部位を有し、

前記ゲート電極を駆動するための駆動手段を有することを特徴とする電界効果型トランジスタ。

(もっと読む)

半導体装置及びその製造方法

【課題】下地絶縁膜の膜厚精度の向上とトランジスタ特性の変動抑制との両立が図られたMISトランジスタを備えた半導体装置、及びその製造方法を提供する。

【解決手段】半導体装置は、半導体基板100における活性領域103a上に形成されたゲート絶縁膜108aと、ゲート絶縁膜108a上に形成されたゲート電極111aとを有するMISトランジスタ170を備えている。ゲート絶縁膜108aは、活性領域103a上に形成された板状の下層ゲート絶縁膜210aと、下層ゲート絶縁膜210a上に形成された断面形状が凹状の上層ゲート絶縁膜211aとを有する。下層ゲート絶縁膜210aは、活性領域103a上に形成された下地絶縁膜104aと、第1の高誘電率絶縁膜106aとで構成され、上層ゲート絶縁膜211aは、第1の高誘電率絶縁膜106a上に形成された第2の高誘電率絶縁膜107aで構成される。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体基板の転移を防止しつつ、絶縁膜の埋め込み性を確保するとともに、エッチング耐性を向上させる。

【解決手段】シリコン含有無機ポリマー膜8にアルカリ金属元素またはアルカリ土類金属元素を含有させ、塗布法などの方法にてトレンチ6内に埋め込まれるようにしてシリコン含有無機ポリマー膜8をライナー膜7上に形成し、水蒸気を含む雰囲気中でシリコン含有無機ポリマー膜8の酸化処理を行うことにより、シリコン含有無機ポリマー膜8をシリコン酸化膜9に変化させる。

(もっと読む)

半導体基板、半導体装置及びその製造方法

【課題】キャリア移動度(チャネル移動度)を増加させて、オン電流を増加させること。

【解決手段】トランジスタを形成するための半導体基板(10)は、主面(11a)を持つシリコン基板(11)と、このシリコン基板(11)の主面(11a)上に形成された歪緩和SiGe層(12)と、この歪緩和SiGe層(12)上に形成された歪Si層(13)と、を含む。

(もっと読む)

半導体装置、および、その製造方法

【課題】製造効率の向上、コストダウン、信頼性の向上を実現する。

【解決手段】第1導電型の第1電界効果トランジスタを第1基板に設ける。そして、第1導電型と異なる第2導電型の第2電界効果トランジスタを第2基板に設ける。そして、第1基板と第2基板とのそれぞれを対面させて貼り合わせる。そして、第1電界効果トランジスタと第2電界効果トランジスタとの間を電気的に接続させる。

(もっと読む)

電子装置

【課題】 信頼性及び色再現性の高い電子装置を提供する。

【解決手段】 単結晶半導体基板11上にスイッチング用FET201及び電流制御用FET202を形成し、電流制御用FET202にEL素子203が電気的に接続された画素構造とする。電流制御用FET202は画素間での特性ばらつきが極めて小さく、色再現性の高い画像を得ることができる。電流制御用FET202にホットキャリア対策を施すことで信頼性の高い電子装置が得られる。

(もっと読む)

電界効果トランジスタ

【課題】急峻なS値特性を有するとともに、ソース/ドレイン領域が同じ導電型となる対称構造を有する電界効果トランジスタを提供する。

【解決手段】本実施形態による電界効果トランジスタは、半導体層と、前記半導体層に離間して設けられたソース領域およびドレイン領域と、前記ソース領域と前記ドレイン領域との間の前記半導体層上に設けられたゲート絶縁膜と、前記ゲート絶縁膜上に設けられたゲート電極と、前記ソース領域および前記ドレイン領域側の前記ゲート電極の少なくとも一方の側面に設けられた高誘電体のゲート側壁と、を備え、前記ソース領域および前記ドレイン領域は前記ゲート電極の対応する側面から離れている。

(もっと読む)

半導体装置

【課題】 素子特性の劣化を抑制する。

【解決手段】 実施形態による半導体装置は、トランジスタ領域を有する半導体装置であって、トランジスタ領域は、基板上に形成された半導体領域と、半導体領域に隣接する素子分離領域と、ラテラルエピタキシャル層を備え、半導体領域上及び半導体領域と素子分離領域との間で横方向に成長するエピタキシャル層と、を具備する。

(もっと読む)

TiC膜を含む半導体構造を形成する方法

【課題】 TiC膜を含む半導体構造を形成する方法を提供する。

【解決手段】 高誘電率(k)の誘電体14および界面層12を含む積層体を基板10の表面上に設けるステップと、Heによって希釈された炭素(C)源およびArを含む雰囲気において、Tiターゲットをスパッタすることにより、前記積層体上にTiC膜16を形成するステップとを含む、半導体構造を形成する方法である。

(もっと読む)

半導体装置及び半導体基板の重水素処理装置

【課題】シリコンカーバイド領域を含む半導体基板上に形成された金属-絶縁膜-半導体構造を有する半導体装置(電界効果型トランジスタ(MISあるいはMOSFET))に対して、高温に加熱された熱触媒体表面での重水素を含んだガスの熱触媒作用によって生成された活性化した重水素を用いることにより、600°C以下の低温においてゲート絶縁膜/シリコンカーバイド半導体界面近傍に存在するダングリングボンドの重水素終端を図り、界面準位密度の低い良好なゲート酸化膜/半導体界面が形成された半導体装置、およびそれを形成する重水素処理装置およびその作製方法を提供する。

【解決手段】半導体基板とゲート絶縁膜、層間絶縁膜、配線層、保護絶縁膜等の半導体装置に形成される膜又は層の界面近傍での重水素元素濃度が1x1019cm-3以上であることを特徴とする金属−絶縁膜−半導体(MIS)構造を有する半導体装置。

(もっと読む)

半導体記憶装置

【課題】GIDLによるホールの発生効率を向上させることが可能な半導体記憶装置を提供する。

【解決手段】フィン3の両側にゲート絶縁膜5を介して設けられ、フィン3にチャネル領域を形成するゲート電極Gと、チャネル領域間のボディ領域にホールを閉じ込めるポテンシャルバリアを形成する不純物拡散層6と、チャネル領域を挟み込むようにしてフィン3に形成されたソース層S/ドレイン層Dとを備え、データ‘1’が書き込まれる際にゲート電圧が負電位かつ基板バイアス電圧およびドレイン電圧が正電位に設定される。

(もっと読む)

半導体装置の製造方法

【課題】シリコン膜のエッチング時に膜厚方向中央部での括れの発生を防止する。

【解決手段】多結晶シリコン膜3の上部と下部はノンドープ層3a、3cにてそれぞれ構成され、多結晶シリコン膜3の中央部は不純物ドープ層3bにて構成され、多結晶シリコン膜3に凹部M1を形成した後、多結晶シリコン膜3の酸化処理にて凹部M1の表面にシリコン酸化膜6を形成し、凹部M1下の多結晶シリコン膜3を除去する。

(もっと読む)

半導体装置及びその製造方法

【課題】特性バラツキを低減することができるような半導体装置及びその製造方法を提供する。

【解決手段】本発明の実施形態にかかる半導体装置は、ゲート絶縁膜を介して基板の表面を第1導電型チャネル領域から酸化膜の一部までを覆い、且つ、第1導電型チャネル領域と酸化膜との間に開口部を有するゲート電極と、この開口部下の基板に形成された第2導電型ドリフト領域の第2の部分とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】 出力ポートの絶縁破壊電圧より低い絶縁破壊電圧を有することが可能な静電放電保護素子を備える半導体装置を提供する。

【解決手段】 半導体装置は、第1LDMOS素子1を含む出力ポートと、出力ポートを静電放電から保護し、第2LDMOS素子4及びバイポーラトランジスタ3から構成される静電放電保護素子2と、を備える。第1LDMOS素子1および第2LDMOS素子4は、それぞれゲート、第1導電型のドレイン領域、第2導電型のボディ領域、及び第1導電型のドレイン領域と第2導電型のボディ領域との間に形成された素子分離領域を備える。このとき、第2LDMOS素子4の絶縁破壊電圧は、第1LDMOS素子1の絶縁破壊電圧より低い。これにより、第1LDMOS素子1の静電破壊を防止することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル形成時のひずみ緩和の抑制を可能にすると共に、更にひずみを印加することを可能にする。

【解決手段】基板1と、基板上に形成されひずみを有する第1半導体層3と、第1半導体層3上に離間して設けられ、第1半導体層3と格子定数が異なる第2および第3半導体層8と、第2半導体層と第3半導体層8との間の第1半導体層3上に設けられたゲート絶縁膜4と、ゲート絶縁膜4上に設けられたゲート電極5と、を備え、第2半導体層および第3半導体層8直下の第1半導体層3の外表面領域をシリサイド3a、8aとする。

(もっと読む)

シリサイド化金属ゲートの形成のための方法

【課題】シリサイド化金属ゲートと、シリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物と、同ゲート構造物を製造する方法と、を提供する。

【解決手段】シリサイド化金属ゲートと、シリサイド化金属ゲートに接するシリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物を提供する。詳しくは、広義に、第一の厚さを有する第一のシリサイド金属のシリサイド化金属ゲートと、隣接する第二の厚さを有する第二の金属のシリサイド化ソース領域およびドレイン領域とを含み、第二の厚さは第一の厚さより薄く、シリサイド化ソース領域およびドレイン領域は少なくともシリサイド化金属ゲートを含むゲート領域の端に位置合わせした半導体構造物を提供する。さらに、シリサイド化金属ゲートと、シリサイド化金属ゲートに接するシリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物を製造する方法も提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性の劣化及び素子のばらつきを抑制しつつ、所望の閾値電圧を実現する。

【解決手段】実施形態による複数の閾値電圧を有する半導体装置500は、基板502と、第1の閾値電圧を有する基板上の第1のトランジスタ510と、第2の閾値電圧を有する基板上の第2のトランジスタ530とを具備する。第1のトランジスタは、基板の第1のチャネル領域上に形成された第1の界面層516と、第1の界面層上に形成された第1のゲート誘電体層518と、第1のゲート誘電体層上に形成された第1のゲート電極520,522とを具備する。第2のトランジスタは、基板の第2のチャネル領域上に形成された第2の界面層536と、第2の界面層上に形成された第2のゲート誘電体層538と、第2のゲート誘電体層上に形成された第2のゲート電極540,542とを具備する。第2の界面層は第1の界面層内になくかつSi、O及びNと異なる添加元素を有する。第1及び第2の閾値電圧は異なる。第1及び第2のトランジスタは同一の導電型である。

(もっと読む)

半導体装置およびその製造方法

【課題】Ge半導体層に、極浅かつ高濃度のキャリアからなるn型不純物領域を形成する。

【解決手段】n型とp型のうちの一方の導電型の半導体基板と、半導体基板表面に選択的に設けられ、一方の導電型と異なる導電型の一対の不純物拡散領域と、一対の不純物拡散領域により挟まれた半導体基板上に設けられたゲート絶縁層と、ゲート絶縁層の上に設けられたゲート電極とを備え、不純物拡散領域の少なくとも一部は、基板に含まれる不純物と同じ導電型で、かつ基板の不純物濃度より高い不純物濃度を有する。

(もっと読む)

半導体装置及び半導体基板の重水素処理装置

【課題】界面準位密度のゲート酸化膜/半導体界面が形成された半導体装置、および作製方法の提供。

【解決手段】半導体基板とゲート絶縁膜、層間絶縁膜、配線層、保護絶縁膜等の半導体装置に形成される膜又は層の界面近傍での重水素元素濃度が1x1019cm-3以上であることを特徴とする金属−絶縁膜−半導体(MIS)構造を有する半導体装置とする。シリコンカーバイド領域を含む半導体基板上に形成された金属-絶縁膜(あるいは酸化膜)-半導体(MISあるいはMOS)構造を有する半導体装置(電界効果型トランジスタ(MISあるいはMOSFET))に対して、高温に加熱された熱触媒体表面での重水素を含んだガスの熱触媒作用によって生成された活性化した重水素を用いることにより、600°C以下の低温においてゲート絶縁膜/シリコンカーバイド半導体界面近傍に存在するダングリングボンドの重水素終端を図る。

(もっと読む)

21 - 40 / 619

[ Back to top ]