Fターム[5F140BD01]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート絶縁膜 (8,730) | 2層 (822)

Fターム[5F140BD01]に分類される特許

141 - 160 / 822

半導体装置及びその製造方法

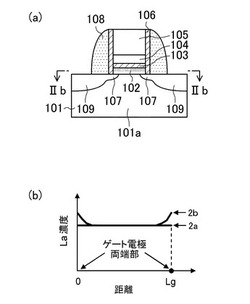

【課題】高誘電率ゲート絶縁膜、及び、ゲート電極としてメタル膜を含む半導体装置において、逆短チャネル効果の発生を防止して高性能化を実現する。

【課題手段】半導体装置は、半導体基板101の上に形成されたランタンを含有する高誘電率ゲート絶縁膜102と、高誘電率ゲート絶縁膜102の上に形成されたキャップ膜103と、キャップ膜103の上に形成されたメタル膜104と、メタル膜104の上に形成されたポリシリコン膜105と、高誘電率ゲート絶縁膜102、キャップ膜103、メタル膜104、及びポリシリコン膜105それぞれの両側面に形成されたランタンを含有するゲート側壁絶縁膜106とを備えている。

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

幅広い電子デバイスのアレイ及びシステムにおける電力消費を低減する一式の新たな構造及び方法が提供される。これらの構造及び方法の一部は、大部分が、既存のバルクCMOSのプロセスフロー及び製造技術を再利用することで実現され、半導体産業及びより広いエレクトロニクス産業がコスト及びリスクを伴って代替技術へ切り替わることを回避可能にする。これらの構造及び方法の一部は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することと、チャネル領域にドーパントを有するFETの閾値電圧VTがより正確に設定されることとを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有することができ、それにより、DDCトランジスタにおける電力消費の有意義な動的制御が可能になる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】MISトランジスタに適当なしきい値電圧が与えられる一方、抵抗素子はシリコン膜からなる抵抗体層の異常成長を抑制して、シリコン膜の膜厚を安定化する。

【解決手段】半導体装置は、半導体基板10の上部に形成された素子分離領域12によって囲まれた第1の活性領域10a、第1の活性領域の上に形成された第1の高誘電体膜14aを有する第1のゲート絶縁膜27a、及び第1のゲート絶縁膜の上に形成された第1のゲート電極28aとを有する第1導電型の第1のMISトランジスタ1aと、素子分離領域の上に形成された第2の高誘電体膜14x、及び該第2の高誘電体膜の上に形成されたシリコンからなる抵抗体層20xを有する抵抗素子1xとを備えている。第1の高誘電体膜と第2の高誘電体膜とは、互いに同一の高誘電体材料からなり、第1の高誘電体膜は第1の調整用金属を含み、第2の高誘電体膜は第1の調整用金属を含まない。

(もっと読む)

二種類の仕事関数メタルを備える半導体装置

【課題】高誘電率ゲート絶縁膜を備える半導体装置の閾値電圧を適切に制御すること。

【解決手段】半導体装置の形成方法は、仕事関数メタルを含むダミーメタルゲート層をベース絶縁膜の直上に形成することと、アニーリングによって仕事関数メタルをベース絶縁膜中に拡散させることと、ウェットエッチングによってダミーメタルゲート層を除去することと、ベース絶縁膜211、212上に高誘電率ゲート絶縁膜213、213を形成することと、高誘電率ゲート絶縁膜213上にメタルゲート214、215を形成することと、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】MISトランジスタにおけるシリコン混晶層からなるソースドレイン領域を、不純物の拡散による不具合を防止しながらチャネル領域に近づけることができるようにする。

【解決手段】半導体装置は、半導体基板10からなるn型の活性領域の上に、ゲート絶縁膜12を介在させて形成されたゲート電極13と、活性領域におけるゲート電極13の両側方の領域に形成されたp型ソースドレイン領域20と、活性領域における各p型ソースドレイン領域20の側面からそれぞれゲート電極13の下側に向かって形成されたn型ポケット領域18とを有している。p型ソースドレイン領域20は、シリコンとIV族元素との混晶層からなり、混晶層は、ゲート長方向におけるゲート電極側の側面がゲート電極側に突き出す凸部20aを有している。凸部20aの先端は、ポケット領域18によって覆われている。

(もっと読む)

半導体デバイスの製造方法および半導体デバイス

【課題】下地膜の結晶性の影響を抑え、高誘電率の結晶構造としたキャパシタ絶縁膜とする。

【解決手段】基板200の上に形成された結晶質膜310の上に非晶質膜320を形成する非晶質膜形成工程と、非晶質膜320の上に結晶質膜310の結晶構造とは独立して制御される結晶構造を持つ絶縁膜330を形成する結晶性絶縁膜形成工程と、を有する。結晶性絶縁膜形成工程においては、基板200を加熱して前記絶縁膜330の少なくとも一部を正方晶系へ相転移させる相転移工程と、を有する。

(もっと読む)

半導体装置の製造方法、基板処理方法及び基板処理装置

【課題】 金属膜の酸化に起因する特性劣化を最小限に抑えることができる半導体装置の製造方法及び基板処理装置を提供する。

【解決手段】 処理容器内に基板を搬入する工程と、処理容器内に処理ガスを供給し排気して化学的蒸着法により基板上に金属膜を形成する工程と、処理容器内にアルミニウム原子を含む原料ガスと窒素原子を含むガスとを供給し排気して化学的蒸着法により金属膜上に窒化アルミニウム膜を形成する工程と、金属膜および窒化アルミニウム膜形成後の基板を処理容器内から搬出する工程と、を有し、金属膜を形成する工程と窒化アルミニウム膜を形成する工程は、処理容器内を非酸素雰囲気に保った状態で連続的に行われる。

(もっと読む)

BiCMOSプロセス技術における高電圧SCRMOS

集積回路が、ドレイン領域(1010)及びSCR端子(1012)の周りに、低減された表面フィールド(RESURF)領域(1024)と共に形成されるSCRMOSトランジスタを含む。RESURF領域は、ドリフト領域(1014)と同じ導電型であり、ドリフト領域(1014)より一層重くドープされる。  (もっと読む)

(もっと読む)

誘電体膜の製造方法

【課題】比誘電率の低下を軽減しつつリーク電流値を低減し、スパッタ率の低下による堆積速度の減少を抑制し、かつ、面内均一性に優れた誘電体膜の製造方法を提供すること。

【解決手段】本発明の一実施形態に係る誘電体膜の製造方法は、基板上に、AlとSiとOを主成分とする金属酸化物である誘電体膜を形成する誘電体膜の製造方法であって、Al元素とSi元素のモル比率Si/(Si+Al)が0<(B/(A+B))≦0.1であり、非晶質構造を有する金属酸化物を形成する工程と、該非晶質構造を有する金属酸化物に1000℃以上のアニール処理を施し、結晶相を含む金属酸化物を形成する工程と、を備える。

(もっと読む)

半導体装置、および、半導体装置の製造方法

【課題】ゲート電極構造の垂直方向の抵抗を低減する。

【解決手段】半導体基板1と、半導体基板1の上に形成されたゲート絶縁膜2と、ゲート絶縁膜2の上に形成された仕事関数制御層3と、仕事関数制御層3の上に形成された第1のシリサイド層4と、第1のシリサイド層4の上に形成されたポリシリコンゲート電極5と、ポリシリコンゲート電極5の下の半導体基板1中の領域を挟んで半導体基板1中に形成されるソース領域6およびドレイン領域7と、を有する半導体装置を提供する。

(もっと読む)

BiCMOSプロセス技術における高電圧SCRMOS

集積回路(1000)が、中央配置のドレイン拡散領域(1008)及び分散型SCR端子(1010)を備える1つのドレイン構造(1006)と、分散型ドレイン拡散領域(1016)及びSCR端子(1018)を備える別のドレイン構造(1012)とを含むSCRMOSトランジスタを有する。中央配置のドレイン拡散領域とソース拡散領域との間のMOSゲート(1022)がソース拡散領域へ短絡される。SCRMOSトランジスタを有する集積回路を形成するためのプロセスも開示される。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート長が短い微細構造を有しながら、低消費電力でかつ高速動作が可能なMISFETを有する半導体装置を提供する。

【解決手段】シリコン基板と、このシリコン基板上にシリコン含有絶縁膜を介して設けられた高誘電率金属酸化膜を有するゲート絶縁膜と、このゲート絶縁膜上に形成されたシリコン含有ゲート電極とを有し、少なくとも前記高誘電率金属酸化膜の側面側に窒素含有部を有するMIS型電界効果トランジスタを備えた半導体装置。

(もっと読む)

最適化されたチャンネル領域を有するMOSトランジスタを具備する半導体素子

【課題】 MOSトランジスタを備える半導体素子を提供する。

【解決手段】 半導体素子は、半導体基板の所定領域に形成されて活性領域を区画する素子分離膜を有する。第1活性領域9a及び第2活性領域9bは(100)面の中心上面9t及び中心上面9tから素子分離膜14に向けて延びる傾斜エッジ面9eを有する。第1活性領域9a及び第2活性領域9bの中心上面9t及び傾斜エッジ面9eは第1半導体パターン15a及び第2半導体パターン15bで覆われる。第1半導体パターン15a及び第2半導体パターン15bは中心上面9tに平行な(100)面の平坦な上面15t及び平坦な上面に実質的に垂直な側壁15sを有する。第1半導体パターン15a及び第2半導体パターン15bの上部を通って側壁に交差する方向に第1ゲートパターン26a及び第2ゲートパターン26bが配置される。

(もっと読む)

ゲルマニウムベースの量子井戸デバイス

量子井戸トランジスタは、ゲルマニウムの量子井戸チャネル領域を有する。シリコンを含有したエッチング停止領域が、チャネル近くへのゲート誘電体の配置を容易にする。III−V族材料のバリア層がチャネルに歪みを付与する。チャネル領域の上及び下の傾斜シリコンゲルマニウム層によって性能が向上される。複数のゲート誘電体材料によって、high−k値のゲート誘電体の使用が可能になる。  (もっと読む)

(もっと読む)

半導体装置

【課題】 占有面積の増加もなく、十分なESD保護機能を持たせたESD保護用のN型のMOSトランジスタを有する半導体装置を得ることを目的とする。

【解決手段】 絶縁膜が埋め込まれたトレンチ素子分離領域と、凹部に周囲をゲート絶縁膜で覆われたゲート電極が埋め込まれたトレンチチャネル領域と、絶縁膜が埋め込まれた凹部の周囲を濃いN型の拡散層で覆ったトレンチドレイン領域とが形成されており、ESD保護用のN型MOSトランジスタのチャネル領域には、トレンチチャネル領域が形成され、なおかつESD保護用のN型MOSトランジスタのドレイン領域には、トレンチドレイン領域が形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】Geを含む半導体で構成されるチャネル領域を有するP型FETにおいて、逆短チャネル特性の発生を抑制しつつ、短チャネル特性を改善する。

【解決手段】半導体装置は、半導体基板100上に形成されたP型FETを備えている。P型FETは、半導体基板100上に形成され、Geを含有する第1の半導体層103と、第1の半導体層103上に形成され、第1の半導体層103よりも低濃度のGeを含有する第2の半導体層104と、第2の半導体層104上にゲート絶縁膜107aを間に挟んで形成されたゲート電極110aと、第2の半導体層104のうちゲート電極110aの両側方に位置する部分に形成されたp型エクステンション領域111aと、第1の半導体層103内に設けられ、且つp型エクステンション領域111aの下に形成されたn型不純物領域152とを有している。

(もっと読む)

絶縁ゲート型半導体素子及び絶縁ゲート型半導体集積回路

【課題】耐放射線性を有する絶縁ゲート型半導体素子、絶縁ゲート型半導体集積回路を提供する。

【解決手段】一部がチャネル領域をなすp型の半導体層11と、半導体層11の上部に活性領域21Bを定義する素子分離絶縁膜21と、チャネル領域にキャリア注入口を介してキャリアを注入するn型の第1主電極領域12と、チャネル領域から、キャリアを排出するキャリア排出口を有するn型の第2主電極領域13と、活性領域21Bの上に設けられたゲート絶縁膜22と、ゲート絶縁膜22の上に設けられ、第1主電極領域12と第2主電極領域13との間を流れるキャリアの流路に直交する主制御部、主制御部に交わる2本のガード部241,242を有してπ字型をなすゲート電極24と、第2主電極領域13のゲート幅方向の両端側に設けられたp型のリーク阻止領域61,62とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】短チャネル効果の発生を抑制できる半導体装置及びその製造方法の提供。

【解決手段】本発明の半導体装置は、半導体基板1の活性領域上にゲート絶縁膜5aを介して形成されたゲート電極105と、ゲート電極105側面を覆う第1絶縁膜サイドウォール5bと、ゲート電極105を挟んで形成されたソース領域108S及びドレイン領域108Dにおいて、側面が第1絶縁膜サイドウォール5bに接して半導体基板1上面に形成されたシリコン層109と、第1絶縁膜サイドウォール5bを介してゲート電極105側面と対向し、底面がシリコン層109上面に接して形成された第2絶縁膜サイドウォール5dと、シリコン層109内下層部に設けられたLDD不純物層109aと、シリコン層109内上層部に設けられた高濃度不純物層109bと、LDD不純物層109aの下方、半導体基板1の表面側に形成されたポケット不純物層108aとを具備する。

(もっと読む)

絶縁ゲート型半導体素子及び絶縁ゲート型半導体集積回路

【課題】RTSノイズを低減することが可能な絶縁ゲート型半導体素子、絶縁ゲート型半導体集積回路を提供する。

【解決手段】チャネル領域として機能するp型の半導体層11と、チャネル領域を少なくとも囲み、活性領域21Bを定義する素子分離絶縁膜21と、活性領域21Bの一方に設けられたn型の第1主電極領域12と、活性領域21Bの他方に設けられたn型の第2主電極領域13と、活性領域21B上に設けられたゲート絶縁膜22と、ゲート絶縁膜22上において、第1主電極領域12と第2主電極領域13との間のチャネル領域を流れるキャリアの流路に直交する方向に伸延するゲート電極24とを備え、チャネル領域への前記キャリアの注入口が素子分離絶縁膜21から離間して設けられている。

(もっと読む)

半導体装置の製造方法

【課題】 高誘電体ゲート絶縁膜およびシリコン基板との界面を高品質化して、MISFETの特性向上を図る。

【解決手段】 シリコン基板11上にhigh−k膜21とゲート電極24を形成する半導体装置の製造方法において、high−k膜形成後にフッ素雰囲気でアニール処理23を施し、その後のプロセス温度を600℃以下で行う、半導体装置の製造方法。

(もっと読む)

141 - 160 / 822

[ Back to top ]