Fターム[5F140BD01]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート絶縁膜 (8,730) | 2層 (822)

Fターム[5F140BD01]に分類される特許

101 - 120 / 822

半導体素子、及び半導体装置

【課題】半導体素子の微細化に伴うゲート電極サイズの微細化においても、ゲート電極とチャネル形成領域間のリーク電流が抑制された半導体素子を提供することを課題の一とする。また、小型かつ高性能な半導体装置を提供することを課題の一とする

【解決手段】チャネル形成領域として機能する半導体層上に、ゲート絶縁膜として比誘電率が10以上の酸化ガリウムを含む絶縁膜を形成し、前記酸化ガリウム上にゲート電極が形成された構造を有する半導体素子を作製することにより、課題の一を解決する。また、前記半導体素子を用いて半導体装置を作製することにより、課題の一を解決する。

(もっと読む)

半導体装置の製造方法

【課題】高誘電率絶縁膜を含むゲート絶縁膜を備えた電界効果型トランジスタにおいてゲート絶縁膜におけるゲート電極の端部下に位置する部分の厚膜化を試みると、高誘電率絶縁膜が結晶化し、ゲートトンネルリーク電流の発生を抑制出来ない場合があった。

【解決手段】半導体装置では、半導体基板1上にはゲート絶縁膜2が形成され、ゲート絶縁膜2上にはゲート電極3が形成されている。ゲート絶縁膜2では、ゲート絶縁膜2におけるゲート電極3の両端部下に位置する厚膜部分2aの膜厚は、ゲート絶縁膜2におけるゲート電極3の中央部下に位置する中央部分2bの膜厚よりも厚い。

(もっと読む)

半導体基板の製造方法および半導体装置の製造方法

【課題】ノーマリーオフ半導体素子のための高品質の酸化物からなる絶縁膜を提供する。

【解決手段】半導体積層構造を有する基板3の上に、酸化物を含む絶縁膜を形成する工程において、酸化物を構成する元素単体ないしは元素の化合物を半導体積層構造を有する基板3の上に付着させる際に、水素ガス中に高純度水を加熱ないしは冷却することにより水蒸気圧を精密制御して混入させることにより、元素単体ないしは元素の化合物を酸化させる酸素分圧を精密に制御して、酸化物の組成を精密制御し、もって半導体積層構造を有する基板3と物理化学的に整合する絶縁膜を形成する。

(もっと読む)

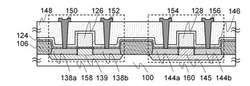

半導体装置の製造方法及び半導体装置

【課題】CMOS回路を構成するnチャネルMISFETとpチャネルMISFETの両者において、キャリア移動度を高めて高い性能を実現する半導体装置を提供する。

【解決手段】半導体基板の第1領域及び第2領域において第1ゲート絶縁膜及び第1ゲート電極(16,17)を形成し、第1ゲート電極の両側部における半導体基板中にソースドレイン領域を形成し、ソースドレイン領域の導電性不純物を活性化し、第1ゲート電極を被覆して全面に半導体基板に応力を印加するストレスライナー膜(27,28)を形成し、少なくとも第1領域に形成された部分のストレスライナー膜は残しながら第2領域における第1ゲート電極の上部部分のストレスライナー膜を除去し、第2領域における第1ゲート電極の上部を露出させて第1ゲート電極を全て除去して第2ゲート電極形成用溝Tを形成し、第2ゲート電極形成用溝内に第2ゲート電極(31,32)を形成する。

(もっと読む)

高誘電率のゲート絶縁膜を有する半導体装置及びそれの製造方法

【課題】本発明はゲート構造物として高誘電率を有する物質として、高誘電率を有する物質からなるゲート絶縁膜を含む半導体装置及びその製造方法に関する。

【解決手段】半導体装置及びその製造方法において、基板上に形成され、ハフニウムシリコン酸化物含有固体物質を含むゲート絶縁膜パターンと前記ゲート絶縁膜パターン上に形成される第1ゲート導電膜パターンを含むゲート構造物及び前記ゲート構造物と隣接する基板の表面部位に配置されており、n型不純物がドーピングされたソース/ドレイン領域を含むことを特徴とする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】縦型のトランジスタにおいてゲートからシリサイドの位置を精度よく制御できるようにする。

【解決手段】柱状半導体14の中央部には、その周囲を囲むように、ゲート絶縁膜9が形成され、さらに、ゲート絶縁膜9の周囲を囲むように、ゲート層6が形成されている。この柱状半導体14の中央部、ゲート絶縁膜9、ゲート層6により、MIS構造が形成されている。ゲート層6の上下には、第1絶縁膜4が形成されている。第1絶縁膜4は、柱状半導体14にも接している。柱状半導体14の側面には、シリサイド18及びn型拡散層(不純物領域)19が形成されている。シリサイド18は、第1絶縁膜4によってセルフ・アラインされた位置に形成されている。

(もっと読む)

電界効果半導体装置の製造方法

【課題】半導体装置を構成する半導体層の表面上にAlOx層を安価に形成でき、且つAlOx層を厚膜化できる半導体装置の製造方法を提供する。

【解決手段】半導体基板1と、前記半導体基板1上に形成された窒化物系化合物半導体層2、3、4と、前記窒化物系化合物半導体層2、3、4上に隣接して形成された酸化アルミニウム層7と、を備える半導体装置の製造方法であって、

前記窒化物系化合物半導体層2、3、4上に多結晶又は非晶質の窒化アルミニウム層6を形成する第1の工程と、前記多結晶又は非晶質の窒化アルミニウム層6を熱酸化して前記酸化アルミニウム層7を得る第2の工程と、を備えることを特徴とする半導体装置の製造方法。

(もっと読む)

半導体素子

【課題】選択的酸化工程を含む金属ゲートパターンを有する半導体素子を提供する。

【解決手段】半導体素子は、半導体基板、半導体基板上に形成されたポリシリコン層、ポリシリコン層上に形成されたバリヤ金属層、及びバリヤ金属層上に形成されたタングステン層を含み、側壁を有する金属ゲートパターンと、金属ゲートパターンの側壁上に形成されたシリコンオキサイド層と、金属ゲートパターンの側壁のシリコンオキサイド層上に形成されたシリコンナイトライド層と、を含む半導体素子であって、金属ゲートパターンは、90nm未満のゲート長を有し、シリコンオキサイド層は、ポリシリコン層の側壁に接触し、シリコンオキサイド層は、第1部分及び第2部分を含むが、第1部分は、ポリシリコン層の側壁の直接上に位置し、第2部分は、タングステン層の側壁上に位置し、第1部分は、第2部分よりさらに厚いことを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】pチャネル型の電界効果トランジスタのしきい値電圧を確実に制御して所望の特性が得られる半導体装置と、その製造方法とを提供する。

【解決手段】温度約700〜900℃のもとで施す熱処理に伴い、素子形成領域RPでは、アルミニウム(Al)膜7a中のアルミニウム(Al)がハフニウム酸窒化(HfON)膜6へ拡散することによって、ハフニウム酸窒化(HfON)膜6に元素としてアルミニウム(Al)が添加される。また、チタンアルミニウムナイトライド(TiAlN)膜からなるハードマスク8a中のアルミニウム(Al)とチタン(Ti)とがハフニウム酸窒化(HfON)膜6へ拡散することによって、ハフニウム酸窒化(HfON)膜6に元素としてアルミニウム(Al)とチタン(Ti)とが添加される。

(もっと読む)

電界効果トランジスタ

【課題】電界効果トランジスタにおいて、フィールドプレート終端での高電界の集中を緩和し、もって高耐圧半導体装置として利用可能とする。

【解決手段】本電界効果トランジスタ30は、GaN系エピタキシャル基板32の電子走行層上に、ゲート電極38を挟んで配置されたソース電極34及びドレイン電極36を備え、ゲート電極38の上部に、ドレイン電極36側及びソース電極34側に庇状に突き出したフィールドプレート40が形成され、基板32の表面層とフィールドプレート40との間に誘電体膜46が形成され、誘電体膜46は、フィールドプレート40のドレイン電極36側及びソース電極34側の終端面と面一状態となるように切れ込み、ドレイン電極36側の下端からドレイン電極36に接続するようにドレイン電極36に向かって延びており、且つ、ソース電極34側の下端からソース電極34に接続するようにソース電極34に向かって延びている。

(もっと読む)

半導体装置及びその製造方法

【課題】工数を大幅に増加せず且つ高誘電体からなるゲート絶縁膜にダメージを与えることがない、仕事関数変更用金属不純物膜の効果を有する半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板101と、半導体基板101の上部に形成されたp型活性領域110と、p型活性領域110の上に形成されたゲート絶縁膜150と、ゲート絶縁膜150の上に形成されたゲート電極106とを有している。ゲート絶縁膜150は、二酸化シリコンよりも大きい誘電率を有する高誘電体膜103と、高誘電体膜103の上に形成され、炭素を含む炭素含有膜104とを有している。高誘電体膜103及び炭素含有膜104は、第1の金属としてランタン又はマグネシウムを含み、ゲート電極106は、第2の金属を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、特性の安定したトランジスタを得ることが可能で、かつ複数の縦型トランジスタ間の特性のばらつきを抑制可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】半導体基板11の表面11aが部分的にエッチングされて形成され、縦壁面となる第1及び第2の側面26a,26bを含む内面によって区画された第2の溝26と、第2の溝26の第1及び第2の側面26a,26bを覆うゲート絶縁膜32と、ゲート絶縁膜32上に形成され、上端面37a,38aが半導体基板11の表面11aより低い位置にある第1の導電膜34、及び第1の導電膜34に形成され、上端面35aが第1の導電膜34の上端面34aより低い位置にある第2の導電膜35よりなるゲート電極33と、第2の溝26内に、半導体基板11の表面11aより低い位置に配置され、第2の導電膜35の上端面35aを覆う第1の絶縁膜17と、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化が進んだ場合であっても、適切なしきい値電圧を有するpチャネルMOSFETを含む半導体装置を製造する。

【解決手段】本発明に係る半導体装置の製造方法は、半導体基板101上に、SiO2またはSiONを含む第1ゲート絶縁層104を形成する第1ゲート絶縁層形成ステップと、第1ゲート絶縁層104上に、金属酸化物を含む第2ゲート絶縁層105を形成する第2ゲート絶縁層形成ステップと、第2ゲート絶縁層105上に、金属を含む第1電極106aを形成する第1電極形成ステップと、形成された積層構造に、複数回のミリセカンドアニール処理を行うことで、第2ゲート絶縁層105および第1電極106aの少なくとも一方に含まれる4族、5族または13族の元素を、第1ゲート絶縁層104と第2ゲート絶縁層105との界面に拡散させるアニールステップとを含む。

(もっと読む)

化合物半導体装置の製造方法及び化合物半導体装置

【課題】リフトオフ法を用いずに、簡易な手法で化合物半導体装置のゲート電極、ソース電極、及びドレイン電極を各種パターンに欠陥を生ぜしめることなく形成する。

【解決手段】AlGaN/GaN・HEMTを製造する際に、化合物半導体層上に保護絶縁膜8を形成し、保護絶縁膜8に開口を形成し、開口を埋め込む導電材料を保護絶縁膜8上に形成し、導電材料上の開口上方に相当する部位にマスクを形成し、マスクを用いて導電材料をエッチングしてゲート電極15(又はソース電極45及びドレイン46)を形成し、その後、保護絶縁膜8上に保護絶縁膜16を形成し、保護絶縁膜8,16に開口を形成し、開口を埋め込む導電材料を保護絶縁膜16上に形成し、導電材料上の開口上方に相当する部位にマスクを形成し、マスクを用いて導電材料をエッチングしてソース電極22及びドレイン23(又はゲート電極53)を形成する。

(もっと読む)

半導体装置の製造方法

【課題】キャップ材料を使用した半導体装置のウェハ面内における閾値電圧Vtのバラツキを抑制することを目的とする。

【解決手段】まず、半導体基板1001の上に、高誘電率ゲート絶縁膜1006及び第1のキャップ膜1008を順に形成する。次に、熱処理を行って、第1のキャップ膜1008中の第1の金属を高誘電体膜1006に拡散させる。その後、高誘電体膜1006に拡散せずに高誘電体膜1006の上に残存した第1のキャップ膜1008を除去して、第1の金属が拡散した高誘電率ゲート絶縁膜1006Aの上に金属電極1010を形成する。

(もっと読む)

半導体装置

【課題】本発明は、不純物拡散層と半導体基板との間に形成される空乏層中におけるGIDLを抑制することのできる半導体装置を提供することを課題とする。

【解決手段】半導体基板11の表面11aが部分的にエッチングされて形成された第2の溝32と、少なくとも第2の溝32の側面32aを覆うゲート絶縁膜38と、ゲート絶縁膜38を介して、第2の溝32の側面32aに形成され、その上端面45aが半導体基板11の表面11aより低い位置にあってゲート電極39となる第1の導電膜45と、第1の導電膜45に形成され、その上端面46aが第1の導電膜45の上端面45bよりも高く、かつ半導体基板11の表面11aより低い位置にあってゲート電極39となる第2の導電膜46と、第1の導電膜45の上端面45b、及び第1の導電膜45の上端面45bから突出した第2の導電膜46を覆うように、第2の溝32内に設けられた第2の絶縁膜と、を有する。

(もっと読む)

ノーマリオフ型GaN系電界効果トランジスタ

【課題】ゲート耐電圧が高くかつオン抵抗が低減されたノーマリオフ型GaN系FETを提供する。

【解決手段】ノーマリオフ型GaN系FETは、第1種GaN系半導体からなるチャネル層4と、このチャネル層上で互いに隔てて設けられた第2種GaN系半導体からなる一対の電子供給層5と、これら電子供給層の間でチャネル層を覆うゲート絶縁膜7と、チャネル層にオーミックコンタクトしているソース電極およびドレイン電極と、ゲート絶縁膜上に形成されたゲート電極とを備え、ゲート絶縁膜はチャネル層上に順次堆積された第1と第2の絶縁層を含み、第1絶縁層7aはSiの酸化物、窒化物および酸窒化物のいずれかからなりかつ5nm以下の厚さを有し、第2絶縁層7bは第1絶縁層に比べて大きなε×Ecを有し、ここでεは誘電率を表し、Ecは絶縁破壊電界を表している。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】低閾値動作が可能な電界効果トランジスタを提供する。

【解決手段】n型半導体領域2と、半導体領域に離間して形成されたソース領域およびドレイン領域12a、12bと、ソース領域12aとドレイン領域12bとの間の半導体領域上に形成され、シリコンと酸素を含む第1絶縁膜4と、第1絶縁膜上に形成され、Hf、Zr、Tiから選ばれた少なくとも1つの物質と酸素を含む第2絶縁膜8と、第2絶縁膜上に形成されたゲート電極10と、を備え、第1絶縁膜と第2絶縁膜との界面7aを含む界面領域7に、Geが導入されており、Geの面密度が、界面領域7内の第1絶縁膜4側においてピークを有している。

(もっと読む)

半導体装置及びその製造方法

【課題】SOI構造の縦型のMISFETの提供

【解決手段】Si基板1上に、一部に空孔4を有する絶縁膜2が設けられ、空孔4上及び絶縁膜2の一部上に横方向半導体層6が設けられ、半導体層6の側面の一部に導電膜3が接して設けられ、絶縁膜2により素子分離されている。半導体層6上の、空孔4直上部に縦方向半導体層7が設けられ、半導体層7の上部にドレイン領域(10,9)が設けられ、離間し、相対して下部にソース領域8が設けられ、ソース領域8は延在して、半導体層6全体に設けられている。半導体層7の全側面には、ゲート酸化膜11を介してゲート電極12が設けられ、ドレイン領域10、ゲート電極11及び導電膜3を介したソース領域8には、バリアメタル18を有する導電プラグ19を介してバリアメタル21を有する配線22が接続されている縦型のMISFET。

(もっと読む)

半導体装置の製造方法、及び半導体装置

【課題】電界効果トランジスタにおけるゲート電極の汚染を防止し、かつゲート電極上に形成されるマスク膜の膜厚を薄くする。

【解決手段】基板10上にゲート絶縁膜100を形成する。次いでゲート絶縁膜100上にゲート電極膜120を形成する。ゲート電極膜120の一部上にマスク膜230を形成する。マスク膜230をマスクとしたエッチングによりゲート電極膜120を選択的に除去する。そして、マスク膜230とゲート電極膜120の側面に接するようゲート側壁膜130を形成する。マスク膜230は少なくとも第1膜200、第2膜210、及び第3膜220をこの順に積層した積層膜により構成される。第2膜210は、ゲート側壁膜130に対して第3膜220よりも高いエッチング選択比を有する。第3膜220は、ゲート電極膜120に対して第2膜210よりも高いエッチング選択比を有する。

(もっと読む)

101 - 120 / 822

[ Back to top ]