Fターム[5F140BD01]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート絶縁膜 (8,730) | 2層 (822)

Fターム[5F140BD01]に分類される特許

201 - 220 / 822

半導体装置及びその製造方法

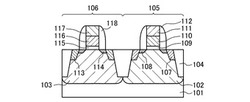

【課題】微細化されても、pチャネルトランジスタのチャネル領域には圧縮歪を、nチャネルトランジスタのチャネル領域には引っ張り歪をそれぞれ効果的に印加できる新しい歪技術を提供する。

【解決手段】pチャネルトランジスタ105のゲート電極は、引っ張り内部応力を持つpチャネルメタル電極110を有する。nチャネルトランジスタ106のゲート電極は、圧縮内部応力を持つnチャネルメタル電極116を有する。

(もっと読む)

半導体デバイスの製造方法及び基板処理装置

【課題】金属製のゲート電極(メタル電極)のダメージを熱酸化により修復する際の高誘電率ゲート絶縁膜の結晶化を抑制する。

【解決手段】エッチングにより側壁が露出した高誘電率ゲート絶縁膜とメタル電極とを有する基板を処理室内に搬入する工程と、処理室内で、基板を高誘電率ゲート絶縁膜が結晶化しない温度に加熱した状態で、基板に対してプラズマで励起した水素含有ガスと酸素含有ガスとを供給して酸化処理を施す工程と、処理後の基板を処理室内から搬出する工程と、を有し、酸化処理を施す工程では、水素含有ガスの活性化時期と酸素含有ガスの活性化時期とが互いに一致するよう、処理室内への水素含有ガスの供給を開始した後、所定時間経過してから処理室内への酸素含有ガスの供給を開始する。

(もっと読む)

MIS型半導体装置及びその製造方法

【課題】半導体集積回路のトランジスタのゲート絶縁膜を、安定な高誘電率絶縁膜で構成した、リーク電流が小さくしかも駆動力の大きい、MIS型半導体装置を提供する。また、閾値電圧のバラツキの小さい、量産可能で安価な高誘電率ゲート絶縁膜の製造方法を提供する。

【解決手段】アルミニウム酸化物層と、ジルコニウムまたはハフニウムのシリコン酸化物層とを積層した積層ゲート絶縁膜を用いたMIS型半導体装置。ジルコニウムまたはハフニウムのシリコン酸化物層を、導電チャネル側に設置する。

(もっと読む)

半導体装置およびその製造方法

【課題】NMISトランジスタとPMISトランジスタの閾値電圧を同時に低減できる半導体装置を提供する。

【解決手段】半導体装置の製造方法は、基板10に形成された第1の活性領域10a上に高誘電体を含む第1のゲート絶縁膜17aと、金属材料を含む第1のゲート電極18aとを形成し、基板10に形成された第2の活性領域10b上に高誘電体を含む第2のゲート絶縁膜17bと、金属材料を含む第2のゲート電極18bとを形成する工程と、第1のゲート絶縁膜17aの端部と第2のゲート絶縁膜17bの端部とに負の固定電荷を導入する工程と、第1のゲート絶縁膜17aの端部を除去する工程とを備えている。

(もっと読む)

半導体装置の製造方法

【課題】高い比誘電率が確保されており且つ熱的に安定なゲート絶縁膜を用いた半導体装置を実現できるようにする。

【解決手段】基板20上に、水素を含むHfO2 膜22Aを形成した後、HfO2 膜22Aに対して熱処理を行なうことにより、基板20側からシリコンをHfO2 膜22A中に拡散させてシリコン含有HfO2 膜22を形成する。その後、シリコン含有HfO2 膜22の上にゲート電極となるポリシリコン膜を形成する。

(もっと読む)

III−V族加工基板の製造方法およびそのIII−V族加工基板

【課題】パッシベーション層を備え、改善した性能を持つデバイスを実現できるIII−V族加工基板およびその製造方法を提供する。

【解決手段】III−V族加工基板の製造方法は、<110>または<111>の結晶方位を持つ第1のIII−V化合物からなる上側層(2)を備えたベース基板(I)を用意すること、第2のIII−V化合物からなるバッファ層(3)を少なくとも形成することを含んだ、中間層(II)を形成することであって、中間層(II)は、ベース基板の上側層(2)の上に位置し、これと接触するようにすること、IV族半導体材料からなる擬似格子整合パッシベーション層(4)を成長させることであって、擬似格子整合パッシベーション層は、中間層(II)の上に位置し、これと接触するようにすることを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】高誘電率ゲート絶縁膜およびメタルゲート電極を備えたCMISFETの性能を向上させる。

【解決手段】高誘電率ゲート絶縁膜として機能するHf含有絶縁膜4a,4b上にメタルゲート電極であるゲート電極GE1,GE2が形成され、ゲート電極GE1,GE2は、金属膜7a,7b,7cの積層膜からなる金属膜7とその上のシリコン膜8との積層構造を有している。金属膜7の最下層の金属膜7aは、窒化チタン膜、窒化タンタル膜、窒化タングステン膜、炭化チタン膜、炭化タンタル膜または窒化タングステン膜からなり、金属膜7bは、ハフニウム膜、ジルコニウム膜またはアルミニウム膜からなり、金属膜7cは、金属膜7aと同種の材料からなる膜である。

(もっと読む)

窒化物系半導体電界効果トランジスタ

【課題】ノーマリオフ動作を達成し、十分なチャネル電流が得られ、かつ、しきい値電圧制御が容易な窒化物系半導体ヘテロ接合電界効果トランジスタを提供する。

【解決手段】GaN層10とAlGaN層11のヘテロ接合界面をチャネルとする電界効果トランジスタにおいて、負の電荷を有する第三の層40をゲート電極34下のゲート絶縁膜31中に設けるとともに、ヘテロ接合を形成する窒化物半導体内にフッ素イオンF−等の負のイオン41を注入する。第三の層40はCl−等の負のイオンが注入される。ゲート絶縁膜31中およびAlGaN層11中に適量の負のイオンを注入することにより、しきい値電圧が上がりノーマリオフ動作を確実に達成するとともに、十分なチャネル電流が得られる。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電率膜のゲート絶縁膜を含むMISFETを有する半導体装置に関し、メタルゲート材料の仕事関数と半導体基板の仕事関数との間の関係によって閾値電圧を容易且つ浅い値に制御しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板上に酸化シリコンを主体とする第1の絶縁膜を形成し、第1の絶縁膜上に酸化ハフニウムを主体とする第2の絶縁膜を形成し、熱処理を行い第2の絶縁膜上にシリコンを析出させ、シリコン上にシリコンに対して酸化作用を有する第3の絶縁膜を形成し、第3の絶縁膜上に金属膜のゲート電極を形成し、熱処理を行い第3の絶縁膜の酸化作用によってシリコンを酸化させる。

(もっと読む)

半導体装置およびその製造方法

【課題】高誘電率材料を含むゲート絶縁膜と、高融点金属等を含むゲート電極とを備え、消費電力の低減と高速動作化とが図られた半導体装置及びその製造方法を提供する。

【解決手段】半導体装置の製造方法は、高誘電率膜を含む絶縁膜101aを形成する工程(a)と、上面に酸化膜が形成され、高融点金属または高融点金属の化合物の少なくとも一方を含む第1の導電膜102aを形成する工程(b)と、酸化膜103aを間に挟んで第1の導電膜102a上に、シリコンを含む第2の導電膜104aを形成する工程(c)と、第1の導電膜102aおよび第2の導電膜104aに対してイオン注入を行い、酸化膜103aの構成材料を前記第2の導電膜104a中のシリコンと混合させてミキシング層103bを形成する工程(d)と、熱処理を行ってミキシング層103bを導電層103cにする工程(e)とを備える。

(もっと読む)

シャロートレンチアイソレーションプロセス

【課題】トレンチ構造の歪み導入要素によりに歪み導入されたチャネルを持つMOSトランジスタのリーク電流を改善する。

【解決手段】MOSトランジスタ106のチャネル領域108に、第1トレンチ構造55a、第2トレンチ構造55bによる歪み導入要素だけでなく、別の歪み導入要素として、MOSトランジスタ106表面上にコンフォーマルに設けられた窒化シリコンキャップ層130を設ける。別の態様では、チャネル領域108内の歪みは、ガス種、例えば水素、酸素、ヘリウムまたは別の希ガスをゲート110またはチャネル領域108の下の領域内に注入することによって導入される。

(もっと読む)

半導体装置の製造方法

【課題】工程増を招くことなく、極めて高い歩留まりでゲート電極について均一で十分なフル・シリサイド化を確実に実現する。

【解決手段】ゲート電極104a,104b及びソース/ドレイン領域107a,107bのNiシリサイド化を行うに際して、1回目のNiシリサイド化の後に1回目のmsecアニール処理であるフラッシュランプアニール処理を行い、2回目のNiシリサイド化、更には必要であれば2回目のフラッシュランプアニール処理を行って、ソース/ドレイン領域107a,107b上には1回目のフラッシュランプアニール処理で形成されたNiSi層111bを維持した状態で、フル・シリサイドゲート電極115a,115bを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、最適な仕事関数を有するメタルゲート電極を持つ半導体装置及びその製造方法に関する。

【解決手段】n チャネルMIS トランジスタを含む半導体装置であり、n チャネルMIS トランジスタは、基板上に形成されたp 型半導体領域、p 型半導体領域に形成されたソース領域102及びドレイン領域104、ソース領域102及びドレイン領域104間のp 型半導体領域上に形成されたゲート絶縁膜106、ゲート絶縁膜106上に形成された金属層108及び化合物層110からなる積層構造を持つゲート電極を有する。金属層108は2 nm未満の厚さ及び4.3 eV以下の仕事関数を有し、化合物層110は4.4 eVを越える仕事関数を有しかつAl及び金属層108とは異なる金属を含んでいる。

(もっと読む)

高kゲート誘電体のための、不純物酸素を捕捉する半導体構造および該構造を形成する方法(高kゲート誘電体のための捕捉金属スタック)

【課題】CMOS集積過程での高温処理の後であっても一定の閾値電圧を維持する高kゲート誘電体の提供。

【解決手段】高kゲート誘電体30と、下部金属層40、捕捉金属層50、および上部金属層60を含む金属ゲート構造とのスタックを提供する。該捕捉金属層は、次の2つの基準、1)Si+2/yMxOy→2x/yM+SiO2の反応によるギブス自由エネルギの変化が正である金属(M)であること、2)酸化物形成に対する酸素原子あたりのギブス自由エネルギが、下部金属層の金属および上部金属層の金属より大きな負である金属であること、を満たす。これらの基準を満たす捕捉金属層は、酸素原子がゲート電極を通って高kゲート誘電体に向け拡散するときに該酸素原子を捕捉する。さらに、該捕捉金属層は、高kゲート誘電体の下の酸化ケイ素界面層の厚さを遠隔から低減する。この結果、ゲート誘電体全体の等価酸化膜厚(EOT)の変動が抑制される。

(もっと読む)

半導体装置およびその製造方法

【課題】高誘電率ゲート絶縁膜およびメタルゲート電極を備えたCMISFETの性能を向上させる。

【解決手段】nチャネル型MISFETQnは、半導体基板1のp型ウエルPWの表面上に、ゲート絶縁膜として機能するHf含有絶縁膜3aを介して形成されたゲート電極GE1を有し、pチャネル型MISFETQpは、n型ウエルNWの表面上に、ゲート絶縁膜として機能するHf含有絶縁膜3bを介して形成されたゲート電極GE2を有している。ゲート電極GE1,GE2は、金属膜7とその上のシリコン膜8との積層構造を有している。Hf含有絶縁膜3aは、Hfと希土類元素とSiとOとNとからなる絶縁材料膜またはHfと希土類元素とSiとOとからなる絶縁材料膜であり、Hf含有絶縁膜3bは、HfとAlとOとNとからなる絶縁材料膜またはHfとAlとOとからなる絶縁材料膜である。

(もっと読む)

半導体装置及びその製造方法

【課題】High-k/metalゲート電極構造において各極性のFETに要求される仕事関数値を実現する。

【解決手段】第1の領域と第2の領域とを有する半導体基板101の上にゲート絶縁膜103を形成する。次に、ゲート絶縁膜103の上に第1の金属窒化膜105を堆積する。次に、第1の金属窒化膜105における第2の領域に位置する部分を除去することにより、ゲート絶縁膜103における第2の領域に位置する部分を露出させる。次に、ゲート絶縁膜103における第2の領域に位置する部分の上に、第1の金属窒化膜105と同じ金属窒化物からなる第2の金属窒化膜107を形成する。

(もっと読む)

半導体ウエハを処理するための方法

【課題】

【解決手段】半導体ウエハを処理するための方法であって:酸化ランタンまたは酸化ランタニド(例えば、Dy2O3、Pr2O3、Ce2O3)を含む層を準備する工程と;炭酸水である水溶液を供給することにより、酸化ランタンまたは酸化ランタニドを含む層を特定の領域で除去して、酸化ランタンまたは酸化ランタニドを含む層が上に蒸着された表面を露出させる工程とを備える方法が開示されている。

(もっと読む)

半導体装置

【課題】インパクトイオン化現象によって発生した電子・正孔を効率よく吸収することが可能で正常な動作特性と高い信頼性を実現する半導体装置を提供する。

【解決手段】半導体装置20は、基板21に対して順次積層されたバッファ層22、下地化合物半導体層23f(下地化合物半導体層23)、インパクトイオン制御層24、下地化合物半導体層23s(下地化合物半導体層23)、チャネル画定化合物半導体層26f(チャネル画定化合物半導体層26)、チャネル画定化合物半導体層26s(チャネル画定化合物半導体層26)、AlGaN(窒化アルミニウムガリウム)層28、GaN(窒化ガリウム)層29を備えている。インパクトイオン制御層24は、下地化合物半導体層23の積層範囲(積層範囲の厚さTst)内に積層されてインパクトイオン化現象の発生位置を制御する。

(もっと読む)

半導体装置の製造方法

【課題】より高温の活性化FLAを行ってもウェハが割れることなく、SDエクステンション抵抗を下げることができる半導体装置の製造方法を提供する。

【解決手段】ウェハをウェハ表面温度1100℃以上に0.1〜10ミリ秒で加熱するための高強度のフラッシュランプアニールを照射する際、その直前のウェハ表面温度を800〜1000℃と高温にする。ウェハの予備加熱を、波形を調整したフラッシュで行うことにより不純物の拡散を抑制する。この手法により、アモルファス層を形成していないウェハ表面を効果的に活性化できるため、欠陥が少なく、かつ浅く低抵抗な接合が形成できる。

(もっと読む)

半導体装置およびその製造方法

【課題】メタルゲート電極の酸化を抑制しつつ、MOSFETの寄生容量の増大を抑制する。

【解決手段】半導体装置は、半導体基板10と、前記半導体基板上に形成されたシリコンと酸素とを含む第1絶縁膜12aと、前記第1絶縁膜上に形成された前記第1絶縁膜よりも誘電率が高く、高融点金属と酸素とを主成分とする第2絶縁膜12bと、で構成されるゲート絶縁膜12と、前記ゲート絶縁膜上に形成された金属層13を含むゲート電極15と、前記ゲート電極の前記金属層の側面、および前記ゲート絶縁膜の前記第2絶縁膜の側面に形成されたシリコンと窒素を含む第1側壁絶縁膜16と、前記第1側壁絶縁膜の側面、および前記第1絶縁膜の前記第1絶縁膜の側面に形成されたシリコンと酸素とを含む第2側壁絶縁膜17と、を具備する。

(もっと読む)

201 - 220 / 822

[ Back to top ]