Fターム[5F140BD07]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート絶縁膜 (8,730) | 材料 (6,782) | SiN (784)

Fターム[5F140BD07]に分類される特許

201 - 220 / 784

エンハンスメント型窒化ガリウム高電子移動度トランジスタ

実施形態には、これに限定されないが、第1バリア層と、該第1バリア層上の窒化ガリウムチャネル層と、該窒化ガリウムチャネル層上に存在し、第1サブレイヤーと第2サブレイヤーと第3サブレイヤーとを備える第2バリア層と、を有するヘテロ構造を備える装置とシステムが含まれる。該第1バリア層、第1サブレイヤーおよび第3サブレイヤーは各々アルミニウムを含んでいてもよい。他の実施形態も、本明細書に記載され特許請求される。 (もっと読む)

窒化物系半導体電界効果トランジスタ

【課題】ノーマリオフ動作を達成し、十分なチャネル電流が得られ、かつ、しきい値電圧制御が容易な窒化物系半導体ヘテロ接合電界効果トランジスタを提供する。

【解決手段】GaN層10とAlGaN層11のヘテロ接合界面をチャネルとする電界効果トランジスタにおいて、負の電荷を有する第三の層40をゲート電極34下のゲート絶縁膜31中に設けるとともに、ヘテロ接合を形成する窒化物半導体内にフッ素イオンF−等の負のイオン41を注入する。第三の層40はCl−等の負のイオンが注入される。ゲート絶縁膜31中およびAlGaN層11中に適量の負のイオンを注入することにより、しきい値電圧が上がりノーマリオフ動作を確実に達成するとともに、十分なチャネル電流が得られる。

(もっと読む)

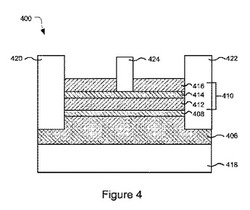

パンチスルーアクセスを有する縦型不揮発性スイッチおよびその製造方法

不揮発性メモリセルにアクセスするための半導体装置が提供される。いくつかの実施形態においては、半導体装置は、ソース、ドレインおよびウェルを含む半導体層の縦型スタックを有する。半導体装置へのドレイン−ソースバイアス電圧の印加は、ウェルにわたってパンチスルー機構を生成し、ソースとドレインとの間の電流の流れを発生させる。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】トランジスタ特性を向上させる。

【解決手段】STI109と、STI109によって互いに分離されたp型ウェル102及びn型ウェル103と、p型ウェル102及びn型ウェル103上に形成されたSiGe膜108とを有するSi基板101を用意する工程と、n型ウェル103上に位置するSiGe膜108をSiO2膜116で被覆する工程と、SiO2膜116をマスクとして酸化処理を行うことによりp型ウェル102上に形成されたSiGe膜108を酸化し、SixGeyOz膜117を形成する工程((c))と、SixGeyOz膜117を除去する工程((d))と、を行い、半導体装置を製造する。

(もっと読む)

半導体ウエハを処理するための方法

【課題】

【解決手段】半導体ウエハを処理するための方法であって:ハフニウムおよび/またはジルコニウムを含む第1の酸化物材料を含む高誘電体層と;前記高誘電体層の上部に蒸着され、ランタン、ランタニド、および/または、アルミニウムを含む第2の酸化物材料を含むキャップ層と、を備えたスタックを準備する工程と;酸化剤を含む水溶液である液体Aを前記半導体ウエハの表面に供給する工程SAと;工程SAの後に、6未満のpH値の液体である液体Bを前記半導体ウエハの前記表面に供給する工程SBと;工程SBの後に、少なくとも10ppmのフッ素濃度の酸性水溶液である液体Cを前記半導体ウエハの前記表面に供給する工程SCとを備える方法が開示されている。

(もっと読む)

超高品質シリコン含有化合物層の形成方法

【課題】ALDがCVDに比べて優れたコンフォーミティ(coformality)、成膜速度及び均一性を備えた気相堆積方法を提供する。

【解決手段】シリコンナイトライド層を含む、超高品質シリコン含有化合物層を形成するため、複数の順次的なステップ140が、反応チャンバー中で実施される。好ましい実施態様において、シリコン前駆物質としてトリシランを用いて、シリコン層が基板上に堆積100される。シリコン前駆物質は、反応チャンバーから除去される110。その後、シリコンナイトライド層が、シリコン層を窒化すること120によって形成される。窒素反応物質は、反応チャンバーから除去される110。これらのステップ100、110、120及び130を繰り返すことによって、所望の厚さのシリコンナイトライド層が形成される。

(もっと読む)

傾斜三元または四元マルチゲートトランジスタ

【課題】 フィン電界効果トランジスタ(FinFET)とその形成方法を提供する。

【解決手段】 半導体基板、前記半導体基板上の絶縁領域、及び前記半導体基板上に位置し、前記絶縁領域間の間隙に少なくとも一部を有し、第1III-V族化合物半導体材料を含むエピタキシー領域を含み、前記エピタキシー領域は、そこと前記半導体基板が第1格子不整合を有する下部分、及び前記下部分上に位置し、そこと前記半導体基板が前記第1格子不整合と異なる第2格子不整合を有する上部分を更に含む集積回路構造。

(もっと読む)

電界効果トランジスタ

【課題】高いしきい値電圧と大きい動作電流とを両立した電界効果トランジスタを提供すること。

【解決手段】基板と、前記基板上に形成され、窒化物系化合物半導体からなり、チャネル層を含む半導体層と、前記チャネル層上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成されたゲート電極と、前記半導体層上において前記ゲート電極を挟むように配置されたソース電極およびドレイン電極と、を備え、前記チャネル層の表面の、少なくとも前記ゲート電極直下の領域が、窒素極性の表面を含む。

(もっと読む)

窒化物半導体装置および窒化物半導体装置製造方法

【課題】窒素不足に起因する移動度の低下を抑制し、窒素不足に起因するリーク電流を低減することができる窒化物半導体装置、その製造方法を提供する。

【解決手段】窒化物半導体装置1は、基板10と、バッファ層11と、窒化物半導体層(第1窒化物半導体層12、第2窒化物半導体層13、第3窒化物半導体層14)と、第1電極22と、第2電極23と、制御電極25とを備える。第1電極22と第2電極23との間で第3窒化物半導体層14の表面から第2窒化物半導体層13に渡って凹状に形成されたリセス部16を備え、リセス部16は、絶縁性窒化物で形成された窒化物絶縁膜17を備え、制御電極25は、導電性窒化物で形成され窒化物絶縁膜17(ゲート絶縁膜)に重ねて配置されている。

(もっと読む)

横型HEMTおよび横型HEMTの製造方法

【課題】高いアバランシュブレークダイン強度を有する横型HEMTと、その製造方法を提供する。

【解決手段】基板10と、基板上に配置された、第1導電型のチヤネルとなる第1層11、少なくとも部分的に上記第1層11の上に配置された電子供給層となる第2層12を有する。さらに、上記横型HEMTは、上記第1導電型に対して相補的な第2導電型の半導体物質を有し、少なくとも部分的に上記第1層11の中に配置された第3層13を有する。このためPNダイオードが上記第1層および第3層の間で形成され、PNダイオードは横型HEMTより低いブレークダウン電圧を有することにより、HEMTを高い電界から保護することができ、HEMTの劣化を防止できる。

(もっと読む)

集積回路構造

【課題】III−V族化合物半導体を含むトランジスタとその形成方法を提供する。

【解決手段】基板20、前記基板上にあり、III族とV族元素を含む第1のIII−V族化合物半導体材料で形成されたチャネル層26、前記チャネル層の上方の高ドープ半導体層30、前記高ドープ半導体層を穿通して形成され前記高ドープ半導体層の側壁に接触したゲート誘電体50、及び前記ゲート誘電体の下部部分上のゲート電極52を含み、ゲート誘電体50が前記ゲート電極の側壁上の側壁部分を有している集積回路構造。

(もっと読む)

改善されたオン/オフ電流比の高移動度多重ゲートトランジスタ

【課題】 金属酸化物半導体(MOS)トランジスタとその形成方法を提供する。

【解決手段】 多重ゲートトランジスタは、基板、第1半導体材料で形成された中央フィン、及び中央フィンの対向側壁上の第1部分と第2部分を含み、第1半導体材料とは異なる第2半導体材料を包含する半導体層を含む基板上の半導体フィン、この半導体フィンの側壁の周囲を包むゲート電極、及び半導体フィンの対向端のソース領域とドレイン領域を含み、中央フィンと半導体層の各々は、ソース領域からドレイン領域に延伸する。

(もっと読む)

半導体装置およびその製造方法

【課題】GIDL等の局所的な電界集中により発生するリークおよび短チャネル効果の発生を抑えた半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、半導体基板2上にゲート絶縁膜11を介して形成されたゲート電極12と、半導体基板2中のゲート電極12の両側に形成され、ゲート電極12側のエクステンション領域151とゲート電極12の反対側の深い領域152とを有し、導電型不純物を含むソース・ドレイン領域15と、を有し、ソース・ドレイン領域15のエクステンション領域151は、ゲート電極12側の高拡散領域151aと、最下部の半導体基板2の表面からの深さが高拡散領域151aの最下部の半導体基板2の表面からの深さよりも浅く、高拡散領域151aと深い領域152との間に設けられた低拡散領域151bと、を含む。

(もっと読む)

絶縁膜の形成方法、半導体装置の製造方法および半導体装置の製造装置

【課題】半導体を高濃度の硝酸の蒸気および/または溶液に接触させる処理で、短時間に、前記半導体表面に高品質の二酸化シリコン膜の生成を実現する。

【解決手段】被処理用シリコンを濃度70wt%の硝酸の加熱溶液から発生させた蒸気中で数秒、および/またはその加熱硝酸溶液で10分程度接触させて、前記シリコンの表面に膜厚約1.39nmの酸化膜を形成した。この被膜は、リーク電流性能が(1V印加時)0.6A/cm2であり、同膜厚換算のオキシナイトライド膜の以下のレベルを実現できた。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】量産性に優れた実用的なプロセスを用いて、炭化珪素基板と二酸化珪素膜との間の界面準位を大幅に低減することができ、デバイスとしての信頼性と電気特性が優れた炭化珪素半導体装置を提供する。

【解決手段】二酸化珪素膜51の形成後、CVD法により、二酸化珪素膜51上に酸窒化珪素膜61を形成する。その後、酸窒化珪素膜61が堆積された炭化珪素基体10を窒化処理反応炉に導入し、窒素酸化物ガス雰囲気中で窒化処理を行う。

(もっと読む)

半導体装置およびその製造方法

【課題】耐熱性に優れたシリサイド層をソース・ドレイン領域に有するp型MOSFETを備える半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、半導体基板2上にゲート絶縁膜11を介して形成されたゲート電極12と、半導体基板2上のゲート電極12の両側に形成されたエレベーテッド層15と、エレベーテッド層15上に形成されたSi:C16層と、半導体基板2、エレベーテッド層15、およびSi:C16内のゲート電極12の両側に形成されたp型のソース・ドレイン領域19と、Si:C層16上に形成されたシリサイド層17と、を有する。

(もっと読む)

MOSトランジスタ

【課題】MOSトランジスタを作成する。

【解決手段】MOSトランジスタであって、ゲート電極と、ゲート電極下地の頂部表面を有するチャンネル領域と、ゲート電極とチャンネル領域の頂部表面の間に挿入された誘電体スタックとを含み、前記誘電体スタックが、少なくとも高―k材料を含む高―k誘電体層と、少なくともケイ素および窒素を含む誘電体層と、前記高―k誘電体層と前記誘電体層の間に配設された中間層とを含み、該中間層が、少なくとも前記高―k材料、ケイ素および窒素を含み、前記ゲート電極がポリシリコンまたはポリシリコンゲルマニウムから作製される。

(もっと読む)

電界効果トランジスタ

【課題】耐電圧を高めて、大電流を安定して継続的に流すことができる電界効果トランジスタを提供する。

【解決手段】電界効果トランジスタ10は、III族窒化物半導体から成る半導体活性層11の表面領域に形成されたソース16s及びドレイン16dと、半導体活性層11上にゲート酸化膜12を介して形成されたゲート電極13とを備える。電界効果トランジスタ10は、ゲート電極13とドレイン16dとの間の半導体活性層11内に形成された電界緩和層20を有する。電界緩和層20は、正の電荷が生じる第1の層21と負の電荷が生じる第2の層22とが、膜厚方向に交互に配置される積層構造を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】GaN/AlGaN−HEMTをE−mode動作させるに当たり、Vf及び最大ドレイン電流を向上させ、かつ良好なゲート−ドレイン間耐圧を有し、さらに、ゲートリーク電流を抑制する。

【解決手段】基板15と、この基板上に形成されており、GaN層17及びAlGaN層19が順次積層されてなる積層構造体21とを含む下地13と、AlGaN層に開口形成されているゲート形成用凹部27と、このゲート形成用凹部の内側底面27a、ゲート形成用凹部の内側壁面27b、及びゲート形成用凹部外の下地面13aを一体的に被覆して形成されているSiN膜29と、SiN膜の表面を被覆して形成されているアモルファスAlN膜31と、SiN膜及びアモルファスAlN膜が形成されているゲート形成用凹部を埋め込むゲート電極33とを具える。

(もっと読む)

補償型ゲートMISFET及びその製造方法

低いゲートリークを有する例えばGaNトランジスタなどのMISFETが提供される。一実施形態において、ゲートコンタクトの下且つバリア層の上に、補償型のGaN層を有することで、ゲートリークが低減される。他の一実施形態において、ゲートコンタクトの下且つバリア層の上に半絶縁性の層を用いることによって、ゲートリークが低減される。  (もっと読む)

(もっと読む)

201 - 220 / 784

[ Back to top ]