Fターム[5F140BD07]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート絶縁膜 (8,730) | 材料 (6,782) | SiN (784)

Fターム[5F140BD07]に分類される特許

141 - 160 / 784

半導体装置およびその製造方法

【課題】界面準位を低減しつつ、電荷トラップに起因するヒステリシスを抑制できる半導体装置の構造およびその製造方法を提供する。

【解決手段】半導体装置200は、GaNを含む半導体層101を表面の少なくとも一部に有する基板(半導体基板100)と、半導体層101と接するように半導体基板100上に設けられており、窒素を含まず、Alを含む酸化金属層からなる第1のゲート絶縁層(Al2O3膜114)と、Al2O3膜114上に設けられており、SiおよびOを含む第2のゲート絶縁層(SiO2膜116)と、SiO2膜116上に設けられたゲート電極118と、を備え、ゲート電極118の下面は、SiO2膜116に接しており、Al2O3膜114の膜厚は、SiO2膜116の膜厚より薄い。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】初期故障や偶発故障の発生を低減する。

【解決手段】HFET1は、下層のGaN層13およびGaN層13の一部を露出させるトレンチT1が形成された上層のAlGaN層14よりなるIII族窒化物半導体層と、III族窒化物半導体層上に形成されたゲート絶縁膜15と、ゲート絶縁膜15上に形成されたゲート電極16と、を備える。少なくともゲート絶縁膜15と接触するトレンチT1底部のGaN層13上面には、原子層ステップが形成されている。原子層ステップのテラス幅の平均値は、0.2μm以上1μm未満である。

(もっと読む)

III族窒化物半導体本体のインシチュドーパント注入及び成長

【課題】半導体材料の構造的及び化学量論的特性を保ったまま、窒化物本体を横方向及び縦方向で空間的に規定された選択ドーピングを達成しうるインシチュドーパント注入及び成長を提供する。

【解決手段】窒化物半導体本体の成長中にインシチュドーパント注入を可能にする方法は、ドーパント注入装置及び成長室を有する複合窒化物室中に、窒化物半導体本体に対する成長環境を確立するステップと、成長室内で窒化物半導体本体を成長させる成長ステップと、ドーパント注入装置を用いて成長室内で窒化物半導体本体にインシチュ状態でドーパント注入を行う注入ステップとを具える。この方法を用いて形成する半導体デバイスは、サポート基板上に形成した第1導電型の窒化物半導体本体と、窒化物半導体本体の成長中にこの窒化物半導体本体のインシチュドーパント注入により形成され、第2導電型を有する少なくとも1つのドープ領域とを具える。

(もっと読む)

窒化物半導体装置

【課題】GaN系の窒化物半導体を用いたデバイスのゲートリセス量の制御性を向上することで、閾値電圧の面内均一性を向上することができる窒化物半導体装置を実現できるようにする。

【解決手段】窒化物半導体装置は、基板101上に形成された第1のGaN系半導体からなるバッファ層102と、第2のGaN系半導体からなるキャリア走行層103と、第3のGaN系半導体からなるキャリア供給層104とを備えている。キャリア供給層104の上には第1の絶縁膜105と、アルミニウムを含む第2の絶縁膜106と、第1の絶縁膜105より膜厚が厚い第3の絶縁膜107とが形成されている。ソース電極108及びドレイン電極109は第1の絶縁膜105上に形成されている。ゲート電極110は、リセス構造を含む第2の絶縁膜106及び第3の絶縁膜107上に形成されている。

(もっと読む)

高導電性のソース/ドレイン接点を有するIII族窒化物トランジスタ及びその製造方法

【課題】III族窒化物トランジスタのドレイン及びソース接点と、下位のドレイン及びソース領域の各々との間の抵抗を低減させる。

【解決手段】ゲート、ソース、及びドレイン領域上に延在するフィールド誘電体240にトレンチをエッチングする工程と、ゲート、ソース、及びドレイン領域上にゲート誘電体270を形成する工程と、ゲート誘電体上270にブランケット拡散バリア272を形成する工程と、ソース及びドレイン領域からブランケット拡散バリア272を除去する工程と、ゲート誘電体270をソース及びドレイン領域から除去し、ソース及びドレイン領域をほぼ露出させる工程とを含む。次いで、ソース及びドレイン領域に接点金属290を堆積することにより、オーミック接点を形成する。

(もっと読む)

ダイヤモンド半導体素子及びその製造方法

【課題】耐電圧、耐熱性、耐放射線性、及び高速性が優れ、かつ、チャネル領域を短くでき、素子の応答性が高いダイヤモンド半導体素子を高精度で製造できる半導体素子の製造方法を提供する。

【解決手段】第1のダイヤモンド半導体領域1の表面上に、絶縁膜2と多層金属電極層3と犠牲層4とを積層し、犠牲層4上に、局所的にレジスト5をパターン形成する。多層金属電極層3の最上層は、Pt又はPt合金により形成する。そして、レジスト5をマスクとして第1の犠牲層、多層金属電極層及び絶縁膜をエッチングした後、レジスト5を除去して、第1のダイヤモンド半導体領域1上に絶縁膜2と金属電極層3と第1の犠牲層4との積層体をパターン形成する。その後、第1のダイヤモンド半導体領域1上に、不純物の高濃度ドープ層7を形成する。その後、犠牲層4をエッチング除去し、高濃度ドープ層7上に金属電極8を形成する。

(もっと読む)

窒化物半導体装置

【課題】エンハンメント型GaN系HFETの閾値電圧のバラツキを低減する。

【解決手段】窒化物半導体装置80では、第2のリセスエッチングによりアンドープGaN層3の上部に突起部51が設けられる。突起部51上には、上部が第1のリセスエッチングにより形成されたアンドープAlGaN層4aが設けられる。積層部7は、アンドープGaN層3の突起部51、アンドープAlGaN層4a、及び絶縁膜5から構成される。トレンチ部8は、絶縁膜5、アンドープAlGaN層4a、及びアンドープGaN層3表面がリセスエッチングされたものである。積層部7及びトレンチ部8上にはゲート絶縁膜6が設けられる。ゲート絶縁膜6上には、トレンチ部8を覆うようにゲート電極33が設けられる。絶縁膜5はゲート絶縁膜6よりも膜厚が厚く設定されている。

(もっと読む)

半導体装置

【課題】メタルゲート電極内に基板面に対して平行な金属とシリコンなどとの境界又はシリサイドとシリコンなどとの境界を含むメタルゲート電極において、トランジスタの接続抵抗が小さく、高速動作時のトランジスタの遅延又はトランジスタ特性のばらつきなどの特性劣化の懸念がなく、且つ、低コストな構造を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板101上に、ゲート絶縁膜105と、pMIS用金属材料109又はnMIS用金属材料111と、ゲート電極材料112と、ゲート側壁メタル層122とを備えている。

(もっと読む)

III族窒化物系へテロ電界効果トランジスタ

【課題】オン動作時には電子移動の抵抗が低く、かつオフ動作時にはゲート電極と2次元電子ガスとのゲートリーク電流が発生しにくいIII族窒化物系へテロ電界効果トランジスタを提供する。

【解決手段】本発明のIII族窒化物系へテロ電界効果トランジスタは、基板と、該基板の上に設けられるキャリア走行層と、該キャリア走行層上に、ヘテロ界面を形成するように設けられる障壁層と、該障壁層上の一部からキャリア走行層の内部まで掘り込まれたリセス構造と、該リセス構造上に設けられる絶縁層と、該絶縁層上に設けられるゲート電極とを含み、キャリア走行層および障壁層はいずれも、III族窒化物半導体からなり、絶縁層は、リセス構造の側面上に形成される側面絶縁層と、リセス構造の底面上に形成される底面絶縁層とからなり、側面絶縁層の厚みは、前記底面絶縁層の厚みよりも厚いことを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】マイクロローディング効果を防止しながら、上層配線となる金属配線のレイアウト制約のない構造を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板1上に形成されたゲート絶縁膜3と、ゲート絶縁膜3の上に形成されたゲート電極4と、半導体基板1に形成された拡散層5と、半導体基板1の上に形成された絶縁膜7及び絶縁膜8と、絶縁膜及び絶縁膜8を貫通するホール9Dに埋め込まれ、側面を絶縁膜11で覆われた金属材料からなるプラグ12と、絶縁膜8を貫通しないホール10Bに埋め込まれ、絶縁膜11からなる絶縁体10Cと、絶縁膜8の上に形成され、プラグ12と電気的に接続する金属配線13Bとを備えている。

(もっと読む)

窒化物半導体を用いた半導体装置およびその製造方法

【課題】ソース領域およびドレイン領域とゲート電極との位置制御性を向上させ、製造バラツキを低減する。

【解決手段】窒化物半導体を用いた半導体装置10は、窒化物半導体層2に所定間隔を隔てて形成されたソース領域3およびドレイン領域4の間のチャネル領域上に形成され、少なくとも一部がシリサイド合金から形成されたゲート電極6を備え、ソース領域3上にあるゲート電極6の端からゲート電極6と上下に重なるソース領域3の端までの距離L1と、ドレイン領域4上にあるゲート電極6の端からゲート電極6と上下に重なるドレイン領域4の端までの距離L2と、が等しい。

(もっと読む)

半導体素子の製造方法

【課題】ピッティング不良が抑制され、簡単な工程を通じて形成することができる高性能の半導体素子の製造方法を提供する。

【解決手段】半導体基板にゲート電極を形成する段階と、ゲート電極に側壁スペーサを形成する段階と、側壁スペーサの両側の半導体基板を一部エッチングしてトレンチを形成する段階と、トレンチ内にSiGe混晶層を形成する段階と、SiGe混晶層上にシリコン層を形成する段階と、シリコン層の面の結晶方向に従って、エッチング率が異なるエッチング液を利用してシリコン層の一部をエッチチングすることによって111傾斜面を有するシリコンファセット(Si facet)を含むキャッピング層を形成する段階と、を有する。キャッピング層を含むことによって半導体素子でホールの移動度が高まる。キャッピング層内のピッティング不良が減少することによって半導体素子の特性が良好になる。

(もっと読む)

半導体装置およびその製造方法

【課題】ソース・ドレイン領域の寄生抵抗の上昇を抑えつつ短チャネル効果の発生を抑えた半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、半導体基板2上にゲート絶縁膜11を介して形成されたゲート電極12と、半導体基板2中のゲート電極12の両側に形成され、ゲート電極12側にエクステンション領域161を有し、導電型不純物を含むソース・ドレイン領域16と、ソース・ドレイン領域16のエクステンション領域161のゲート電極12側の側面のみに接し、導電型不純物の半導体基板2中での拡散を抑制する性質を有する拡散抑制不純物を含む拡散抑制層15と、を有する。

(もっと読む)

半導体装置およびその作製法

【課題】チャネル層半導体として用いるInN系半導体において、高濃度の残留背景電子が存在していても、ピンチオフ特性が得られ、InN系半導体の優れた電子輸送特性(高い電子移動度および高い飽和電子速度)が活用可能となる、窒化物半導体を用いた導体装置およびその作製法を提供すること。

【解決手段】ソース電極1にオーミック接触する障壁層半導体とオーミック領域チャネル層半導体とから形成されるソース側へテロ接合構造、および、ドレイン電極3にオーミック接触する障壁層半導体とオーミック領域チャネル層半導体とから形成されるドレイン側へテロ接合構造が形成され、それぞれのへテロ接合構造が、InN系チャネル層半導体(#)と接し、それぞれのへテロ接合構造において、ヘテロ接合界面近傍のみに伝導電子が局在し、ヘテロ接合界面の垂直方向位置が、InN系チャネル層半導体(#)の層内位置に存在することを特徴とする半導体装置を構成する。

(もっと読む)

半導体ウェーハ、及びその製造方法

【課題】シリコン基板にダメージを与えずに、ゲート下の不純物分布の正確な評価を安定して行うことのできる半導体ウェーハとその製造方法を提供する。

【解決手段】 半導体ウェーハは、半導体基板上の所定の箇所に設定されたモニター領域に、他と電気的接続を有しない断面形状がW字型のダミー充填部を有する。

(もっと読む)

電界効果トランジスタ、電子装置、電界効果トランジスタの製造方法及び使用方法

【課題】 チップ面積を大きくし過ぎることなく、過電圧、過電力が加わっても破壊されない電界効果トランジスタを提供する。

【解決手段】 本発明の電界効果トランジスタは、

半導体層上に、ゲート電極110と、ドレイン電極109と、ソース電極108と、保護ダイオード(保護ダイオード電極)111とが配置され、

ドレイン電極109が、保護ダイオード111の周囲の一部もしくは全部を囲む状態で形成されているか、または、

ドレイン電極109は、複数であり、複数のドレイン電極109の少なくとも一対のドレイン電極間に、保護ダイオード111が配置されるように形成されていることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート長が短い微細構造を有しながら、低消費電力でかつ高速動作が可能なMISFETを有する半導体装置を提供する。

【解決手段】シリコン基板と、このシリコン基板上にシリコン含有絶縁膜を介して設けられた高誘電率金属酸化膜を有するゲート絶縁膜と、このゲート絶縁膜上に形成されたシリコン含有ゲート電極とを有し、少なくとも前記高誘電率金属酸化膜の側面側に窒素含有部を有するMIS型電界効果トランジスタを備えた半導体装置。

(もっと読む)

半導体装置

【課題】 占有面積の増加もなく、十分なESD保護機能を持たせたESD保護用のN型のMOSトランジスタを有する半導体装置を得ることを目的とする。

【解決手段】 絶縁膜が埋め込まれたトレンチ素子分離領域と、凹部に周囲をゲート絶縁膜で覆われたゲート電極が埋め込まれたトレンチチャネル領域と、絶縁膜が埋め込まれた凹部の周囲を濃いN型の拡散層で覆ったトレンチドレイン領域とが形成されており、ESD保護用のN型MOSトランジスタのチャネル領域には、トレンチチャネル領域が形成され、なおかつESD保護用のN型MOSトランジスタのドレイン領域には、トレンチドレイン領域が形成されている。

(もっと読む)

集積回路デバイスに歪みを与える技術及び構成

本開示の実施形態により、例えば横型電界効果トランジスタなどの集積回路デバイスに歪みを与える技術及び構成が提供される。集積回路デバイスは、半導体基板と、該半導体基板と結合された第1のバリア層と、第1のバリア層に結合された、第1の格子定数を持つ第1の材料を有する量子井戸チャネルと、量子井戸チャネルに結合されたソース構造とを含む。ソース構造は、第1の格子定数とは異なる第2の格子定数を持つ第2の材料を有し、量子井戸チャネルに歪みを与える。その他の実施形態も開示される。  (もっと読む)

(もっと読む)

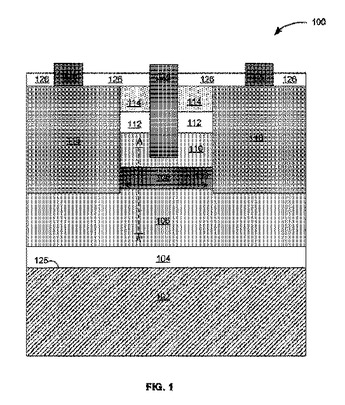

FinFETとトライゲートデバイス用のラップアラウンド型コンタクト

サブストレートとサブストレートの上に形成された半導体ボディを有する半導体デバイスである。半導体ボディはソース領域とドレイン領域を有している。ソース領域、ドレイン領域、またはその組み合わせは、第一の側面、第二の側面、及び上面を有している。第一の側面は第二の側面と向かい合っており、上面は底面と向かい合っている。ソース領域、ドレイン領域、またはその組み合わせは、実質的に全ての第一の側面の上に、実質的に全ての第二の側面の上に、そして上面の上に、形成されたメタル層を有している。  (もっと読む)

(もっと読む)

141 - 160 / 784

[ Back to top ]