Fターム[5F140BD07]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート絶縁膜 (8,730) | 材料 (6,782) | SiN (784)

Fターム[5F140BD07]に分類される特許

21 - 40 / 784

グラフェンを含む電極構造体及び電界効果トランジスタ

【課題】グラフェンを含む電極構造体及び電界効果トランジスタを提供する。

【解決手段】半導体層上のグラフェンと、グラフェン上の電極メタルと、を備え、該グラフェンは、半導体層と直接的に接触し、電極メタルは、グラフェンと直接的に接触する電極構造体である。半導体層は、シリコン、ゲルマニウム、シリコン・ゲルマニウム、III−V族半導体、及びII−VI族半導体を含むグループから選択された一つで形成される。グラフェンは、単層または二層のグラフェンで形成される。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】窒化物半導体を用いた電界効果トランジスタのしきい値電圧がより容易に制御できるようにする。

【解決手段】基板101の上に形成されたGaNからなる緩衝層102と、緩衝層102の上に形成されたAlGaNからなる障壁層103と、障壁層103の上に形成されたゲート電極104とを備える。また、障壁層103の上にゲート電極104を挟んでゲート電極104とは離間して形成されたソース電極105およびドレイン電極106を備える。加えて、障壁層103とゲート電極104との間に形成されたInAlNからなるキャップ層107を備える。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】特性の低下を抑制しながらノーマリオフ動作を実現することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1上方に形成された電子走行層3及び電子供給層5と、電子供給層5上方に形成されたゲート電極11g、ソース電極11s及びドレイン電極11dと、電子供給層5とゲート電極11gとの間に形成されたp型半導体層8と、が含まれている。p型半導体層8に含まれるp型不純物として、少なくとも電子走行層3及び電子供給層5のいずれかを構成する元素と同種の元素が用いられている。

(もっと読む)

窒化物半導体装置

【課題】内蔵する環流ダイオードの順方向電圧が低く、高耐圧で、低オン抵抗の、ノーマリオフ型の窒化物半導体装置を提供する。

【解決手段】窒化物半導体装置は、基板1、第1の窒化物半導体層3、第2の窒化物半導体層4、及び第2の窒化物半導体層上4に設けられた、ソース電極5、ドレイン電極6、第1のゲート電極9、ショットキー電極10、第2のゲート電極12、を備える。第2の窒化物半導体層4と第1の窒化物半導体層3との界面には、2次元電子ガスが形成される。第1のゲート電極9はノーマリオフ型FET20のゲート電極であり、ソース電極5とドレイン電極6との間に設けられる。ショットキー電極10は、第1のゲート電極9とドレイン電極6との間に設けられる。第2のゲート電極12はノーマリオン型FET21のゲート電極であり、ショットキー電極10とドレイン電極6との間に設けられる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】窒化物半導体層をチャネルとして用いたトランジスタにおいて、オン抵抗を低くしつつ、閾値電圧を高くする。

【解決手段】キャップ層400と障壁層300の界面、及びチャネル層200とバッファ層100の界面には圧縮歪が生じており、障壁層300とチャネル層200の界面には引張り歪が生じている。このため、キャップ層400と障壁層300の界面、並びにチャネル層200とバッファ層100の界面において、負の電荷が正の電荷よりも多くなっており、障壁層300とチャネル層200の界面において、正の電荷が負の電荷よりも多くなっている。チャネル層200は、第1層、第2層、及び第3層の積層構造を有している。第2層は、第1層及び第3層よりも電子親和力が大きい。

(もっと読む)

半導体装置及びその製造方法、電源装置、高周波増幅器

【課題】放置時間が長くても、化合物半導体積層構造の表面のダングリングボンドがフッ素で終端された状態が維持されるようにし、閾値電圧の変動を抑制して、信頼性を向上させる。

【解決手段】半導体装置は、化合物半導体積層構造6と、化合物半導体積層構造6の表面を覆うフッ素含有バリア膜9と、化合物半導体積層構造6の上方にフッ素含有バリア膜9を挟んで設けられたゲート電極8とを備える。

(もっと読む)

半導体装置の製造方法

【課題】一定のドレイン電圧及びゲート電圧に対して得られるドレイン電流を増大することの出来る半導体装置の製造方法を提供する。

【解決手段】チャンネル領域と、ソース領域及びドレイン領域と、前記ソース領域及びドレイン領域にそれぞれ電気的に接続する合計二つの第1の電極と、前記チャンネル領域上にゲート絶縁膜を介して設けられた第2の電極とを備えた半導体装置の製造に際し、前記ゲート絶縁膜を、酸素の含有量を1ppb以下にした水素添加超純水にIPAを添加した洗浄液を用いて、酸素含有量1ppb以下の窒素雰囲気でしかも遮光した状態で表面の洗浄を行ない、かつ等方性酸化または窒化で形成することにより、前記チャンネル領域と前記ゲート絶縁膜との界面の平坦度を、前記ソース領域から前記ドレイン領域に向かう方向での長さ2nmにおけるピーク・トゥ・バレイ値が0.3nm以下となるようにするとともに、前記第1の電極から前記チャンネル領域までの抵抗率を4Ω・μm以下とした。

(もっと読む)

半導体装置の製造方法

【課題】ヒ素(As)を高濃度にドーピングした状態でエクステンション領域のエピタキシャル成長膜表面に凹凸を発生させることなく、平滑な面に形成することを可能とする。

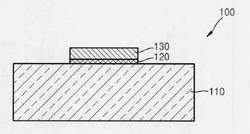

【解決手段】半導体基板11上にゲート絶縁膜12を介してゲート電極13を備え、前記ゲート電極13の両側の前記半導体基板11上に形成された不純物を含有してなるエクステンション領域17、18を備えた半導体装置1であって、前記エクステンション領域17、18は、シリコンゲルマニウムにヒ素を含む状態でエピタキシャル成長されたエピタキシャル成長膜からなり、このエピタキシャル成長膜は、ヒ素をドーピングしながらシリコンとゲルマニウムとを前記半導体基板11上に選択的にエピタキシャル成長させて形成される。

(もっと読む)

絶縁ゲート型半導体素子及び絶縁ゲート型半導体集積回路

【課題】RTSノイズを低減することが可能な絶縁ゲート型半導体素子、絶縁ゲート型半導体集積回路を提供する。

【解決手段】チャネル領域として機能する第1導電型の半導体層11、チャネル領域を囲み、半導体層11に活性領域を定義する素子分離絶縁膜21、活性領域の一方に設けられた第2導電型の第1主電極領域62、活性領域の他方に設けられた第2導電型の第2主電極領域63、活性領域の表面のゲート絶縁膜22、多結晶シリコン層を含んで、ゲート絶縁膜22の上に設けられたゲート電極54を備える。多結晶シリコン層は、第1主電極領域62,第2主電極領域63に接する部分は第2導電型の第1多結晶シリコン領域54-2、チャネル領域と素子分離絶縁膜21との境界領域の上部は第1導電型の第2多結晶シリコン領域54-1である。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置について、小型化を図りつつ、ドレイン耐圧を向上する。

【解決手段】ゲート電極20と、ゲート電極20と離間するソース電極24と、平面視でゲート電極20からみてソース電極24の反対側に位置し、かつゲート電極20と離間するドレイン電極22と、平面視でゲート電極20とドレイン電極22の間に位置し、絶縁膜26を介して半導体基板10上に設けられ、かつゲート電極20、ソース電極24およびドレイン電極22と離間する少なくとも一つのフィールドプレート電極30と、絶縁膜26中に設けられ、かつフィールドプレート電極30と半導体基板10を接続する少なくとも一つのフィールドプレートコンタクト40と、を備え、平面視でフィールドプレート電極30は、フィールドプレートコンタクト40からソース電極24側またはドレイン電極22側の少なくとも一方に延伸している。

(もっと読む)

半導体装置

【課題】低オン抵抗であって、かつ、ノーマリーオフの電界効果型トランジスタを提供する。

【解決手段】基板10の上に形成された電子走行層11と、電子走行層11の上に、電子走行層11よりもバンドギャップの広い半導体により形成された電子供給層12と、電子供給層12の上に、電子供給層よりもバンドギャップの狭い半導体により形成されたバリア形成層13と、バリア形成層13の上に、不純物のドープされた半導体により形成された上部チャネル層14と、バリア形成層13及び上部チャネル層14を除去することにより形成されたバリア形成層13及び上部チャネル層14の側面と、側面に形成された絶縁膜20と、絶縁膜20を介し形成されたゲート電極21と、上部チャネル層14と接続されるソース電極22と、電子供給層12または電子走行層11と接続されるドレイン電極23と、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極に臨む領域の半導体層へのダメージ層の形成を抑制して、ノーマリオフ動作を実現することができるヘテロ接合電界効果型トランジスタを備える半導体装置およびその製造方法を提供する。

【解決手段】チャネル層23とヘテロ接合を形成するバリア層24のうち、ゲート電極29に臨む領域を除く他の領域に、バリア層24の伝導帯から、チャネル層23とバリア層24とのヘテロ界面のバンド不連続量ΔEcと、バリア層24に発生する分極によるバリア層24のゲート電極29側とヘテロ界面側とのエネルギー差ΔEpとを足し合わせたエネルギー(ΔEc+ΔEp)までのエネルギー深さのバンドギャップ中に準位を形成する不純物をドーピングして、不純物ドーピング領域26を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】多結晶シリコン膜との接触に起因するショットキー抵抗を低減する。

【解決手段】半導体装置は、トランジスタを備える。トランジスタは、第1の活性領域の表面の一部を覆い二酸化シリコンよりも高い誘電率を有する第1の絶縁材料からなる第1のゲート絶縁膜と、第1のゲート絶縁膜上に形成された第1の金属材料からなる第1の金属ゲート電極と、第1の金属ゲート電極上に形成されたp型導電型の第1の多結晶シリコン膜を有する。

(もっと読む)

高電子移動度トランジスタとその製造方法

【課題】高電子移動度トランジスタにおいて、ゲート部のドレイン側端部における電界集中を緩和する。

【解決手段】高電子移動度トランジスタ10は、導電体部23と第1抵抗部R1と第2抵抗部R2を備えている。導電体部23は、ドレイン電極21とゲート部26の間に設けられている。第1抵抗部R1は、一端がドレイン電極21に電気的に接続されており、他端が導電体部23に電気的に接続されている。第2抵抗部R2は、一端がソース電極28に電気的に接続されており、他端が導電体部23に電気的に接続されている。

(もっと読む)

窒化物系半導体装置

【課題】ゲート絶縁膜の破壊を防止すると共に、信頼性を向上させた、ノーマリオフの双方向動作が可能な窒化物系半導体装置を提供する。

【解決手段】窒化物系半導体素子10は、第1MOSFET部30及び第2MOSFET部31を備えており、第1ゲート電極26と第2ゲート電極27との間に設けられた第1SBD金属電極28及び第2SBD金属電極29がAlGaN層20とショットキー接合されている。第1SBD金属電極28と第1電極24とが接続されており、電気的に短絡していると共に、第2SBD金属電極29と第2電極25とが接続されており、電気的に短絡している。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】窒化物半導体層をチャネルとして用いたトランジスタにおいて、閾値電圧を高くする。

【解決手段】第2窒化物半導体層200は、Alの組成比が互いに異なる複数の窒化物半導体層を順次積層した構造を有するため、Al組成が階段状に変化している。第2窒化物半導体層200を形成する複数の半導体層は、それぞれが同一方向に分極している。そしてゲート電極420に近い半導体層は、ゲート電極420から遠い半導体層よりも、分極の強度が強く(又は弱く)なっている。すなわち複数の半導体層は、ゲート電極420に近づくにつれて、分極の強度が一方向に変化している。この分極の方向は、複数の半導体層内の界面において負の電荷が正の電荷よりも多くなる方向である。

(もっと読む)

抵抗変化物質を含む半導体素子及びその製造方法

【課題】抵抗変化物質を含む半導体素子及びその製造方法を提供する。

【解決手段】印加された電圧によって抵抗が変化する抵抗変化物質をチャネル層として含む半導体素子及びその製造方法、前記半導体素子を含む不揮発性メモリ装置に係り、前記半導体素子は、絶縁基板上に配置されたチャネル層、前記チャネル層内に配置されたゲート電極、前記ゲート電極を取り囲むゲート絶縁膜、前記ゲート電極の両側面で、前記チャネル層上に配置されるソース電極及びドレイン電極、並びに前記基板と前記ゲート電極との間に配置される抵抗変化物質層を含み、これにより、前記半導体素子は、スイッチの機能と不揮発性メモリの機能とを同時に遂行することができる。

(もっと読む)

電界効果トランジスタ

【課題】窒化物半導体を用いた電界効果トランジスタで、高いドレイン電流が実現できるようにする。

【解決手段】ドレイン電極107とゲート領域121との間のドレイン領域123の距離は、ソース電極106とゲート領域121との間のソース領域122の距離より長く形成され、加えて、ゲート電極104は、ゲート領域121からソース電極106の側に延在する延在部141を備えて形成されている。ゲート電極104のソース電極106の側への延在部141により、ゲート電極104に対する電圧印加でソース領域122のチャネル層101における電子濃度が増加可能とされている。

(もっと読む)

半導体装置の製造方法、半導体装置、SOI基板の製造方法およびSOI基板

【課題】SOI基板のチャージ蓄積による不良を抑制する。

【解決手段】まず、シード基板100の一面に、シード基板100の表面と同一面を形成するように、開口部220を有する絶縁層200を形成する(絶縁層形成工程)。次いで、シード基板100の一面に接するように、支持基板300を貼り合せる(貼り合せ工程)。次いで、シード基板100または支持基板300の一方を薄板化することにより、当該薄板化基板からなる半導体層120を形成する(半導体層形成工程)。以上の工程により、SOI基板を準備する。次いで、半導体層120に半導体素子60を形成する(半導体素子形成工程)。

(もっと読む)

HEMT装置を製造するCMOSコンパチブルな方法とそのHEMT装置

【課題】Si−CMOSプロセス時術とコンパチブルなHEMT装置の製造法を提供する。

【解決手段】基板101を提供するステップと、III族窒化物層のスタックを基板上に形成するステップと、窒化シリコンからなり、スタックの上方層に対して上に位置すると共に当接する第1パッシベーション層301を形成し、第1パッシベーション層が、現場でスタックに堆積されるステップと、第1パッシベーション層に対して上に位置すると共に当接する誘電体層を形成するステップと、窒化シリコンからなり、誘電体層に対して上に位置すると共に当接する第2パッシベーション層303を形成し、第2パッシベーション層が、LPCVD、MOCVD又は同等の手法によって450℃より高い温度で堆積されるステップと、ソースドレイン・オーミック接触とゲート電極601を形成するステップとを備える。

(もっと読む)

21 - 40 / 784

[ Back to top ]