Fターム[5F140BF16]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 2層目材料 (3,048) | 金属 (2,560) | 合金 (39)

Fターム[5F140BF16]に分類される特許

1 - 20 / 39

半導体装置及びその製造方法

【課題】higher-k材料であるチタン酸化膜の半導体基板との界面を安定化でき、さらなる微細化に対応できるゲート構造を実現できるようにする。

【解決手段】半導体装置は、半導体基板1の上に形成されたゲート絶縁膜と、該ゲート絶縁膜の上に形成されたゲート電極とを備えている。ゲート絶縁膜は、アナターゼ型酸化チタンを主成分とする高誘電率絶縁膜5であり、ゲート電極は、第1の金属膜6又は第2の金属膜8を含む導電膜から構成されている。

(もっと読む)

半導体集積回路装置の製造方法

【課題】高誘電率ゲート絶縁膜を用いたCMIS型半導体集積回路において、短チャネル長、且つ狭チャネル幅のデバイス領域では、ソースドレイン領域の活性化アニールによって、高誘電率ゲート絶縁膜とシリコン系基板部との界面膜であるILの膜厚が増加することによって、閾値電圧の絶対値が増加するという問題がある。

【解決手段】本願の一つの発明は、MISFETを有する半導体集積回路装置の製造方法において、MISFETのゲートスタック及びその周辺構造を形成した後、半導体基板表面を酸素吸収膜で覆い、その状態でソースドレインの不純物を活性化するためのアニールを実行し、その後、当該酸素吸収膜を除去するものである。

(もっと読む)

半導体装置の製造方法

【課題】微細化を達成するとともに、ゲート電極等の信頼性を確保する半導体装置の製造方法を提供する。

【解決手段】N型MISトランジスタ及びP型MISトランジスタのそれぞれのゲート形成領域において、N型MISトランジスタのゲート形成領域の凹部内に形成されたゲート絶縁膜F0上に第1の金属含有膜F1を、P型MISトランジスタのゲート形成領域の凹部内に形成されたゲート絶縁膜F0上に第3の金属含有膜F3を形成し、第1の金属含有膜F1上及び第3の金属含有膜F3上に第2の金属含有膜F2を形成し、N型MISトランジスタのゲート絶縁膜F0に接する第1の金属含有膜F1の仕事関数がP型MISトランジスタのゲート絶縁膜F0に接する第3の金属含有膜F3の仕事関数よりも小さい。

(もっと読む)

半導体装置

【課題】短チャネルでもオフ特性の優れたトランジスタ等の半導体装置を提供する。

【解決手段】ソース102aの周囲をエクステンション領域103aおよびハロー領域105a、ドレイン102bの周囲をエクステンション領域103bおよびハロー領域105bで取り囲むように配置し、また、不純物濃度の低い基板101がソース102a、ドレイン102bと接しない構造とする。さらに、ゲート絶縁物109を介して高仕事関数電極104を設け、基板101の表面近傍にエクステンション領域103aおよびエクステンション領域103bより侵入する電子を排除する。このような構造とすることにより、短チャネルでもチャネル領域の不純物濃度を低下させることができ、良好なトランジスタ特性を得ることができる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】エッチング量を少なくしても素子分離膜の周辺にHigh−kゲート絶縁膜材料やゲート電極材料が残ることを抑制できるようにする。

【解決手段】素子分離膜102はSTI構造を有しており、基板101に埋め込まれており、かつトランジスタが形成される素子形成領域を分離している。素子分離膜102の側面の上端は、トランジスタのチャネル形成層よりも上に位置しており、かつチャネル形成層の表面から素子分離膜102の側面の最上部までの高さhが35nm以下である。また素子分離膜102のうちチャネル形成層よりも上に位置している部分の側面は、基板の表面に対する角度θが80度以下である。

(もっと読む)

半導体デバイス及びその製造方法

本願は、半導体デバイス及びその製造方法に関するものである。本発明の半導体デバイスの製造方法は、半導体基板を提供する工程と、半導体基板に、該半導体基板に形成されたゲート絶縁層及び該ゲート絶縁層に形成された犠牲ゲートを含むゲート領域と、ソース/ドレイン領域とを含むトランジスタ構造を形成する工程と、第1の層間絶縁層を堆積し、犠牲ゲートを露出させるように該第1の層間絶縁層に対して平坦化を行う工程と、犠牲ゲートを除去して、リプレースメントゲートホールを形成する工程と、第1の層間絶縁層におけるソース/ドレイン領域に対応する位置に、第1のコンタクトホールを形成する工程と、第1のコンタクトホール及びリプレースメントゲートホールに第1の導電材料を充填して、ソース/ドレイン領域に接触する第1のコンタクト部と、リプレースメントゲートとを形成する工程とを含む。本発明によれば、リプレースメントゲートと第1のコンタクト部は、同一の工程で同じ材料を堆積して形成することができるため、製造プロセスを簡単化できた。  (もっと読む)

(もっと読む)

ダイヤモンド半導体素子及びその製造方法

【課題】耐電圧、耐熱性、耐放射線性、及び高速性が優れ、かつ、チャネル領域を短くでき、素子の応答性が高いダイヤモンド半導体素子を高精度で製造できる半導体素子の製造方法を提供する。

【解決手段】第1のダイヤモンド半導体領域1の表面上に、絶縁膜2と多層金属電極層3と犠牲層4とを積層し、犠牲層4上に、局所的にレジスト5をパターン形成する。多層金属電極層3の最上層は、Pt又はPt合金により形成する。そして、レジスト5をマスクとして第1の犠牲層、多層金属電極層及び絶縁膜をエッチングした後、レジスト5を除去して、第1のダイヤモンド半導体領域1上に絶縁膜2と金属電極層3と第1の犠牲層4との積層体をパターン形成する。その後、第1のダイヤモンド半導体領域1上に、不純物の高濃度ドープ層7を形成する。その後、犠牲層4をエッチング除去し、高濃度ドープ層7上に金属電極8を形成する。

(もっと読む)

半導体装置の製造方法

【課題】 置換ゲート工程で発生する不良を防止できる半導体装置の製造方法を提供する。

【解決手段】本発明による半導体装置の製造方法は、半導体基板上にゲート絶縁膜および犠牲ゲート電極を含むゲートパターンを形成する段階、前記半導体基板および前記ゲートパターン上にエッチング停止層および絶縁層を形成する段階、前記エッチング停止層が露出するまで前記絶縁層を除去する段階、前記犠牲ゲート電極が露出するまで前記エッチング停止層をエッチバックする段階、前記犠牲ゲート電極を除去し、結果物の全体構造の上面に金属層を形成する段階、前記絶縁層が露出するまで前記金属層を除去する段階、および前記金属層を所定の深さでエッチバックする段階を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】仕事関数を十分に制御することができ、閾値電圧の変動を抑制した半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体装置1は、半導体基板10に第1導電型チャネルMOSFETを備える。第1導電型チャネルMOSFETは、例えばPチャネルMOSFETであって、半導体基板10の上に設けられたゲート絶縁膜21と、ゲート電極65とからなる。ゲート電極65は、ゲート絶縁膜21の上に設けられた金属ゲート電極20と、金属ゲート電極20の上に設けられた金属酸化膜24と、金属酸化膜24の上に設けられた金属ゲート電極26と、を含んでいる。

(もっと読む)

半導体装置およびその製造方法

【課題】メタルゲート電極を有するpチャネル型電界効果トランジスタにおいて、所望するしきい値電圧を安定して得ることのできる技術を提供する。

【解決手段】半導体基板1上に形成されたHfSiON膜からなるゲート絶縁膜5h上に、Me−O−Al−O−Me結合を含むMe1−xAlxOy(0.2≦x≦0.75、0.2≦y≦1.5)組成の導電性膜を一部に有するメタルゲート電極6、またはMe−O−Al−N−Me結合を含むMe1−xAlxN1−zOz(0.2≦x≦0.75、0.1≦z≦0.9)組成の導電性膜を一部に有するメタルゲート電極6を形成する。

(もっと読む)

非対称型半導体デバイス及び製造方法

【課題】 非対称型半導体デバイス、及びその製造の際にスペーサ・スキームを用いる方法を提供する

【解決手段】 高kゲート誘電体の表面上に配置された非対称型ゲート・スタックを含む半構造体が提供される。非対称型ゲート・スタックは、第1の部分と第2の部分とを含み、第1の部分は、第2の部分とは異なる閾値電圧を有する。本発明の非対称型ゲート・スタックの第1の部分は、下から上に、閾値電圧調整材料及び少なくとも第1の導電性スペーサを含み、本発明の非対称型ゲート・スタックの第2の部分は、ゲート誘電体の上の少なくとも第2の導電性スペーサを含む。幾つかの実施形態において、第2の導電性スペーサは、下にある高kゲート誘電体と直接接触しており、他の実施形態においては、第1及び第2の導電性スペーサは、前記閾値電圧調整材料と直接接触している。

(もっと読む)

半導体装置及びその製造方法

【課題】高い仕事関数及び高温安定性を備えたメタルゲートを有する半導体装置及びその製造方法を提供する。

【解決手段】半導体基板上に形成されたゲート誘電体層108と、ゲート誘電体層108上に形成された酸素を含む合金層110と、酸素を含む合金層110上に形成されたRe層112と、ゲート誘電体層108と酸素を含む合金層110との間に位置するRe酸化物層502を含むp 型電界効果トランジスタを具備する。

(もっと読む)

高電力マイクロ電子デバイスのための金属化構造

【課題】高電力で高性能なデバイスによって生成される熱応力に耐えることができる金属相互接続システムを提供する。

【解決手段】半導体デバイス構造であって、炭化ケイ素およびIII族窒化物からなる群から選択される広バンドギャップの半導体部分と、該半導体部分に対する相互接続構造であって、それぞれ2つの高導電性層と互い違いに、少なくとも2つの拡散バリア層を含む、相互接続構造とを備え、該拡散バリア層は、該高導電性層とは異なる熱膨張係数を有し、該高導電性層よりも低い熱膨張係数を有し、該それぞれの熱膨張係数の差異は、該高導電性層の膨張を抑えるために十分な大きさであるが、層間の接着強度を超える歪みを隣接層間に生じさせる差異よりも小さい、半導体デバイス構造。

(もっと読む)

ALD技術を用いたドーピング

【課題】阻害反応物を用いてドーパント前駆体が利用可能な結合部位の一部を阻害することによって、堆積したドーパントの濃度および均一性を制御することができる。ALDプロセスにおいて、阻害反応物をドーパント前駆体の導入前に導入することができる、または阻害反応物およびドーパント前駆体を同時に導入することができる。

【解決手段】原子層堆積プロセス(ALD)によって、基板表面または2つの薄膜間の界面をドープする方法が提供される。

(もっと読む)

半導体素子

【課題】インバータ回路など、電気接続された2つの半導体スイッチによるスイッチング動作を行なうための電気回路において、寄生インダクタンスおよびオン抵抗を抑制することができる構造の半導体素子を提供すること。

【解決手段】この半導体素子は、基板1と、基板1の一方側に形成される半導体積層構造部2とを備える。半導体積層構造部2は、n型層5、このn型層5の一方側(下面側)に積層されたp型層4、およびこのp型層4に積層されたn型層3からなる縦型npn構造の第1半導体積層構造8と、n型層5をこの第1半導体積層構造8と共有し、n型層5、このn型層5の他方側(上面側)に積層されたp型層6、およびこのp型層6に積層されたn型層7からなる縦型npn構造の第2半導体積層構造9とを備える。

(もっと読む)

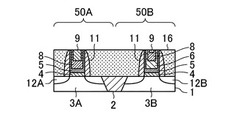

半導体装置及びその製造方法

【課題】駆動能力を低下させることなく、半導体装置内部の高電界が与える影響によって生じるGIDLを低減する。

【解決手段】ゲート電極108は、ゲート電極108のチャネル長方向の中央部に位置し且つ高誘電率膜107つまりゲート絶縁膜と接する第1の導電部108Aと、ゲート電極108のチャネル長方向の両端部に位置し且つ高誘電率膜107つまりゲート絶縁膜と接する第2の導電部108Bとを含む。第1の導電部108Aの第1の仕事関数と第2の導電部108Bの第2の仕事関数とが異なっている。

(もっと読む)

半導体装置

【課題】 ゲート電極上のシリサイド膜の断線を抑制する。

【解決手段】 ソース・ドレイン領域をデュアルシリサイド構造とし、ゲート電極の仕事関数はn型MISトランジスタ、p型MISトランジスタそれぞれの有するメタルゲート電極により定める構造とし、且つ、メタルゲート電極上の多結晶シリコン層は共通のn+ドーピング層とし、ゲート上シリサイド膜はn型領域に対しショットキー障壁が低くなる材料で形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】Pチャネル型トランジスタの閾値電圧を制御することができる半導体装置、およびその半導体装置の製造方法を提供する。

【解決手段】NTrとPTrとを含む半導体装置において、N型チャネル形成領域とP型チャネル形成領域とを有するN型半導体基板2上に絶縁膜Fが形成され、絶縁膜Fにゲート電極用溝A及びBとが形成され、ゲート電極用溝A及びBの内側表面上にゲート絶縁膜20が形成され、NTr領域におけるゲート絶縁膜20上にNTr仕事関数制御メタル膜21が形成され、NTr仕事関数制御メタル膜21及びゲート絶縁膜20上にフッ素がドープされたPTr仕事関数制御メタル膜23が形成され、PTr仕事関数制御メタル膜23の上層に、ゲート電極用溝に埋め込まれてゲート電極が形成されている構成とする。

(もっと読む)

電界効果型トランジスタの修復方法、半導体装置の修復方法、半導体装置の作製方法、及び半導体装置

【課題】電界効果型トランジスタのリーク電流を低減し、寿命の向上を図るための簡便な修復方法を提供することを課題とする。また、作製コストの増加を抑え、消費電力が小さく、且つ信頼性の高い半導体装置を提供することを課題とする。

【解決手段】ソース電極又はドレイン電極の一方と、ゲート電極との間に、電気的な衝撃を加える。または、ソース電極又はドレイン電極の一方と、ソース電極又はドレイン電極の他方との間に、電気的な衝撃を加える。これにより、リークパスを絶縁化し、リーク電流を低減することができる。なお、上記の電気的な衝撃は、静電気等の電気パルスであっても良いし、直流電圧、交流電圧、直流電流、交流電流等であっても良い。

(もっと読む)

半導体装置およびその製造方法

【課題】従来のCMISデバイスにおいては、価電子帯端近くの高い仕事関数を有する金属は、還元雰囲気アニール後に実効仕事関数が低下する。

【解決手段】半導体装置は、ソースとドレイン間のN型半導体層上に形成された金属元素を含むゲート絶縁膜と、ゲート絶縁膜上に形成され、膜厚が3nm以下であるカーボン層と、カーボン層上に形成されたゲート電極とを有し、ゲート電極/ゲート絶縁膜界面へのカーボン層による仕事関数の上昇効果により、還元雰囲気アニール耐性のない価電子帯端近くの高い仕事関数を有する金属を用いずとも、PMISFETに必要な実効仕事関数を得ることができ、低い閾値電圧を実現する。

(もっと読む)

1 - 20 / 39

[ Back to top ]