Fターム[5F140BG37]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極及び側壁の製造 (21,161) | ゲート電極の形成処理 (7,666) | ゲート電極の形状を形成する方法 (2,844) | エッチング (1,849)

Fターム[5F140BG37]の下位に属するFターム

ドライエッチング (966)

Fターム[5F140BG37]に分類される特許

161 - 180 / 883

半導体装置およびその製造方法

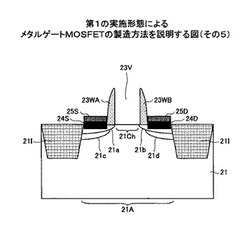

【課題】CMPによるダミーゲート電極の頭出し工程およびCMPによるメタルゲート電極の形成工程を回避できる製造方法を提供する。

【解決手段】シリサイド膜24S,24D上に選択的に、シリコン膜25S,25Dを形成する工程と、側壁絶縁膜23WA,23WBの間にシリコン基板の表面を露出する凹部23Vを形成する工程と、側壁絶縁膜23WA,23WBの表面および露出されたシリコン基板表面を連続して覆うように、誘電体膜を形成する工程と、シリコン基板上に金属または導電性金属窒化物を含む導電膜を、凹部23Vに誘電体膜を介して充填するように形成する工程と、導電膜をエッチバックし、側壁絶縁膜23WA,23WBの間において凹部23Vを誘電体膜を介して充填するゲート電極を形成する工程と、を含む。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ゲート閾値電圧を低下させることなく、チャネル移動度を向上できる炭化珪素MOSFETを提供する。

【解決手段】炭化珪素半導体装置200は、炭化珪素基板10と、炭化珪素基板10上に形成された炭化珪素層20と、炭化珪素層20上に形成されたゲート絶縁膜30と、ゲート絶縁膜30を介して炭化珪素層20上の所定位置に形成され、III族軽元素であるB、AlまたはGaをp型ドーパントとして含む多結晶シリコンからなるゲート電極40とを有する。そして、ゲート電極40中の上記p型ドーパントを、ゲート電極40直下の炭化珪素層20とゲート絶縁膜30との界面近傍に拡散させ、上記p型ドーパントによって界面近傍の不純物準位をパッシベーションする。

(もっと読む)

自己整合コンタクト

トランジスタは、基板と、基板上の一対のスペーサと、基板上且つスペーサ対間のゲート誘電体層と、ゲート誘電体層上且つスペーサ対間のゲート電極層と、ゲート電極層上且つスペーサ対間の絶縁キャップ層と、スペーサ対に隣接する一対の拡散領域とを有する。絶縁キャップ層は、ゲートにセルフアラインされるエッチング停止構造を形成し、コンタクトエッチングがゲート電極を露出させることを防止し、それにより、ゲートとコンタクトとの間の短絡を防止する。絶縁キャップ層は、セルフアラインコンタクトを実現し、パターニング限界に対して一層ロバストな、より幅広なコンタクトを最初にパターニングすることを可能にする。  (もっと読む)

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】ピラー型MOSトランジスタに関し、チャネルがフローティング状態になることを防止できる半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置200は、基板11に立設された、トランジスタ用の第一のピラー1と、前記第一のピラー1に隣接された、前記第一のピラー1のチャネル16と同じ導電型の連結部14と、前記第一のピラー1に連結部14を介して隣接された、前記チャネル16と同じ導電型の、前記第一のピラー1のチャネル16電位制御用の第二のピラー2と、を有し、前記第二のピラー2上面に、電位を与える構造を有することを特徴とする。

(もっと読む)

ドープされたエピタキシャル領域を有する半導体装置およびその製造方法

本発明の実施例として、半導体装置上のエピタキシャル領域を示した。ある実施例では、エピタキシャル領域は、成膜−エッチングプロセスを経て基板に成膜される。周期的な成膜−エッチングプロセスの間に、スペーサの下側に形成されるキャビティは、エピタキシャルキャップ層によって埋め戻される。エピタキシャル領域およびエピタキシャルキャップ層は、チャネル領域での電子移動度を改善し、短チャネル効果が抑制され、寄生抵抗が低下する。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】配線層の加工マージンが大きく、微細化に適した半導体装置の製造方法を提供する。

【解決手段】半導体基板1にゲート電極溝を形成する工程と、ゲート電極溝の内壁面にゲート絶縁膜15を形成する工程と、ゲート電極溝の底部に埋め込みゲート電極23Aを形成する工程と、埋め込みゲート電極23Aの上面を覆うようにゲート電極溝の内部に絶縁膜を埋め込んだ後、エッチバックして当該ゲート電極溝の上部にキャップ絶縁膜22を形成する工程と、半導体基板1の上面に層間絶縁膜24を形成する工程と、層間絶縁膜24にビットコンタクト開口部を形成する工程と、を備え、半導体基板1の上面に層間絶縁膜24を形成する工程が、半導体基板1の上面とキャップ絶縁膜22の上面との間に生じた段差を埋め込むように層間絶縁膜24を成膜するとともに当該層間絶縁膜24の上面を平坦とすることを特徴とする半導体装置の製造方法である。

(もっと読む)

半導体装置、および、半導体装置の製造方法

【課題】チャネル領域に強い歪みを印加することによりデバイス特性を改善した半導体装置を提供すること。

【解決手段】半導体基板1と、半導体基板1の第1の面に形成されたゲート絶縁膜2と、ゲート絶縁膜2の上に形成されたゲート電極3と、ゲート電極3の側壁に形成されたゲート側壁絶縁膜4と、ゲート電極3の下の半導体基板1中に形成されるチャネル領域に隣接し、不純物が注入されたソース/ドレイン拡散層領域5、6と、ゲート電極3の上方を除き、ソース/ドレイン拡散層領域5、6の上に形成された応力印加膜8と、を有し、半導体基板1の第1の面におけるソース/ドレイン拡散層領域5、6が形成された領域には、凹部または凸部50、51、60、61が設けられている半導体装置を提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】MOSトランジスタのオン電流を低下させずにMOSトランジスタを小型化する。

【解決手段】素子形成領域2を他の領域と分離する素子分離領域3が形成された基板(半導体基板1)と、素子形成領域2に形成されたゲート溝4と、素子形成領域2にゲート溝4を挟んで離間して形成された一対の拡散領域5を有する。更に、ゲート溝4内及びゲート溝4の周囲縁部に形成されたゲート6を有する。ゲート溝4は、チャネル幅方向Dではその開口端4aの形状が素子分離領域3により画定され、且つ、チャネル長方向Eでは一対の拡散領域5にそれぞれ接するように形成されている。チャネル幅方向Dにおいて、ゲート溝4と素子分離領域3との間に、一対の拡散領域5を繋ぐ半導体領域(シリコン領域20)を有している。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタを備えた半導体装置において、トランジスタのGIDLを抑制する。

【解決手段】縦型トランジスタを備えた半導体装置に関する。縦型トランジスタは、半導体領域と、半導体領域上に設けられた柱状領域と、柱状領域の側面を覆うように設けられたゲート絶縁膜と、ゲート絶縁膜上に設けられたゲート電極と、柱状領域の上部に設けられた第1の不純物拡散領域と、半導体領域内に柱状領域を囲むように設けられた第2の不純物拡散領域と、を有する。第1の不純物拡散領域は、柱状領域の側面と離間するように設けられている。

(もっと読む)

非対称スペーサをゲートとして備えるLDMOSトランジスタ

【課題】本発明は、横方向拡散金属酸化物半導体(LDMOS)トランジスタと、これを製造する方法を提供する。

【解決手段】LDMOSトランジスタはp型基板上に形成されたn型エピタキシャル層と、LDMOSトランジスタのゲートとして機能する非対称導体スペーサとを備える。LDMOSトランジスタはまた、非対称導体スペーサの両側のソース領域及びドレイン領域と、イオン注入を非対称導体スペーサに行うことで形成されたチャネル領域とを備える。非対称導体スペーサの高さはソース領域からドレイン領域に向かって増加する。チャネル領域は、基本的に完全に非対称導体スペーサの下に存在し、従来技術のLDMOSトランジスタのチャネル領域の長さよりも短い長さを有する。本発明のLDMOSトランジスタはまた、当該トランジスタの活性領域を囲むフィールド酸化物層と、非対称導体スペーサをn型エピタキシャル層から絶縁する薄い誘電体層とを備える。

(もっと読む)

MOS型半導体装置

【課題】所望の位置に所望の厚さのゲート酸化膜を有する、高性能かつ長寿命のMOS型半導体を提供すること。

【解決手段】半導体基板と、該半導体基板上にゲート酸化膜を介して形成されたゲート電極とを含み、該ゲート酸化膜の両端部に接するように該半導体基板上にそれぞれ設けられた、該半導体基板の導電型とは異なる導電型の不純物を含む2つの不純物活性領域をそれぞれソース電極及びドレイン電極とする、MOS型半導体装置であって、該ゲート酸化膜を介して形成されたゲート電極は、それぞれが該半導体基板とゲート酸化膜を介して形成された構造を有する複数の領域からなり、各領域の該ゲート酸化膜の厚さが少なくとも2種類の異なる厚さで構成され、該各領域は互いに接合されている、ことを特徴とするMOS型半導体装置。

(もっと読む)

トレンチ型パワーMOSトランジスタおよびその製造方法

【課題】パワーMOSトランジスタにおいて、高い降伏電圧、高い出力電流および高速の動作速度を備えるのみならず、水平構造を備えるために、CMOSの製造工程で製作された一般的な集積回路と同一のチップ上に整合させる。

【解決手段】本発明のトレンチ型パワーMOSトランジスタはゲート導電体312と、絶縁層310とを備えたトレンチ型ゲート領域を具備する。絶縁層310は、ゲート導電体312と井戸領域308との間で薄い側壁領域を形成しており、ゲート導電体312と二重拡散のドーピング領域306との間で厚い側壁領域を形成するとともに、ゲート導電体312と深井戸領域304との間で厚い最下部領域を形成している。

(もっと読む)

半導体装置、半導体チップ及び半導体装置の製造方法

【課題】製造工程中にピラー径の変動が小さいピラー型MOSトランジスタを備えた半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置は、基板対して垂直に立設する第1のピラー及び第2のピラーの側面にゲート絶縁膜を介して形成されたゲート電極と、第1のピラーの先端部及び基端周囲領域に形成された上部拡散層及び下部拡散層と、を備え、第2のピラーのゲート電極と隣接する第1のピラーのゲート電極とは接続されており、第1のピラーのゲート電極には第2のピラーのゲート電極を介して電位が供給され、第1のピラーと、該第1のピラーに隣接する第2のピラーの少なくとも一部とは平面視して、第1のピラー及び第2のピラーの側面を構成する面のうち、熱酸化速度及び/又はエッチング速度が最大の面に対して45°の方向に沿って配置されていることを特徴とする。

(もっと読む)

半導体素子及びトランジスタ

【課題】ゲートとチャンネル部との接触面を増大させ電流の損失を減らし、チャンネルを形成する半導体層の格子特性を変化させ電子移動度を向上させることができる半導体素子及びトランジスタを提供すること、及び、ゲートと接触する面積が増大され、半導体層の格子特性も向上されてチャンネル部内の電子の流れを改善し、電力消耗も減らすことができる半導体素子及びトランジスタを提供すること、を目的とする。

【解決手段】半導体基板上に形成されて第1半導体パターンを含む3次元直線状の第1構造物と、第一構造物の中心部を貫通するように配置され、第1半導体パターンと異なる結晶構造を有する第2半導体パターンを含む第2構造物と、第1構造物に対して直交する方向に延長して3面で第2構造物の一部を囲むゲートを含むトランジスタとする。

(もっと読む)

半導体装置の製造方法

【課題】 高誘電体ゲート絶縁膜およびシリコン基板との界面を高品質化して、MISFETの特性向上を図る。

【解決手段】 シリコン基板11上にhigh−k膜21とゲート電極24を形成する半導体装置の製造方法において、high−k膜形成後にフッ素雰囲気でアニール処理23を施し、その後のプロセス温度を600℃以下で行う、半導体装置の製造方法。

(もっと読む)

半導体デバイス及びその製造方法

【課題】従来よりも界面準位密度を低減させることができる半導体デバイス及びその製造方法を提供する。

【解決手段】窒素ガス雰囲気下で低ダメージなECRプラズマを用いたECRプラズマ処理を行うことにより、III−V族化合物半導体層2の表面を窒化処理したことで、当該III−V族化合物半導体層2にIn−N結合及びGa−N結合を形成しAs酸化物を抑制して界面特性を向上させることができ、かくして従来よりも界面準位密度が低減されたMOSFET1を提供できる。また、アニール処理することにより、窒化処理層5においてGa−N結合が支配的となった界面結合状態を形成し、界面準位密度を一段と低減させることができる。

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

幅広い電子デバイスのアレイ及びシステムにおける電力消費を低減する一式の新たな構造及び方法が提供される。これらの構造及び方法のうちの一部は、大部分が既存のバルクCMOSのプロセスフロー及び製造技術を再利用することで実現され、半導体産業及びより広いエレクトロニクス産業がコスト及びリスクを伴って代替技術へ切り替わることを回避可能にする。これらの構造及び方法のうちの一部は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することと、チャネル領域にドーパントを有するFETの閾値電圧VTがより一層正確に設定されることとを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有することができ、それにより、DDCトランジスタにおける電力消費の有意義な動的制御が可能になる。  (もっと読む)

(もっと読む)

トランジスタの製造方法

【課題】ゲートとチャンネル部との接触面を増大させ電流の損失を減らし、チャンネルを形成する半導体層の格子特性を変化させ電子移動度を向上させることができるトランジスタの製造方法を提供すること、及び、ゲートと接触する面積が増大され、半導体層の格子特性も向上されてチャンネル部内の電子の流れを改善し、電力消耗も減らすことができるトランジスタの製造方法を提供すること、を目的とする。

【解決手段】半導体基板上に第1半導体層及び第1半導体層と異なる格子定数と結晶構造を有する第2半導体層を順次形成する段階と、第2半導体層及び第1半導体層をエッチングして格子定数の差によって第1半導体層の結晶構造が変形された変形結晶構造を有し、直線状の第1半導体パターンを形成する段階と、第1半導体パターン上に第1半導体層と同一な結晶構造を有する第3半導体層を形成する段階とを含む。

(もっと読む)

半導体装置の製造方法

【課題】 DMOSトランジスタのオン抵抗のバラツキをなくすために、チャネル抵抗のバラツキが生じない製造方法を提供する。

【解決手段】 半導体基板上に第1ボディー領域を形成した後、ゲート酸化膜上にゲート電極膜を積層する。第2ボディー領域を形成するためフォトレジストをマスクとして使用し、開口を形成する。本発明は、フォトレジストを残したまま開口内に不純物イオンを注入し、チャネル領域を構成する第2ボディー領域を形成する。さらに同じマスクを使用して第1ソース領域を形成する。次に、ゲート電極を形成し、サイドスペーサーを形成した後、第2ソース領域とドレイン領域とを同時に形成する。

(もっと読む)

自己整合損傷層を有するデバイス構造体の形成方法

【解決課題】 自己整合損傷層を有するデバイス構造体の形成方法を提供すること。

【解決手段】デバイス構造体は、基板の半導体材料内部に画定された第1導電型の第1及び第2ドープ領域を有する。逆の導電型の第3ドープ領域が、横方向に第1ドープ領域を第2ドープ領域から分離する。ゲート構造部が基板の上表面に配置され、第3ドープ領域と垂直方向で重なる関係を有する。第1結晶損傷層は基板の半導体材料の内部に画定される。第1結晶損傷層は、基板の半導体材料によって取り囲まれた第1の複数のボイドを有する。第1ドープ領域は、第1結晶損傷層と基板の上表面との垂直方向の間に配置される。第1結晶損傷層は横方向に第3ドープ領域内には延びない。

(もっと読む)

161 - 180 / 883

[ Back to top ]