Fターム[5F140BG37]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極及び側壁の製造 (21,161) | ゲート電極の形成処理 (7,666) | ゲート電極の形状を形成する方法 (2,844) | エッチング (1,849)

Fターム[5F140BG37]の下位に属するFターム

ドライエッチング (966)

Fターム[5F140BG37]に分類される特許

201 - 220 / 883

半導体装置

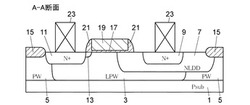

【課題】MOSトランジスタの高耐圧化、オン抵抗の低減、HCI耐性の向上、及びデザインルールの縮小を実現する。

【解決手段】MOSトランジスタのドレインは、チャネル長方向で一端がP型低濃度ウェル3内に配置され、他端がP型ウェル5内に配置されたN型低濃度ドレイン7と、低濃度ウェル3上の低濃度ドレイン7内に低濃度ドレイン7の端部とは間隔をもって配置されたN型高濃度ドレイン9からなる。ソースは、チャネル長方向で一端が低濃度ドレイン7とは間隔をもって低濃度ウェル3内に配置され、他端がウェル5内に配置されたN型高濃度ソース11と、低濃度ウェル3内で高濃度ソース11に隣接し、低濃度ドレイン7とは間隔をもって配置されたN型低濃度ソース13からなる。ゲート電極19は、高濃度ドレイン9−低濃度ソース13間の低濃度ウェル3上及び低濃度ドレイン7上に高濃度ドレイン9とは間隔をもって配置されている。

(もっと読む)

誘電体膜、誘電体膜を用いた半導体装置の製造方法及び半導体製造装置

【課題】高誘電率を有する誘電体膜の製造方法を提供する。

【解決手段】薄いシリコン酸化膜を形成したSi基板上に、HfN/Hf積層膜を形成し、アニール処理によりHf、Si、O、Nの混合物からなる金属酸窒化物とする誘電体膜の製造する。(1)EOTの低減が可能であり、(2)リーク電流がJg=1.0E−1A/cm2以下に低減され、(3)固定電荷の発生によるヒステリシスが抑制され、(4)700℃以上の熱処理を行ってもEOTの増加が無く耐熱性に優れる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】容易に製造できる半導体装置を提供する。

【解決手段】半導体装置は、PMOSトランジスタのゲート電極1pの仕事関数値が、High-kゲート絶縁膜16(16a)、及び、High-kゲート絶縁膜16・酸化シリコン膜15界面へのAlの拡散により調整されており、NMOSトランジスタのゲート電極1nの仕事関数値が、High-kゲート絶縁膜16・金属ゲート膜19間に挿入された、数原子層程度のAl層18により調整されている構成を有する。

(もっと読む)

半導体装置の製造方法

【課題】 半導体装置の製造方法に関し、シリサイドを構成する金属のサイドウォールの直下への潜り込みの影響を低減する。

【解決手段】 シリコン基板上にゲート電極を形成する工程と、ゲート電極の側壁に、第1絶縁膜による第1サイドウォールと、第1サイドウォール上にあって、第1絶縁膜とはエッチング特性の異なる第2絶縁膜による第2サイドウォールを形成する工程と、シリコン基板および第2サイドウォールを含む表面に金属をスパッタリングにより堆積させ、金属の一部をシリコン基板に侵入させる工程と、シリコン基板上に堆積した金属を除去する工程と、金属の除去工程の後に熱処理を行って、スパッタリングによってシリコン基板に侵入した金属とシリコン基板中のシリコン原子とを反応させてシリサイド層を形成する工程とを備える。

(もっと読む)

半導体素子およびその製造方法

【課題】半導体素子の低オン抵抗化を実現し、全体の製造工程数を低減する半導体素子およびその製造方法を提供すること。

【解決手段】ソース・ドレイン領域を形成する際のイオン注入時に、低耐圧横型トレンチMOSFETでは、ドレイン形成用の開口部がトレンチ側壁から離れ、ソース形成用の開口部がトレンチ側壁に達し、トレンチ横型パワーMOSFETでは、ソース形成用の開口部がトレンチ側壁から離れ、ドレイン形成用の開口部がトレンチ側壁に達するパターンのマスクを用いる。このマスクを用いて、高ドーズ量および低加速電圧で行うイオン注入と、低ドーズ量および高加速電圧で行うイオン注入を連続して行うことによって、低耐圧横型トレンチMOSFETのLDD領域と、トレンチ横型パワーMOSFETのLDD領域とを同時に形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】pMOSトランジスタにcSiGeとeSiGeを適用し、且つゲート絶縁膜におけるダメージ発生を防止でき、素子特性の向上及びしきい値制御性の向上をはかる。

【解決手段】pMOSトランジスタのチャネル部及びソース・ドレイン領域にSiGeを用いた半導体装置において、Si基板202上の一部に形成され、pMOSトランジスタのチャネルとなる第1のSiGe層205と、第1のSiGe層205上にゲート絶縁膜206を介して形成されたゲート電極208と、pMOSトランジスタのソース・ドレイン領域に埋め込み形成され、且つチャネル側の端部が基板表面よりも深い位置でチャネル側に突出するように形成された第2のSiGe層214と、第1のSiGe層205と第2のSiGe層214とを分離するように、基板の表面部でSiGe層205,214間に挿入されたSi層222とを備えた。

(もっと読む)

高kゲート誘電体のための、不純物酸素を捕捉する半導体構造および該構造を形成する方法(高kゲート誘電体のための捕捉金属スタック)

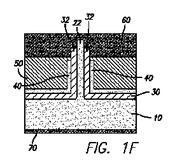

【課題】CMOS集積過程での高温処理の後であっても一定の閾値電圧を維持する高kゲート誘電体の提供。

【解決手段】高kゲート誘電体30と、下部金属層40、捕捉金属層50、および上部金属層60を含む金属ゲート構造とのスタックを提供する。該捕捉金属層は、次の2つの基準、1)Si+2/yMxOy→2x/yM+SiO2の反応によるギブス自由エネルギの変化が正である金属(M)であること、2)酸化物形成に対する酸素原子あたりのギブス自由エネルギが、下部金属層の金属および上部金属層の金属より大きな負である金属であること、を満たす。これらの基準を満たす捕捉金属層は、酸素原子がゲート電極を通って高kゲート誘電体に向け拡散するときに該酸素原子を捕捉する。さらに、該捕捉金属層は、高kゲート誘電体の下の酸化ケイ素界面層の厚さを遠隔から低減する。この結果、ゲート誘電体全体の等価酸化膜厚(EOT)の変動が抑制される。

(もっと読む)

パッシベートされたシリコンナノワイヤーの製造方法およびこれにより得られるデバイス

パッシベートされたシリコンナノワイヤーの製造方法およびこれにより得られる電子構造体について記載する。こうした構造体は、金属−酸化物−半導体(MOS)構造を含むことができ、構造体はMOS電界効果トランジスタ(MOSFET)または光電子スイッチに用いることができる。  (もっと読む)

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】突出部の側面が凹凸状とされ、前記側面を覆うようにゲート酸化膜を形成したときに、実効的なチャネル長が増加して、ピラー型MOSトランジスタの電流駆動能力が低下するという課題があった。

【解決手段】基板と、前記基板の一面から垂直方向に突出された突出部7とを備え、突出部7の先端側の上部拡散層と、基端側の下部拡散層と、側面7cを覆うゲート絶縁膜14と、ゲート絶縁膜14を覆うゲート電極15と、を有し、チャネルが前記垂直方向となるピラー型MOSトランジスタ51を具備し、突出部7が平面視八角形状であり、突出部7の側面7cが{100}面からなる4つの主表面8a、8b、8c、8dと、{110}面および{111}面からなり、前記主表面8a、8b、8c、8dよりも面積が小さい4つの副表面9a、9b、9c、9dとからなる半導体装置101を用いることにより、上記課題を解決できる。

(もっと読む)

半導体装置及びその製造方法

【課題】導電型に応じて容易に構成を変えることが可能なFinトランジスタ及びその製造方法を提供する。

【解決手段】半導体装置は、基板と、基板上に設けられた凸状の半導体からなるトランジスタ活性領域104と、トランジスタ活性領域104の一部の側面上及び上面上に設けられたゲート絶縁膜105aと、ゲート絶縁膜105aを間に挟んでトランジスタ活性領域104の側面及び上面の一部上に設けられたゲート電極350とを備えている。ゲート電極350のうち、トランジスタ活性領域104の側面上に設けられた部分の構成とトランジスタ活性領域104の上面上に設けられた部分の構成とは互いに異なっている。

(もっと読む)

半導体装置及びその製造方法

【課題】p型MISトランジスタを有する半導体装置において、p型のエクステンション拡散層の浅接合化を進めた場合でも、p型のエクステンション拡散層が高抵抗化されることを抑制する。

【解決手段】半導体装置は、半導体基板1に形成されたp型MISトランジスタpTrを備えた半導体装置である。p型MISトランジスタpTrは、第1の活性領域1a上に形成された第1のゲート絶縁膜2aと、第1のゲート絶縁膜2a上に形成された第1のゲート電極3aと、第1の活性領域1aにおける第1のゲート電極3aの側方下の領域に形成されたp型のエクステンション拡散層5aと、第1のゲート電極3aの側面上に形成された第1のサイドウォールスペーサ11Aとを備えている。第1のサイドウォールスペーサ11Aは、負の電荷が帯電した帯電サイドウォール6aと、帯電サイドウォール6aの上に形成された第1のサイドウォール10Aとを有している。

(もっと読む)

半導体装置およびその製造方法

【課題】メタルゲート電極の酸化を抑制しつつ、MOSFETの寄生容量の増大を抑制する。

【解決手段】半導体装置は、半導体基板10と、前記半導体基板上に形成されたシリコンと酸素とを含む第1絶縁膜12aと、前記第1絶縁膜上に形成された前記第1絶縁膜よりも誘電率が高く、高融点金属と酸素とを主成分とする第2絶縁膜12bと、で構成されるゲート絶縁膜12と、前記ゲート絶縁膜上に形成された金属層13を含むゲート電極15と、前記ゲート電極の前記金属層の側面、および前記ゲート絶縁膜の前記第2絶縁膜の側面に形成されたシリコンと窒素を含む第1側壁絶縁膜16と、前記第1側壁絶縁膜の側面、および前記第1絶縁膜の前記第1絶縁膜の側面に形成されたシリコンと酸素とを含む第2側壁絶縁膜17と、を具備する。

(もっと読む)

半導体装置及びその製造方法

【課題】PMISトランジスタのソースドレイン電極に高濃度のゲルマニウムを含むシリコンゲルマニウム層を用いても、シリコンゲルマニウム層に格子緩和を生じさせることなく、ソースドレイン電極の上部にシリコン層又は金属シリサイド層を形成できるようにする。

【解決手段】半導体装置は、n型半導体領域100の上にゲート絶縁膜101を介在させて形成されたゲート電極102と、その両側方に形成されたp型のソースドレイン電極150とを有している。ソースドレイン電極150は、n型半導体領域100に設けられた各リセス部100aに、その底部から少なくともチャネル領域の深さにまで形成されたシリコンゲルマニウム層111と、その上に形成され、炭素とシリコンゲルマニウム層のゲルマニウム濃度よりも低いゲルマニウムとを含むカーボンドープドシリコンゲルマニウム層112と、その上に形成された金属シリサイド層115とから構成される。

(もっと読む)

半導体装置の製造方法

【課題】 トランジスタのスイッチング速度低下を防止することが可能な半導体装置の製造方法を提供する。

【解決手段】 本発明では、半導体基板100上にゲート絶縁膜104を形成する工程と、ゲート絶縁膜104上に金属膜107を形成する工程と、金属膜107上に金属シリコン化合物膜108を連続して堆積する工程と、金属シリコン化合物膜108上にシリコン膜110を形成する工程と、金属膜107、金属シリコン化合物膜108及びシリコン膜110を加工する工程と、を備える。

(もっと読む)

非対称型半導体デバイス及び製造方法

【課題】 非対称型半導体デバイス、及びその製造の際にスペーサ・スキームを用いる方法を提供する

【解決手段】 高kゲート誘電体の表面上に配置された非対称型ゲート・スタックを含む半構造体が提供される。非対称型ゲート・スタックは、第1の部分と第2の部分とを含み、第1の部分は、第2の部分とは異なる閾値電圧を有する。本発明の非対称型ゲート・スタックの第1の部分は、下から上に、閾値電圧調整材料及び少なくとも第1の導電性スペーサを含み、本発明の非対称型ゲート・スタックの第2の部分は、ゲート誘電体の上の少なくとも第2の導電性スペーサを含む。幾つかの実施形態において、第2の導電性スペーサは、下にある高kゲート誘電体と直接接触しており、他の実施形態においては、第1及び第2の導電性スペーサは、前記閾値電圧調整材料と直接接触している。

(もっと読む)

水素化ホウ素クラスターイオンの注入によるイオン注入装置及び半導体製造方法

【課題】イオン化チャンバ内の電子ビーム通路に均一な磁場を生成する磁場装置を提供する。

【解決手段】電子衝撃イオン源用の磁場装置において、イオン化チャンバ内の電子ビーム通路に均一な磁束線119を生成させるために、一対の永久磁石510A、510Bにより生成された磁束が、磁気ヨークアセンブリ500を経て、電子ビーム通過用の一対の整列した開口530A、530Bを有する磁極片520A、520Bの間の間隙を通って戻るようにする。

(もっと読む)

半導体装置の製造方法

【課題】短いゲート長を加工可能にする半導体装置の製造方法を提供すること。

【解決手段】半導体装置の製造方法の一形態は、シリコン基板2上にシリコン酸化膜34を形成し、酸化膜34上に所定幅T1を有する多結晶シリコン膜35aを形成し、少なくとも多結晶シリコン膜35aの両側部を酸化し、所定幅T1よりも狭い幅を有する酸化膜34の部分を多結晶シリコン膜35aの下に残すように、酸化膜34を、多結晶シリコン膜35aの酸化された部分と共にエッチングし、酸化された部分がエッチングされた多結晶シリコン膜35aをマスクとして、多結晶シリコン膜35aの両側のシリコン基板2の部分に不純物をイオン注入し、多結晶シリコン膜35aの両側に側壁絶縁膜14を形成し、側壁絶縁膜14が形成された多結晶シリコン膜35aをマスクとして、多結晶シリコン膜35aの両側のシリコン基板2の部分に不純物をイオン注入する、工程を有する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体装置全体としてみたとき、微細化によるチップ面積の減少を図りつつ、各素子に必要とされる特性を維持・向上させる。

【解決手段】半導体装置は、FinFET10と、FinFET10と同一のチップ上に設けられたPlanarFET20とを具備する。PlanarFETの第2ゲート絶縁層24は、FinFET10の第1ゲート絶縁層14よりも厚い。

(もっと読む)

半導体装置の製造方法

【課題】ソース、ドレインの低抵抗化及び寄生容量の低減化のための構造、所望のゲート長、ソース、ドレイン形状、柱状半導体の直径が得られるSGTの製造方法を提供する。

【解決手段】第1の平面状半導体層上に第1の柱状半導体層を形成する工程と、第1の柱状半導体層の下部と第1の平面状半導体層に第1の第2導電型半導体層を形成する工程と、第1の柱状半導体層の底部及び第1の平面状半導体層上に第1の絶縁膜を形成する工程と、第1の柱状半導体層の周囲にゲート絶縁膜およびゲート電極を形成する工程と、ゲート電極の上部且つ第1の柱状半導体層の上部側壁と、ゲート電極の側壁に第2の絶縁膜をサイドウォール状に形成する工程と、第1の第2導電型半導体層と第2の第2導電型半導体層との間に第1導電型半導体層を形成する工程と、第1の第2導電型半導体層の上部表面と、第2の第2導電型半導体層の上部表面に金属と半導体の化合物を形成する工程とを含む。

(もっと読む)

スレショルド電圧を有する電界効果トランジスタ、及びその製造方法

【課題】相異なるスレショルド電圧を有する電界効果トランジスタを提供する。

【解決手段】ドープ半導体ウエル上に、複数種のゲート・スタック(100〜600)が形成される。ドープ半導体ウエル(22、24)上に、高誘電率(high−k)ゲート誘電体(30L)が形成される。一つのデバイス領域中に金属ゲート層(42L)が形成され、他のデバイス領域(200、400、500、600)ではhigh−kゲート誘電体は露出される。該他のデバイス領域中に、相異なる厚さを有するスレショルド電圧調整酸化物層が形成される。次いで、スレショルド電圧調整酸化物層を覆って導電性ゲート材料層(72L)が形成される。電界効果トランジスタの一つの型は、high−kゲート誘電体部分を包含するゲート誘電体を包含する。電界効果トランジスタの他の型は、high−kゲート誘電体部分と、相異なる厚さを有する第一スレショルド電圧調整酸化物部分とを包含するゲート誘電体を包含する。相異なるゲート誘電体スタックと、同一のドーパント濃度を有するドープ半導体ウエルを用いることによって、相異なるスレショルド電圧を有する電界効果トランジスタが提供される。

(もっと読む)

201 - 220 / 883

[ Back to top ]