Fターム[5F140BG37]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極及び側壁の製造 (21,161) | ゲート電極の形成処理 (7,666) | ゲート電極の形状を形成する方法 (2,844) | エッチング (1,849)

Fターム[5F140BG37]の下位に属するFターム

ドライエッチング (966)

Fターム[5F140BG37]に分類される特許

121 - 140 / 883

半導体装置の製造方法

【課題】高誘電率絶縁膜を含むゲート絶縁膜を備えた電界効果型トランジスタにおいてゲート絶縁膜におけるゲート電極の端部下に位置する部分の厚膜化を試みると、高誘電率絶縁膜が結晶化し、ゲートトンネルリーク電流の発生を抑制出来ない場合があった。

【解決手段】半導体装置では、半導体基板1上にはゲート絶縁膜2が形成され、ゲート絶縁膜2上にはゲート電極3が形成されている。ゲート絶縁膜2では、ゲート絶縁膜2におけるゲート電極3の両端部下に位置する厚膜部分2aの膜厚は、ゲート絶縁膜2におけるゲート電極3の中央部下に位置する中央部分2bの膜厚よりも厚い。

(もっと読む)

半導体装置の製造方法

【課題】高耐電圧により大電流化が可能で、オン抵抗が低く高速動作が可能で、高集積化と省エネルギーが可能で、素子間分離の容易な、電気熱変換素子駆動用の半導体装置を提供する。

【解決手段】電気熱変換素子とそれに通電するためのスイッチング素子とがp型半導体基体1に集積化されている。スイッチング素子は、半導体基体1の表面に設けられたn型ウェル領域2と、それに隣接して設けられチャネル領域を提供するp型ベース領域6と、その表面側に設けられたn型ソース領域7と、n型ウェル領域2の表面側に設けられたn型ドレイン領域8,9と、チャネル領域上にゲート絶縁膜を介して設けられたゲート電極4とを有する絶縁ゲート型電界効果トランジスタである。ベース領域6は、ドレイン領域8,9を横方向に分離するように設けられた、ウェル領域2より不純物濃度の高い半導体からなる。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1の主面にゲート絶縁膜用のHf含有膜4、Al含有膜5及びマスク層6を形成してから、nチャネル型MISFET形成予定領域であるnMIS形成領域1Aのマスク層6とAl含有膜5を選択的に除去する。それから、nMIS形成領域1AのHf含有膜4上とpチャネル型MISFET形成予定領域であるpMIS形成領域1Bのマスク層6上に希土類含有膜7を形成し、熱処理を行って、nMIS形成領域1AのHf含有膜4を希土類含有膜7と反応させ、pMIS形成領域1BのHf含有膜4をAl含有膜5と反応させる。その後、未反応の希土類含有膜7とマスク層6を除去してから、メタルゲート電極を形成する。マスク層6は、窒化チタン又は窒化タンタルからなる窒化金属膜6aと、その上のチタン又はタンタルからなる金属膜6bとの積層構造を有する。

(もっと読む)

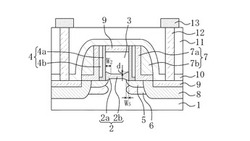

半導体装置およびその製造方法

【課題】pチャネル型の電界効果トランジスタのしきい値電圧を確実に制御して所望の特性が得られる半導体装置と、その製造方法とを提供する。

【解決手段】温度約700〜900℃のもとで施す熱処理に伴い、素子形成領域RPでは、アルミニウム(Al)膜7a中のアルミニウム(Al)がハフニウム酸窒化(HfON)膜6へ拡散することによって、ハフニウム酸窒化(HfON)膜6に元素としてアルミニウム(Al)が添加される。また、チタンアルミニウムナイトライド(TiAlN)膜からなるハードマスク8a中のアルミニウム(Al)とチタン(Ti)とがハフニウム酸窒化(HfON)膜6へ拡散することによって、ハフニウム酸窒化(HfON)膜6に元素としてアルミニウム(Al)とチタン(Ti)とが添加される。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化が進んだ場合であっても、適切なしきい値電圧を有するpチャネルMOSFETを含む半導体装置を製造する。

【解決手段】本発明に係る半導体装置の製造方法は、半導体基板101上に、SiO2またはSiONを含む第1ゲート絶縁層104を形成する第1ゲート絶縁層形成ステップと、第1ゲート絶縁層104上に、金属酸化物を含む第2ゲート絶縁層105を形成する第2ゲート絶縁層形成ステップと、第2ゲート絶縁層105上に、金属を含む第1電極106aを形成する第1電極形成ステップと、形成された積層構造に、複数回のミリセカンドアニール処理を行うことで、第2ゲート絶縁層105および第1電極106aの少なくとも一方に含まれる4族、5族または13族の元素を、第1ゲート絶縁層104と第2ゲート絶縁層105との界面に拡散させるアニールステップとを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、特性の安定したトランジスタを得ることが可能で、かつ複数の縦型トランジスタ間の特性のばらつきを抑制可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】半導体基板11の表面11aが部分的にエッチングされて形成され、縦壁面となる第1及び第2の側面26a,26bを含む内面によって区画された第2の溝26と、第2の溝26の第1及び第2の側面26a,26bを覆うゲート絶縁膜32と、ゲート絶縁膜32上に形成され、上端面37a,38aが半導体基板11の表面11aより低い位置にある第1の導電膜34、及び第1の導電膜34に形成され、上端面35aが第1の導電膜34の上端面34aより低い位置にある第2の導電膜35よりなるゲート電極33と、第2の溝26内に、半導体基板11の表面11aより低い位置に配置され、第2の導電膜35の上端面35aを覆う第1の絶縁膜17と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】キャップ材料を使用した半導体装置のウェハ面内における閾値電圧Vtのバラツキを抑制することを目的とする。

【解決手段】まず、半導体基板1001の上に、高誘電率ゲート絶縁膜1006及び第1のキャップ膜1008を順に形成する。次に、熱処理を行って、第1のキャップ膜1008中の第1の金属を高誘電体膜1006に拡散させる。その後、高誘電体膜1006に拡散せずに高誘電体膜1006の上に残存した第1のキャップ膜1008を除去して、第1の金属が拡散した高誘電率ゲート絶縁膜1006Aの上に金属電極1010を形成する。

(もっと読む)

半導体装置の製造方法

【課題】ダミーシリコンピラーを用いてゲート電極を延長する場合の、シリコンピラーにおける反り変形の発生を抑制する。

【解決手段】半導体装置の製造方法は、第1及び第2のシリコンピラー3,4の側周面3a,4aに形成されたゲート絶縁膜9を覆うゲート電極材料を成膜する工程を備え、ゲート電極材料の成膜量は、ゲート絶縁膜9を介して側周面3aを覆う第1の部分と、ゲート絶縁膜9を介して側周面4aを覆う第2の部分とが接触しないよう制御され、第1及び第2の部分を覆うとともに第1の部分と第2の部分の間の領域を埋めるマスク絶縁膜を形成する工程と、マスク絶縁膜をマスクとして用いてゲート電極材料をエッチングすることにより、ゲート絶縁膜9を介してそれぞれ側周面3a,4aを覆うゲート電極101,102と、ゲート電極101,102とを電気的に接続する導体膜11とを形成する工程とをさら備える。

(もっと読む)

半導体装置及びその製造方法

【課題】良好な電気的特性を有する半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10上に形成されたゲート絶縁膜20と、ゲート絶縁膜上に形成されたキャップ膜22と、キャップ膜上に形成されたシリコン酸化膜23と、シリコン酸化膜上に形成された金属ゲート電極24と、金属ゲート電極の両側の半導体基板内に形成されたソース/ドレイン拡散層48とを有している。

(もっと読む)

半導体装置の製造方法、及び半導体装置

【課題】電界効果トランジスタにおけるゲート電極の汚染を防止し、かつゲート電極上に形成されるマスク膜の膜厚を薄くする。

【解決手段】基板10上にゲート絶縁膜100を形成する。次いでゲート絶縁膜100上にゲート電極膜120を形成する。ゲート電極膜120の一部上にマスク膜230を形成する。マスク膜230をマスクとしたエッチングによりゲート電極膜120を選択的に除去する。そして、マスク膜230とゲート電極膜120の側面に接するようゲート側壁膜130を形成する。マスク膜230は少なくとも第1膜200、第2膜210、及び第3膜220をこの順に積層した積層膜により構成される。第2膜210は、ゲート側壁膜130に対して第3膜220よりも高いエッチング選択比を有する。第3膜220は、ゲート電極膜120に対して第2膜210よりも高いエッチング選択比を有する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】電界効果型トランジスタの閾値電圧を精度よく制御することができ、かつその範囲を広くする。

【解決手段】この半導体装置は、ゲート絶縁膜120及びゲート電極130を有する電界効果型トランジスタ101を備える。ゲート絶縁膜120は、界面層110と高誘電率膜112とを積層した構成を有している。高誘電率膜112は、酸化シリコンより誘電率が高い金属酸化物からなる。そしてゲート絶縁膜120は、高誘電率膜112と界面層110の界面近傍に、窒素を含有する窒素含有層を有している。窒素含有層は高誘電率膜112から界面層110に渡って形成されている。窒素含有層において、窒素の濃度は高誘電率膜112と界面層110の界面が最も高い。

(もっと読む)

半導体装置の製造方法、及び半導体装置

【課題】ゲート電極が金属窒化膜により構成されるMOSFETにおいて、電流駆動能力の向上を図る。

【解決手段】基板10に、素子形成領域20を分離する素子分離領域50を設ける。次に素子形成領域20上にゲート絶縁膜100を形成する。その後ゲート絶縁膜100上に金属窒化膜により構成される下部ゲート電極膜200を形成する。さらに下部ゲート電極膜200を熱処理する。そして下部ゲート電極膜200上に上部ゲート電極膜220を形成する。

(もっと読む)

半導体装置の製造方法

【課題】バラツキの小さな高特性、高信頼性の半導体装置の製造方法を提供する。

【解決手段】ゲート電極の側壁に窒化膜サイドウォールを形成し、ウエットエッチングにより、ソース・ドレイン形成予定領域上のゲート酸化膜を除去することにより、窒化膜サイドウォール下方にアンダーカットが入るが、ゲート電極下方にはアンダーカットは入らない。これにより、ソース・ドレインのシート抵抗ばらつき増大を抑制し、また、シリコン基板にダメージを導入してしまうこともないため、接合リーク、しきい値ばらつき等の不具合を引き起こすことがない。

(もっと読む)

電荷トラップを有するゲート誘電体を含む揮発性メモリ及びその製造方法

【課題】チャネルイオン注入領域のドーピング濃度を相対的に低下しながらも所望のしきい電圧値を得ることができる揮発性メモリを提供する。

【解決手段】ゲート誘電体として順次積層された下部ゲート誘電体、電荷トラップのための中間ゲート誘電体、及び上部ゲート誘電体を備えたセルトランジスタと、ゲート誘電体として単一層の酸化膜を備えたロジック用トランジスタとで、揮発性メモリを構成する。

(もっと読む)

半導体装置及びその製造方法

【課題】バイポーラトランジスタや縦型FET等の縦型デバイスを、絶縁膜マスクを用いた選択成長による、ボトムアップ構造にするすることで、精密な制御を要求される工程を削減できる製造方法を提供する。

【解決手段】導電性基板20の第1主表面上に、第1絶縁膜32、金属膜42及び第2絶縁膜52を順次に形成する。次に、第1絶縁膜、金属膜及び第2絶縁膜の、中央領域の部分を除去することにより、導電性基板を露出する成長用開口部70を形成する。次に、成長用開口部内に、半導体成長部82,84を形成する。次に、第2絶縁膜の、中央領域の周囲の周辺領域内に設けられた引出電極領域の部分72を除去することにより、金属膜を露出する引出電極用開口部を形成する。次に、引出電極用開口部内72に、引出電極90を形成する。次に、半導体成長部上及び導電性基板の第2主表面上にオーミック電極92を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】配線の信頼性の高い半導体装置を提供する。

【解決手段】半導体基板42上に台形状の凸部領域と台形状の凹部領域を設け、凹部領域のシリコン表面にはゲート酸化膜45が設けられ、ゲート酸化膜上にはゲート電極46が形成されている。凹部領域に設けられたゲート電極46の両側の凸部領域にはソース・ドレイン高濃度領域48が位置し、ソース・ドレイン高濃度領域48とゲート電極46の間にはソース・ドレイン低濃度領域47が形成されている。ソース・ドレイン高濃度領域48の上表面には第1層目の金属配線49と第2層目の金属配線50と第3層目の金属配線52が積層され、ソース・ドレイン高濃度領域48から第3金属配線までの接続にコンタクトホールやビアホールなどを利用していない。このように本発明の半導体装置は、コンタクトホールやビアホールなどの接続孔を形成しないで素子と配線との接続や配線間接続を行なうことができる。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極と第1のコンタクトプラグとが接触する接触幅を充分に確保する。

【解決手段】半導体基板10の上に、エッチングストッパー膜17、第1の層間絶縁膜18及び第2の層間絶縁膜19を順次形成する。次に、第1,第2の層間絶縁膜18,19を貫通し、且つ、エッチングストッパー膜17を露出する第1のホール23を形成する。次に、酸素ガスを含むプラズマを用いたプラズマ処理により、第2の層間絶縁膜19における第1のホール23の側壁に露出する部分を変質して、第1の変質層25を形成する。次に、第1の変質層25を除去して、第2のホール27を形成する。次に、エッチングストッパー膜17における第2のホール27に露出する部分を除去して、第1のコンタクトホール29を形成する。次に、第1のコンタクトホール29に、第1のコンタクトプラグ32Aを形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】初期故障や偶発故障の発生を低減する。

【解決手段】HFET1は、下層のGaN層13およびGaN層13の一部を露出させるトレンチT1が形成された上層のAlGaN層14よりなるIII族窒化物半導体層と、III族窒化物半導体層上に形成されたゲート絶縁膜15と、ゲート絶縁膜15上に形成されたゲート電極16と、を備える。少なくともゲート絶縁膜15と接触するトレンチT1底部のGaN層13上面には、原子層ステップが形成されている。原子層ステップのテラス幅の平均値は、0.2μm以上1μm未満である。

(もっと読む)

半導体装置およびその製造方法

【課題】特性を劣化させることなく、微細化することができる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、主表面を有する半導体基板SBと、主表面に互いに間隔をおいて形成されたソース領域SRおよびドレイン領域DRと、ソース領域SRとドレイン領域DRとに挟まれる主表面上に形成されたゲート電極層GEと、ソース領域SRの表面に接するように形成された第1導電層PL1と、ドレイン領域DRの表面に接するように形成された第2導電層PL2とを備え、第1導電層PL1とソース領域SRとの接触領域CR1からゲート電極層GEの下側を通って第2導電層PL2とドレイン領域DRとの接触領域CR2まで延びるように溝REが主表面に形成されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】ゲート電極に注入された不純物に起因するゲートリークを低減させる。

【解決手段】ゲート電極14が形成されたアクティブ領域による被覆率が50%以上かつその面積が0.02mm2以上の領域において、多結晶シリコン膜14´に炭素15を導入してから、多結晶シリコン膜14´にリン16を導入し、多結晶シリコン膜14´をパターニングすることにより、ゲート絶縁膜13上にゲート電極14を形成する。

(もっと読む)

121 - 140 / 883

[ Back to top ]