Fターム[5F140BG45]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極及び側壁の製造 (21,161) | ゲート電極形成後の処理 (1,641) | エッチング (876)

Fターム[5F140BG45]の下位に属するFターム

コンタクトホールの形成 (137)

Fターム[5F140BG45]に分類される特許

101 - 120 / 739

高kゲート誘電体のための、不純物酸素を捕捉する半導体構造および該構造を形成する方法(高kゲート誘電体のための捕捉金属スタック)

【課題】CMOS集積過程での高温処理の後であっても一定の閾値電圧を維持する高kゲート誘電体の提供。

【解決手段】高kゲート誘電体30と、下部金属層40、捕捉金属層50、および上部金属層60を含む金属ゲート構造とのスタックを提供する。該捕捉金属層は、次の2つの基準、1)Si+2/yMxOy→2x/yM+SiO2の反応によるギブス自由エネルギの変化が正である金属(M)であること、2)酸化物形成に対する酸素原子あたりのギブス自由エネルギが、下部金属層の金属および上部金属層の金属より大きな負である金属であること、を満たす。これらの基準を満たす捕捉金属層は、酸素原子がゲート電極を通って高kゲート誘電体に向け拡散するときに該酸素原子を捕捉する。さらに、該捕捉金属層は、高kゲート誘電体の下の酸化ケイ素界面層の厚さを遠隔から低減する。この結果、ゲート誘電体全体の等価酸化膜厚(EOT)の変動が抑制される。

(もっと読む)

半導体ウエハを処理するための方法

【課題】

【解決手段】半導体ウエハを処理するための方法であって:酸化ランタンまたは酸化ランタニド(例えば、Dy2O3、Pr2O3、Ce2O3)を含む層を準備する工程と;炭酸水である水溶液を供給することにより、酸化ランタンまたは酸化ランタニドを含む層を特定の領域で除去して、酸化ランタンまたは酸化ランタニドを含む層が上に蒸着された表面を露出させる工程とを備える方法が開示されている。

(もっと読む)

半導体装置及びその製造方法

【課題】p型ソースドレイン領域内にシリコン混晶層が形成されていると、N型MISトランジスタのキャリア移動度が低下する虞があった。

【解決手段】活性領域10aと活性領域10bとが素子分離領域11により分離されており、活性領域10a上には第1導電型の第1のトランジスタが設けられており、活性領域10b上には第2導電型の第2のトランジスタが設けられている。活性領域10b内には、第1の応力を有するシリコン混晶層21が設けられている。素子分離領域11のうち活性領域10aと活性領域10bとで挟まれた部分の上面には凹部22が設けられている。凹部23内には応力絶縁膜24が設けられており、応力絶縁膜24は第1の応力とは反対方向の第2の応力を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】PMISトランジスタのソースドレイン電極に高濃度のゲルマニウムを含むシリコンゲルマニウム層を用いても、シリコンゲルマニウム層に格子緩和を生じさせることなく、ソースドレイン電極の上部にシリコン層又は金属シリサイド層を形成できるようにする。

【解決手段】半導体装置は、n型半導体領域100の上にゲート絶縁膜101を介在させて形成されたゲート電極102と、その両側方に形成されたp型のソースドレイン電極150とを有している。ソースドレイン電極150は、n型半導体領域100に設けられた各リセス部100aに、その底部から少なくともチャネル領域の深さにまで形成されたシリコンゲルマニウム層111と、その上に形成され、炭素とシリコンゲルマニウム層のゲルマニウム濃度よりも低いゲルマニウムとを含むカーボンドープドシリコンゲルマニウム層112と、その上に形成された金属シリサイド層115とから構成される。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極中の不純物がゲート絶縁膜を突き抜けてチャネル領域に拡

散するのを抑制し、ソース・ドレイン領域の不純物イオンが部分的にチャネル領

域方向に異常拡散するのを防ぐ。

【解決手段】ゲート絶縁膜3上に、ポリシリコン膜4を被着してゲート電極5

パターンにパターンニングした後、ソース・ドレイン領域9を形成する前に、窒

素を含む雰囲気中で窒化処理を行って、ゲート電極5端部付近のゲート絶縁膜3

中に新たに窒素を導入する。または、ゲート電極5のパターンニング後、ソース

・ドレイン領域9を形成する前に、酸化処理を行うことによってゲート電極5の

パターンニングの際に生じるダメージや汚染の一部を酸化膜中に取り込んで基板

から除去する。その後、窒化処理を行うことにより、酸化処理によってゲート電

極5端部付近に形成され、ダメージを含む酸化膜に積極的に窒素を導入する。

(もっと読む)

半導体装置およびその製造方法

【課題】メタルゲート電極を有するpチャネル型電界効果トランジスタにおいて、所望するしきい値電圧を安定して得ることのできる技術を提供する。

【解決手段】半導体基板1上に形成されたHfSiON膜からなるゲート絶縁膜5h上に、Me−O−Al−O−Me結合を含むMe1−xAlxOy(0.2≦x≦0.75、0.2≦y≦1.5)組成の導電性膜を一部に有するメタルゲート電極6、またはMe−O−Al−N−Me結合を含むMe1−xAlxN1−zOz(0.2≦x≦0.75、0.1≦z≦0.9)組成の導電性膜を一部に有するメタルゲート電極6を形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】素子分離構造の面積を増大させることなく、素子分離構造の表面の後退量を低減させる。

【解決手段】半導体基板11の表面よりも低い位置に埋め込み絶縁層12を埋め込み、埋め込み絶縁層12と材料の異なるキャップ絶縁層13を半導体基板11と埋め込み絶縁層12と間の段差12aの肩の部分にかからないようにして埋め込み絶縁層12上に形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】基板上にヒューズ素子を備える半導体装置において、ヒューズを切断しやすくし、かつヒューズ切断状態を確実に得る。

【解決手段】半導体装置1は、基板10上に、MIPS構造を有するMOSトランジスタとヒューズ素子100を備える。ヒューズ素子100は、基板10の上に設けられた金属膜28と、金属膜28の上に設けられた絶縁膜30と、絶縁膜30の上に設けられたシリコン層34と、シリコン層34の上の少なくとも一部を覆うシリサイド層73と、からなる。

(もっと読む)

半導体装置の製造方法

【課題】所望のMOSトランジスタのみにチャネル領域に引っ張り応力を印加してキャリア移動度を向上させ、且つ、製造工程の複雑化を抑える。

【解決手段】シリコン基板10上にnMOSトランジスタのゲート絶縁膜13およびゲート電極14を非単結晶シリコンで形成し、ゲート電極14をマスクとして例えばAsやSb等の比較的質量数が大きい(質量数70以上)n型ドーパントを注入することで、nMOSトランジスタのソースドレイン領域を形成する。それにより、ゲート電極14は非晶質化する。そして、ゲート電極14が再結晶化する温度(約550℃)以下の温度条件でゲート電極14を覆うようにシリコン酸化膜40を形成し、その後1000℃程度の加熱処理を行う。それにより、ゲート電極14内に強い圧縮応力が残留すると共に、その下のチャネル領域には強い引っ張り応力が印加され、当該nMOSトランジスタのキャリア移動度は向上する。

(もっと読む)

半導体装置の製造方法

【課題】 トランジスタのスイッチング速度低下を防止することが可能な半導体装置の製造方法を提供する。

【解決手段】 本発明では、半導体基板100上にゲート絶縁膜104を形成する工程と、ゲート絶縁膜104上に金属膜107を形成する工程と、金属膜107上に金属シリコン化合物膜108を連続して堆積する工程と、金属シリコン化合物膜108上にシリコン膜110を形成する工程と、金属膜107、金属シリコン化合物膜108及びシリコン膜110を加工する工程と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】短いゲート長を加工可能にする半導体装置の製造方法を提供すること。

【解決手段】半導体装置の製造方法の一形態は、シリコン基板2上にシリコン酸化膜34を形成し、酸化膜34上に所定幅T1を有する多結晶シリコン膜35aを形成し、少なくとも多結晶シリコン膜35aの両側部を酸化し、所定幅T1よりも狭い幅を有する酸化膜34の部分を多結晶シリコン膜35aの下に残すように、酸化膜34を、多結晶シリコン膜35aの酸化された部分と共にエッチングし、酸化された部分がエッチングされた多結晶シリコン膜35aをマスクとして、多結晶シリコン膜35aの両側のシリコン基板2の部分に不純物をイオン注入し、多結晶シリコン膜35aの両側に側壁絶縁膜14を形成し、側壁絶縁膜14が形成された多結晶シリコン膜35aをマスクとして、多結晶シリコン膜35aの両側のシリコン基板2の部分に不純物をイオン注入する、工程を有する。

(もっと読む)

半導体装置の製造方法

【課題】ソース、ドレインの低抵抗化及び寄生容量の低減化のための構造、所望のゲート長、ソース、ドレイン形状、柱状半導体の直径が得られるSGTの製造方法を提供する。

【解決手段】第1の平面状半導体層上に第1の柱状半導体層を形成する工程と、第1の柱状半導体層の下部と第1の平面状半導体層に第1の第2導電型半導体層を形成する工程と、第1の柱状半導体層の底部及び第1の平面状半導体層上に第1の絶縁膜を形成する工程と、第1の柱状半導体層の周囲にゲート絶縁膜およびゲート電極を形成する工程と、ゲート電極の上部且つ第1の柱状半導体層の上部側壁と、ゲート電極の側壁に第2の絶縁膜をサイドウォール状に形成する工程と、第1の第2導電型半導体層と第2の第2導電型半導体層との間に第1導電型半導体層を形成する工程と、第1の第2導電型半導体層の上部表面と、第2の第2導電型半導体層の上部表面に金属と半導体の化合物を形成する工程とを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】耐熱性に優れたシリサイド層をソース・ドレイン領域に有するp型MOSFETを備える半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、半導体基板2上にゲート絶縁膜11を介して形成されたゲート電極12と、半導体基板2上のゲート電極12の両側に形成されたエレベーテッド層15と、エレベーテッド層15上に形成されたSi:C16層と、半導体基板2、エレベーテッド層15、およびSi:C16内のゲート電極12の両側に形成されたp型のソース・ドレイン領域19と、Si:C層16上に形成されたシリサイド層17と、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】MIPS構造を有する電界効果トランジスタにおいて、金属ゲート電極とポリシリコンゲート電極との接触抵抗を低減することにより、AC動作を向上させる。

【解決手段】半導体装置1は、半導体基板10上に電界効果トランジスタを有する。電界効果トランジスタは、ゲート絶縁膜25、27とゲート電極63、71と、を備える。さらに、ゲート電極63、71は第1金属からなる第1電極層22と、第2金属からなる第2電極層26、34と、シリコン層からなる第3電極層62、70と、を含む積層構造である。第2金属は、シリコン層の多数キャリアに対する第1電極層22と第3電極層62、70とのバンド不連続を緩和する仕事関数を有する材料である。

(もっと読む)

半導体装置

【課題】SiGeのチャネルを有する半導体装置の高性能化及び高信頼化をはかる。

【解決手段】シリコンを主成分とする半導体基板101の一主面に設けられ、素子分離絶縁膜102によって区画された素子形成領域103と、チャネル領域となるSi及びGeを主成分とし素子形成領域103上に設けられた半導体膜104と、半導体膜104上にゲート絶縁膜105を介して設けられたゲート電極106と、チャネル領域を挟んで半導体膜104及び基板101に形成されS/D領域110と、ゲート電極106の両側面に設けられた側壁絶縁膜109と、S/D領域110上の側壁絶縁膜109で区画されたS/Dコンタクト領域上に半導体膜104と金属との反応により形成され、且つS/Dコンタクト領域以外の半導体膜104よりも薄い膜厚に形成された金属化合物膜111とを備えた。

(もっと読む)

半導体装置の製造方法

【課題】

製造工程を簡略化しつつ、特性の優れた第1のMOSトランジスタと第2のMOSトランジスタとを製造する半導体装置の製造方法を提供する。

【解決手段】

半導体基板に、第1のMOSトランジスタ領域、第2のMOSトランジスタ領域を画定する素子分離領域を形成し、第1のMOSトランジスタ領域、第2のMOSトランジスタ領域に第1導電型の不純物をイオン注入し、第1導電型のウェルを形成し、第1のMOSトランジスタ領域、第2のMOSトランジスタ領域上に絶縁ゲート電極を形成し、第2のMOSトランジスタのドレイン領域を覆うマスクを介して、半導体基板法線方向から傾いた複数方向から第1導電型の不純物をイオン注入し、第1のMOSトランジスタ領域の前記絶縁ゲート電極下方に対称的なチャネルドーズ領域、第2のMOSトランジスタ領域の前記絶縁ゲート電極下方に非対称なチャネルドーズ領域を形成し、半導体装置を製造する。

(もっと読む)

ソース/ドレインゾーンに沿って調節したポケット部分を具備する非対称的電界効果トランジスタを有する半導体構成体の構成及び製造

【課題】 半導体ボディの上部表面に沿って設けられている非対称的絶縁ゲート電界効果トランジスタ(100U又は102U)は、該トランジスタボディ物質のチャンネルゾーン(244又は284)によって横方向に分離された第1及び第2ソース/ドレインゾーン(240及び242又は280及び282)を包含している。

【解決手段】 ゲート電極(262又は302)がチャンネルゾーン上方でゲート誘電体層(260又は300)の上側に位置している。該ボディ物質の横方向に隣接した物質よりも一層高度にドープした該ボディ物質のポケット部分(250又は290)が該S/Dゾーンの内のほぼ第1のもののみに沿って該チャンネルゾーン内に延在している。該ポケット部分の垂直ドーパント分布は、互いに離隔されている夫々の位置(PH−1乃至PH−3)において複数個の局所的最大(316−1乃至316−3)に到達すべく調節されている。該調節は、典型的に、該ポケット部分の垂直方向ドーパント分布が上部半導体表面近くで比較的平坦であるように実施される。その結果、該トランジスタのリーク電流は減少されている。

(もっと読む)

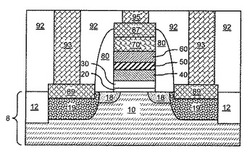

L形状スペーサを使用した非対称的電界効果トランジスタの製造及び構成体

【課題】 非対称的電界効果トランジスタ(102)の製造は、半導体ボディのボディ物質のチャンネルゾーン(284)の上方でそれからゲート誘電体層(300)によって垂直方向に分離されているゲート電極(302)を画定することとなる。

【解決手段】 該ゲート電極をドーパント阻止用シールドとして使用して、半導体ドーパントを該ボディ物質内に導入させて、一層高度にドープしたポケット部分(290)を画定する。該ゲート電極に沿ってスペーサ(304T)を設ける。該スペーサは、(i)該ゲート電極に沿って位置されている誘電体部分、(ii)該半導体ボディに沿って位置されている誘電体部分、及び(iii)該他の2つのスペーサ部分の間の空間をほぼ占有するフィラー部分(SC)、を包含している。該ゲート電極及び該スペーサをドーパント阻止用シールドとして使用して、半導体ドーパントを該半導体ボディ内に導入させて、一対のソース/ドレイン部分(280M及び282M)を画定する。該フィラースペーサ部分を除去して該スペーサをL形状(304)へ変換させる。一対の電気的コンタクト(310及び312)を夫々該主要ソース/ドレイン部分に対して形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】シェアードコンタクト形成時に、ゲート電極が溶解されて形状異常となるのを防止する。

【解決手段】半導体装置は、基板1上にゲート絶縁膜2を介して形成されたゲート電極31と、基板1のゲート電極31の両側方に形成された不純物領域32及び33とを有するトランジスタと、トランジスタ上を覆うように基板1上に形成された層間絶縁膜11及び12と、不純物領域32及び33及びゲート電極31に電気的に接続するシェアードコンタクト14とを備える。ゲート電極31の側面下部を覆うように第1のサイドウォール5、第1のサイドウォール5におけるゲート電極31とは反対側に第2のサイドウォール6、第1のサイドウォール5上に、ゲート電極31の側面上部と第2のサイドウォール6とに挟まれるように第3のサイドウォール9bが形成されている。第2及び第3のサイドウォール6及び9bは、第1のサイドウォール5とは異なる材料からなる。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1に形成したnチャネル型MISFETQnのソース・ドレイン用のn+型半導体領域7bおよびゲート電極GE1上と、pチャネル型MISFETQpのソース・ドレイン用のp+型半導体領域8bおよびゲート電極GE2上とに、ニッケル白金シリサイドからなる金属シリサイド層13bをサリサイドプロセスで形成する。その後、半導体基板1全面上に引張応力膜TSL1を形成してから、pチャネル型MISFETQp上の引張応力膜TSL1をドライエッチングで除去し、半導体基板1全面上に圧縮応力膜CSL1を形成してからnチャネル型MISFETQn上の圧縮応力膜CSL1をドライエッチングで除去する。金属シリサイド層13bにおけるPt濃度は、表面が最も高く、表面から深い位置になるほど低くなっている。

(もっと読む)

101 - 120 / 739

[ Back to top ]