Fターム[5F140BG58]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極及び側壁の製造 (21,161) | エッチングレートの差の利用 (194)

Fターム[5F140BG58]に分類される特許

1 - 20 / 194

半導体装置の製造方法

【課題】第1の領域において、第2の絶縁膜からゲート絶縁膜への酸化剤の侵入を防止する。第2の領域において、複数の第1の配線間に設けられた第2の絶縁膜を第1の絶縁膜に対して選択的に除去する。

【解決手段】半導体装置の製造方法では、基板の第1の領域には第1の積層体を形成し第2の領域には複数の第1の配線を形成する。第1の絶縁膜をマスクとして、第1の領域の主面に第1の不純物のイオン注入を施す。第1の積層体の側壁を覆いかつ複数の第1の配線間を埋設するように第2の絶縁膜を形成する。第2の絶縁膜をマスクとして、第1の領域の主面に第2の不純物のイオン注入を施す。第1のエッチングにより、第2の絶縁膜を第1の絶縁膜に対して選択的に除去した後、基板に熱処理を行う。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の高い半導体装置を製造する。

【解決手段】半導体装置の製造方法は、半導体基板50上に絶縁膜を形成する工程と、絶縁膜上に、ゲート電極20およびハードマスク34を順に積層してなる積層体10を形成する工程と、積層体10をマスクとして、半導体基板50にイオン注入を行う工程と、積層体10の側面上に保護膜44を形成する工程と、エッチングによりハードマスク34を除去する工程と、エッチングにより保護膜44を除去する工程と、を備える。

(もっと読む)

半導体デバイスのための非対称スペーサ構造体を形成する方法

【課題】 デバイスのゲートとソースとの間の低い直列抵抗を維持し、同時に、ゲートからドレインへの過剰なオーバーラップによって形成される悪影響を最小限にするFETデバイスの製造を可能にする。

【解決手段】半導体基板の上に少なくとも1対の隣接して離間配置された、オフセット・スペーサ114を備えるゲート構造体102の上にスペーサ層132を形成するステップであって、ゲート構造体は、スペーサ層がゲート構造体間の領域で第1の厚さで形成され、その他の場所で第2の厚さで形成されるように離間配置され、第2の厚さは第1の厚さより厚い、ステップと、1対の隣接して離間配置されたゲート構造体のオフセット・スペーサに隣接して非対称スペーサ構造体124a、bを形成するようにスペーサ層をエッチングするステップとを含み、非対称スペーサ構造体は、ソース及びドレイン領域の画定において用いられる。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクトホールの一部が素子分離領域上に配置された構造の半導体装置において、短絡及び接合漏れ電流の増大を抑制する。

【解決手段】半導体装置50は、半導体基板10における活性領域10aを取り囲むように形成された溝15bに素子分離絶縁膜15aが埋め込まれた素子分離領域15と、活性領域10aに形成された不純物領域26と、半導体基板10上を覆う層間絶縁膜28と、層間絶縁膜28を貫通し、活性領域10a上及び素子分離領域15上に跨って形成されたコンタクトプラグ34と、少なくともコンタクトプラグ34下方において、不純物領域26上に形成された金属シリサイド膜33とを備える。素子分離領域15は、コンタクトプラグ34の下方において、素子分離絶縁膜15と活性領域10aとの間に設けられた保護絶縁膜35を更に有する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】ゲート電極の側壁側にサイドウォールを精度よく形成することが可能な半導体装置の製造方法及び半導体装置を提供することを目的とする。

【解決手段】まず、SOI基板5の一方面側においてゲート電極34上及びゲート電極34の周囲の領域に第1絶縁膜40を形成する。次に、第1絶縁膜40上に積層させる構成で第1絶縁膜40とは材質の異なる第2絶縁膜42を形成する。そして、第1絶縁膜40及び第2絶縁膜42におけるゲート電極34の側壁34a側の部分を残しつつ、第2絶縁膜42よりも第1絶縁膜40のほうが、エッチング速度が遅くなるように第1絶縁膜40及び第2絶縁膜42を除去し、ゲート電極34の側壁34a側にサイドウォール45を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】歩留まりに優れた半導体装置を提供する。

【解決手段】ゲート電極140は素子形成領域104に形成されている。サイドウォール層160は、ゲート電極140の側壁を覆っている。拡散領域170は素子形成領域104に位置する基板100に形成され、トランジスタ110のソース及びドレインとなる。絶縁層200は、素子形成領域104上、及びゲート電極140上に形成されている。コンタクト210は絶縁層200に形成され、拡散領域170に接続している。ゲート電極140のうちコンタクト210と隣に位置する部分は、サイドウォール層160より低く形成されている。絶縁層200は、ゲート電極140のうちコンタクト210と隣に位置する部分上かつ、サイドウォール層160同士の間に形成されている間隙に埋設される。

(もっと読む)

半導体装置の製造方法

【課題】高集積化を図ることができる半導体装置の製造方法を提供することである。

【解決手段】実施形態に係る半導体装置の製造方法は、半導体基板に第1の方向に延びる複数の溝を形成する工程と、前記溝の内面上及び前記半導体基板の上面上に絶縁膜を形成する工程と、前記絶縁膜上に、前記溝を埋めるように、第1の導電層を堆積する工程と、前記第1の導電層上に第2の導電層を堆積する工程と、前記第2の導電層上における前記溝の直上域の一部を含む領域にハードマスクを形成する工程と、前記ハードマスクをマスクとして前記第2の導電層をエッチングすることにより、前記ハードマスク及び前記第2の導電層を含む柱状体を形成する工程と、前記柱状体における前記溝の幅方向に面する2つの側面上に、電極加工側壁を形成する工程と、前記柱状体及び前記電極加工側壁をマスクとしてエッチングすることにより、前記第1の導電層における露出した部分の上部を除去し下部を残留させる工程と、前記電極加工側壁を除去する工程とを備える。

(もっと読む)

トンネルトランジスタの製造方法

【課題】1回のリソグラフィ工程によりセルフアラインでトンネルトランジスタを製造する方法を提供する。

【解決手段】ゲート絶縁膜及びゲート電極が積層された半導体基板上に第1の絶縁膜を形成しリソグラフィにより第1の絶縁膜の端部に第1の絶縁膜とは薬品選択性が異なりゲート電極位置を画定する第2の絶縁膜を形成する工程と、第1及び第2の絶縁膜をマスクにゲート電極の一端を画定する工程と、第1及び第2の絶縁膜をマスクにして第1導電型不純物を半導体基板に導入しソースを形成する工程と、半導体基板全面に第1の絶縁膜とは薬品選択性が異なる第3の絶縁膜を被覆する工程と、該第3の絶縁膜の一部を除去することにより該第1の絶縁膜を選択的に除去する工程と、第2及び第3の絶縁膜をマスクにしてゲート電極を形成した後、第2導電型不純物を半導体基板に導入しドレインを形成する工程を含むトンネルトランジスタの製造方法。

(もっと読む)

トランジスタ及びその製造方法

【課題】駆動電流を向上したnMOSトランジスタを備えた半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板の素子領域101の上にゲート絶縁膜111を介在させて形成されたゲート電極112と、素子領域101におけるゲート電極112の両側方に形成され、n型不純物及び炭素を含むソースドレイン領域122とを備えている。ソースドレイン領域122を構成するシリコン及びソースドレイン領域122に含まれる炭素の少なくとも一方は、主同位体よりも質量数が大きい安定同位体の存在比が、天然存在比よりも高い。

(もっと読む)

金属ゲート電極を有する半導体素子の製造方法

【課題】 収率が低下することなくCMOS集積回路の特性を最適可能な半導体素子の製造方法を提供する。

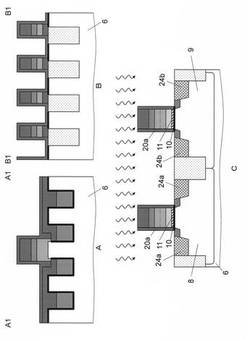

【解決手段】 半導体基板1の上の第1領域A内及び第2領域B内に各々形成された第1グルーブ15a及び第2グルーブ15bを有する層間絶縁膜15を形成する。次に、半導体基板1上に積層金属膜22を形成し、積層金属膜22上に非感光性を有する平坦化膜23を第1グルーブ15a及び第2グルーブ15bを充填するように形成する。第1領域A内の平坦化膜23を乾式エッチングによって選択的に除去し、第1領域A内の積層金属膜22を露出させ、第2領域B内の積層金属膜22を覆う平坦化膜パターン23pを形成する。これにより、第1領域A内の最上部金属膜を容易に除去することができるので、収率が低下することなく異なる仕事関数を有する第1金属ゲート電極及び第2金属ゲート電極を形成できる。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板の主面上の洗浄効果を低下させることなく、電界効果トランジスタのゲート電極の側面上に形成されたオフセットスペーサ膜の除去を抑制する。

【解決手段】ゲート電極部Gn,Gpを覆うように、半導体基板1の主面上に薬液に対するエッチング速度が互いに異なる第1OSS膜10および第2OSS膜12を順次形成した後、異方性エッチングにより、ゲート電極部Gn,Gpの側面上に位置する第2OSS膜12を残して、他の部分に位置する第2OSS膜12を除去する。そして、ゲート電極部Gn,Gpと、ゲート電極部Gn,Gpの側面上に位置する第1OSS膜10および第2OSS膜12と、をマスクにして、半導体基板1に不純物をイオン注入した後、半導体基板1を薬液により洗浄して、露出している第1OSS膜10を除去する。

(もっと読む)

半導体装置の製造方法

【課題】フラッシュメモリセルと低電圧動作トランジスタや高電圧動作トランジスタを集積化し、異種トランジスタを混載する半導体装置の製造法を提供する。

【解決手段】半導体装置の製造方法は、(a)トンネル絶縁膜、Fゲート電極膜、電極間絶縁膜を堆積したFゲート電極構造を形成し(b)ゲート絶縁膜を形成し(c)導電膜、エッチストッパ膜を堆積し(d)エッチストッパ膜、導電膜をエッチングした積層ゲート電極構造を形成し(e)積層ゲート電極構造の側壁上に第1絶縁膜を形成し(f)積層ゲート電極側壁上に第1サイドウォールスペーサ層を形成し(g)エッチストッパ層を除去し(h)他の領域の導電層から、ゲート電極構造を形成し(i)積層ゲート電極構造、ゲート電極構造側壁上に第2サイドウォールスペーサを形成し(j)希弗酸水溶液で半導体基板表面を露出し(k)半導体基板表面にシリサイド層を形成する。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極上のキャップ膜が厚く、隣接するトランジスタ間の空間のアスペクト比が大きいトランジスタに、適切な濃度プロファイルを有するハロー領域を形成することのできる半導体装置の製造方法を提供する。

【解決手段】一実施の形態による半導体装置の製造方法は、基板上に第1および第2のゲート電極を形成する工程と、前記第1および第2のゲート電極下に第1および第2のハロー領域をそれぞれ形成する工程と、前記第1および第2の絶縁膜に底面および側面をそれぞれ覆われた第1および第2のキャップ膜を形成する工程と、を含む。前記第1のハロー領域は、第1の不純物を、前記第2の絶縁膜を貫通させて前記基板に打ち込むことにより形成される。前記第2のハロー領域は、第2の不純物を、前記第1の絶縁膜を貫通させて前記基板に打ち込むことにより形成される。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、ゲート絶縁膜の一方の側のみに、容易に、かつ精度良く、バーズビークを形成可能な半導体装置の製造方法を提供することを課題とする。

【解決手段】斜めイオン注入により、マスク膜にイオンを注入することで、シリコン酸化膜及びシリコン窒化膜を介して、ゲート絶縁膜の第1の側面と第1の不純物拡散領域の上面とで構成される角部に形成されたマスク膜のエッチング速度を、他の部分に形成されたマスク膜よりも速くし、次いで、ウエットエッチングにより、角部に形成されたマスク膜を選択的に除去して、シリコン窒化膜の表面の一部を露出させ、次いで、ウエットエッチングにより、マスク膜から露出されたシリコン窒化膜を選択的に除去して、シリコン酸化膜の表面の一部を露出させ、その後、熱酸化法により、ゲート絶縁膜の第1の側面側にバーズビークを形成する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】導電材料のゲートトレンチへの埋め込みが容易な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上の絶縁膜と、絶縁膜に設けられた凹部と、凹部の底部であって半導体基板上に設けられたゲート絶縁膜とを形成する工程と、凹部の内壁面上と絶縁膜の上面上に、第1金属を含む導電材料で第1ゲート電極膜を形成する工程と、第1ゲート電極膜上に、凹部の側面部分の一部は覆わないように、導電材料の融点よりも高い融点を持つ材料でカバー膜を形成する工程と、カバー膜が形成された状態で、熱処理を行って、第1ゲート電極膜をリフローさせる工程とを有する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】縦型のトランジスタにおいてゲートからシリサイドの位置を精度よく制御できるようにする。

【解決手段】柱状半導体14の中央部には、その周囲を囲むように、ゲート絶縁膜9が形成され、さらに、ゲート絶縁膜9の周囲を囲むように、ゲート層6が形成されている。この柱状半導体14の中央部、ゲート絶縁膜9、ゲート層6により、MIS構造が形成されている。ゲート層6の上下には、第1絶縁膜4が形成されている。第1絶縁膜4は、柱状半導体14にも接している。柱状半導体14の側面には、シリサイド18及びn型拡散層(不純物領域)19が形成されている。シリサイド18は、第1絶縁膜4によってセルフ・アラインされた位置に形成されている。

(もっと読む)

半導体装置の製造方法、及び半導体装置

【課題】電界効果トランジスタにおけるゲート電極の汚染を防止し、かつゲート電極上に形成されるマスク膜の膜厚を薄くする。

【解決手段】基板10上にゲート絶縁膜100を形成する。次いでゲート絶縁膜100上にゲート電極膜120を形成する。ゲート電極膜120の一部上にマスク膜230を形成する。マスク膜230をマスクとしたエッチングによりゲート電極膜120を選択的に除去する。そして、マスク膜230とゲート電極膜120の側面に接するようゲート側壁膜130を形成する。マスク膜230は少なくとも第1膜200、第2膜210、及び第3膜220をこの順に積層した積層膜により構成される。第2膜210は、ゲート側壁膜130に対して第3膜220よりも高いエッチング選択比を有する。第3膜220は、ゲート電極膜120に対して第2膜210よりも高いエッチング選択比を有する。

(もっと読む)

半導体装置の製造方法

【課題】ポリシリコンゲート電極の意図しないフルシリサイド化を防止する。

【解決手段】基板17上に、ゲート絶縁膜12およびシリコン層10をこの順に積層した積層体(10、12)を形成する工程と、積層体(10、12)の側壁沿いにSiN膜を有するオフセットスペーサ13を形成する工程と、その後、シリコン層10の上面を、薬液を用いて洗浄する工程と、その後、少なくともシリコン層10の上面を覆う金属膜19を形成する工程と、その後、加熱する工程と、を有し、オフセットスペーサ13が有するSiN膜は、ALD法を用いて450℃以上で成膜されたSiN膜、または、1Gpa以上の引張/圧縮応力を有するSiN膜であり、前記薬液は、重量比率で、HF/H2O=1/100以上であるDHF、または、バッファードフッ酸である半導体装置の製造方法を提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】バリアメタルの膜厚を抑制しながらメタルゲートの拡散性材料が高誘電率誘電体に拡散することを防ぐ。

【解決手段】半導体装置がゲート積層体構造を含む。ゲート積層体構造は、半導体基板5の上に形成された界面層4と、界面層4の上に形成された高誘電率誘電体3と、拡散性材料と不純物金属を含み、高誘電率誘電体の上方に形成されたシリサイドゲート1と、拡散性材料に対するバリア効果を持ち、高誘電率誘電体3とシリサイドゲート1の間に形成されたバリアメタル2とを備えている。不純物金属は、シリサイドゲート1の拡散性材料が高誘電率誘電体に導入されることを防ぐことができるような、拡散性材料に対するバリア効果を有している。

(もっと読む)

マルチフィン高さを有するFinFET

【課題】マルチフィン高さを有するFinFETを提供する。

【解決手段】集積回路構造は、半導体基板と、半導体基板上のFinFETと、を含む。FinFETは、半導体フィンと、半導体フィンの頂面および側壁上のゲート誘電体と、ゲート誘電体上のゲート電極と、半導体フィン一端に位置するソース/ドレイン領域と、を備える。一対の第一STI領域は、ソース/ドレイン領域の一部分の真下に位置する部分を含み、一対の第一STI領域は、半導体ストリップにより分離され、且つ、半導体ストリップに隣接する。一対の第一STI領域は、更に、第一頂面を有する。一対の第二STI領域は、ゲート電極の真下に位置する部分を含み、一対の第二STI領域は、半導体ストリップにより互いに分離され、且つ、半導体ストリップに隣接する。第二STI領域は、第一頂面より高い第二頂面を有する。

(もっと読む)

1 - 20 / 194

[ Back to top ]