Fターム[5F140BH05]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース、ドレイン領域及びSD近傍領域 (10,828) | 形状、配置 (1,748) | 断面形状 (1,038)

Fターム[5F140BH05]の下位に属するFターム

せり上げSD (488)

せり下げSD(エッチングしているもの) (276)

Fターム[5F140BH05]に分類される特許

101 - 120 / 274

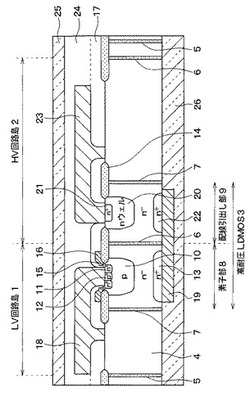

半導体装置

【課題】層間絶縁膜を厚くしなくてもソース配線の外にドレイン配線を引き出せ、かつ、LOCOS酸化膜や層間絶縁膜などの絶縁膜の絶縁破壊を防止できるようにする。

【解決手段】素子部8から配線引出し部9に延設されるようにn-型ドリフト層4の裏面に裏面電極19を備え、この裏面電極19とソース配線18との間に電流が流れるような構造、つまりn-型ドリフト層4の表裏を貫通して縦方向に電流を流す構造にする。そして、裏面電極19を配線引出し部9まで延設し、n+型コンタクト領域21、配線引出し部9のn-型ドリフト層4、nウェル領域20およびn+型コンタクト領域21を通じてドレイン配線23と接続する。すなわち、裏面電極19を通じて電流が流れるようにすることにより、ドレイン配線23を素子部8の外に引き出した構造とする。

(もっと読む)

横型MOSトランジスタ及びその製造方法

【課題】Locos酸化膜のソース電極側での耐圧特性における電界集中を緩和した横型MOSトランジスタ及びその製造方法を提供することを課題とする。

【解決手段】

横型MOSトランジスタは、基板100、n−活性層101、n−ドリフト層101a、Locos酸化膜102、n−ウェル領域103、p−ボディ拡散層104、ゲート酸化層105、ゲートポリサイド電極106、n+ドレイン領域107、n+ソース領域108、p+基板電極109、及びp+拡散層110を備える。p+拡散層110は、Locos酸化層102のソース領域側の第1端部102aに隣接する領域に形成され、n−活性層101とは導電型が逆の不純物が注入される。これにより、第1端部102a付近に生じる過剰なキャリアが打ち消され、キャリア濃度を最適化され、第1端部102a付近における耐圧特性が緩和される。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】p型MISFETまたはn型MISEFETを有する半導体装置において、p型MISFETまたはn型MISEFETのソース/ドレイン電極界面抵抗を低減する半導体装置およびその製造方法を提供する。

【解決手段】半導体基板100にp型MISFET200を備える半導体装置であって、p型MISFET200が、半導体基板100中のチャネル領域204と、チャネル領域204上に形成されたゲート絶縁膜206と、ゲート絶縁膜206上に形成されたゲート電極208と、チャネル領域204の両側の、Niを含有するシリサイド層210で形成されたソース/ドレイン電極と、ソース/ドレイン電極と半導体基板100との界面の半導体基板100側に形成された、Mg、CaまたはBaを含有する界面層230を有することを特徴とする半導体装置およびその製造方法。

(もっと読む)

横型MOSトランジスタ及びその製造方法

【課題】製造工程を追加せずに作製可能で、Locos酸化膜のソース電極側の電界集中を緩和した横型MOSトランジスタ及びその製造方法を提供することを課題とする。

【解決手段】

横型MOSトランジスタは、基板100、活性層101、Locos酸化膜102、拡散層103、104、105、ゲート酸化層106、ドレイン領域107、ソース領域108、ボディ拡散層109、ゲートポリサイド電極110を備える。Locos酸化層102は、第1領域102aと第2領域102bとを含む。第1領域102aには拡散工程が重複して行われ、第2領域102bよりも不純物濃度が高くされる。犠牲酸化膜のエッチング工程で第1領域102aと第2領域102bもエッチングされ、第1領域102aは第2領域102bよりも薄くされる。これにより、Locos酸化層102のソース領域108に近い側での電界強度分布が緩和される。

(もっと読む)

半導体装置及びその製造方法

【課題】所望の厚さで制御良くエピタキシャル成長され、良好な特性を示すシリコン混晶層を備えた半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、半導体基板10内に形成された素子分離領域11aと、素子分離領域11aに囲まれた半導体基板10からなり、トレンチ部を有する活性領域と、活性領域上に形成されたゲート電極13、ゲート電極13の側面上であって、平面的に見てゲート電極13とトレンチ部との間に形成された第1のサイドウォール19、及びトレンチ部内に充填された第1導電型のシリコン混晶層21を有する第1導電型のMISトランジスタと、トレンチ部と素子分離領域11a、11bとの間に設けられ、半導体基板10からなる基板領域と、基板領域に形成された第1導電型の不純物領域22とを備えている。シリコン混晶層21は、活性領域のチャネル領域に対して応力を生じさせる。

(もっと読む)

GaN系半導体装置及びその製造方法

【課題】ボンディングパッドを減らして、素子サイズの小型化を可能にし、かつ、アバランシェ破壊を抑制して信頼性の向上を図ったGaN系半導体装置及びその製造方法を提供する。

【解決手段】GaN系半導体装置20は、オン状態で能動層25を介して相互間に電流が流れるソース電極31およびドレイン電極32と、ゲート電極33と、裏面電極34とを備える。能動層25におけるソース電極31を形成する部分に、能動層25の表面側からシリコン基板21に達する深さの溝27が形成されている。溝27内には、能動層25の表面とシリコン基板21とを電気的に接続するソース電極31と、ソース電極31の溝27内の部分を能動層25に対して絶縁する絶縁層70とが形成されている。溝27内に、ソース電極31と絶縁層70を形成しているため、溝27および絶縁膜70の形成が容易になる。

(もっと読む)

半導体装置及びその製造方法

【課題】不純物の注入量及びチャネル領域中の不純物濃度を容易に制御する。動作特性に優れたFin型電界効果型トランジスタを備えた半導体装置を提供する。

【解決手段】Fin状の半導体基板の部分に犠牲酸化膜を形成した後、マスクパターンをマスクに用いて半導体基板に不純物を注入する。この後、犠牲酸化膜を除去して、半導体基板を露出させた後、露出した半導体基板上にゲート絶縁膜を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】 装置規模の拡大を最小限に抑制しながら、高い耐圧性を維持するとともに、現実的な製造プロセスの下で容易に製造が可能な半導体装置を提供する。

【解決手段】 第1絶縁膜3aを貫通するように基板面に直交する深さ方向に形成される導電膜14aと、第2絶縁膜3bの直上層から底面に達するまで一の外側壁に沿って深さ方向に形成される導電膜14bと、導電膜14bの底面の深さ位置から絶縁膜3a及び3bに挟まれた領域に係る基板2の上面位置に亘って、少なくとも導電膜14bの底面及び絶縁膜3bと接触していない側の外側壁と接触して形成される絶縁膜13bと、絶縁膜13bと3bに挟まれた領域内において底面から上面に向かって、第1導電型の第1不純物拡散領域6、第2導電型の第2不純物拡散領域5a、第1導電型の第3不純物拡散領域7、及び高濃度の前記第1導電型の第4不純物拡散領域17bを備える。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極周辺の基板に生じるエッチングによる基板掘れを低減又は解消し、短チャネル効果を抑制しうる半導体装置の製造方法を提供することにある。

【解決手段】シリコン基板10上にゲート絶縁膜12を介してゲート電極14を形成する工程と、シリコン基板10上及びゲート電極14上に、シリコン基板10及びゲート電極14を覆うように、引張応力を有する引張応力膜22を形成する工程と、引張応力膜22を除去する工程と、引張応力膜22が除去されたゲート電極14をマスクとして不純物をシリコン基板10内に導入し、ゲート電極14の両側のシリコン基板10内に不純物層24を形成する工程とを有している。

(もっと読む)

半導体装置及びその製造方法

【課題】駆動能力に優れたPMOSトランジスタを実現する。

【解決手段】半導体装置は、半導体基板101における素子分離領域102によって分離された活性領域104上に形成されたPMOSトランジスタであって、このPMOSトランジスタは、活性領域104上に形成されたゲート絶縁膜105bと、ゲート絶縁膜上に形成されたゲート電極106bと、サイドウォール108bと、ソース・ドレイン拡散層領域107bとを備える。ソース・ドレイン拡散層領域107bは、半導体基板101の主面に対して傾斜面101Bを有している。

(もっと読む)

半導体装置及びその製造方法

【課題】 化学機械研磨を行うことなく、比較的低コストでフルシリサイドゲート電極を形成することができる半導体装置の製造方法を提供する。

【解決手段】 半導体基板の表面上に第1の膜(27)及び第2の膜(28)を形成する。第2の膜をパターニングすることにより、内部に開口(41c)または凹部(41d)が配置された第1のパターン(41a)と、一方向に長い第2のパターン(31a)とを形成する。第1及び第2のパターンを覆い、それらのパターンの上面上の部分の膜厚が、半導体基板の表面上の部分の膜厚よりも薄くなるように、半導体基板の上に塗布法により、第3の膜(51)を形成する。第3の膜をエッチバックすることにより、第1及び第2のパターンの上面を露出させる。全面に第4の膜(55)を形成する。第1及び第2のパターンと、第4の膜とを反応させることにより、第1及び第2のパターンを、その底面まで、金属シリサイド化物にする。

(もっと読む)

半導体装置及びその製造方法

【課題】 簡便な方法で{111}結晶面にトランジスタを形成することが可能な半導体装置を提供する。

【解決手段】 表面が{100}結晶面で構成されたシリコンを有する基板(20)に、活性領域を画定する素子分離絶縁膜(21)が形成されている。この基板に、少なくとも側面の一部が、{111}結晶面が表れた第1の斜面で構成された凹部(36)が形成されている。第1の斜面上に、第1のトランジスタ(TL1)が形成されている。第1のトランジスタは、第1のゲート電極(41b)、第1のソース、及び第1のドレインを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】縦型絶縁ゲート型電界効果トランジスタのソースコンタクト抵抗を低減する。

【解決手段】半導体装置40では、半導体基板1の上部に、第1のソース層2aが設けられ、第1のソース層2a内に第1のソース層2aより深く、凹部3を有する第2のソース層2bが設けられる。凹部3上には、積層された第1の層間絶縁膜4a、ゲート電極膜5、及び第2の層間絶縁膜4bを貫通するようにゲート開口部が設けられる。側面にゲート絶縁膜6が設けられたゲート開口部には、第3のソース層2c、チャネル部7、及びドレイン層8が積層埋設される。第3のソース層2cは、下部が第2のソース層2bと接するように、凹部3上及びゲート開口部に埋設される。第1の層間絶縁膜4aと凹部3の間に突起状のゲート絶縁膜凸部6aが設けられる。

(もっと読む)

半導体装置

【課題】本発明は、MOSトランジスタの電流駆動能力をより向上させることができる半導体装置を提供する。

【解決手段】本発明に係る半導体装置は、半導体基板1、PMOSトランジスタP1、およびSiC層10を備えている。半導体基板1は、シリコンから成る。PMOSトランジスタP1は、半導体基板1の上面内に形成される。SiC層は、PMOSトランジスタP1のチャネル領域の下方から、PMOSトランジスタP1を構成する電極領域内若しくは電極領域下に渡って、形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】電流リークパスの発生やロールオフ特性の劣化等の問題を発生させることなく、チャネル領域に導入される歪み量を大幅に高め、動作速度を向上させることを可能とする信頼性の高い半導体装置を実現する。

【解決手段】サイドウォール5内には、シリコン基板1とゲート絶縁膜3との界面位置よりも高い位置、ここではシリコン基板1の表面上に例えばエピタキシャル成長によりせり上げ形成されたSiエピ層6が形成され、シリコン基板1のソース/ドレイン領域8の上部には凹部1aが形成される。そして、Siエピ層6と接触してシリコン基板1の表面から上部が突出するように凹部1a内にSiGeエピ層9が形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】電界効果トランジスタのオン電流を小さくすることなく、微細化を実現することのできる技術を提供する。

【解決手段】半導体基板の主面に素子分離領域2によって周囲を規定された活性領域3が配置され、この活性領域3は、周辺部3aに凹状の段差3cを有する断面形状となっており、活性領域3の周辺部3aの半導体基板の上面は、活性領域3の中央部3bの平坦な半導体基板の上面よりも低く形成されている。活性領域3の周辺部3aに凹状の段差3cを設けることにより、この活性領域3に形成されるMIS・FETの実質的なゲート幅を増加させて、MIS・FETのドレイン電流を増加させる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】構造を工夫することにより、ストレスライナー膜がチャネルに印加する応力を高め、電流駆動力が向上した半導体装置を得ることを目的とする。

【解決手段】本発明の半導体装置では、半導体基板1と、この半導体基板1に形成された素子分離絶縁膜2と、半導体基板1上から素子分離絶縁膜2上にかけて形成されたゲート電極4とを備えている。素子分離絶縁膜2は、ゲート電極4下以外の該素子分離絶縁膜2の上部を掘り下げることによって上段部と下段部の段差構造を有している。この半導体装置1は、ゲート電極4の両側の半導体基板1に形成されたソースあるいはドレインとなる半導体領域と、半導体領域、素子分離絶縁膜2の下段部、およびゲート電極4を覆って形成されたストレスライナー膜3とをさらに備えている。

(もっと読む)

半導体装置とその製造方法

【課題】 高駆動能力横型MOSトランジスタにおいて、単位面積当りのゲート幅を増大させつつ、素子特性の安定した高駆動能力横型MOSトランジスタの構造を提供する。

【解決手段】 MOSトランジスタにおいて、ゲート長方向に対し水平に配置するトレンチもしくはフィンの構造をゲート幅方向に階段状に形成することで半導体基板表面とトレンチ底部もしくはフィン頭頂部の段差が緩和されるため、単位面積当りの駆動能力を上げるために深いトレンチもしくは高いフィンを有している場合においても、イオン注入法を用いてチャネル領域、ソース拡散層およびドレイン拡散層の不純物濃度を均一に形成することができる構造と成る。これにより、チャネルが形成される面による特性の変動が現れない安定した特性が得られ、単位面積当りのオン抵抗が低減された高駆動能力横型MOSトランジスタを提供することが可能となる。

(もっと読む)

半導体装置

【課題】ロールオフ特性を劣化させずにチャネル領域に十分な歪みを生じさせることのできるエピタキシャル結晶を埋め込んだソース・ドレイン領域を有する半導体装置を提供する。

【解決手段】本発明の一態様に係る半導体装置は、半導体基板と、前記半導体基板上にゲート絶縁膜を介して形成されたゲート電極と、前記半導体基板の前記ゲート電極下の領域に形成されたチャネル領域と、前記チャネル領域を挟んで形成され、チャネル方向に平行な方向の導電型不純物の濃度分布が、前記ゲート電極から遠くなるに従って濃度が増加する部分を有するソース領域およびドレイン領域と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極下の絶縁膜の実装時のストレスによるクラックの発生を防止できるようにした半導体装置及びその製造方法、半導体装置の設計方法を提供する。

【解決手段】シリコン基板1に設けられたトランジスタと、このトランジスタを覆うようにシリコン基板1上に設けられた層間絶縁膜21と、層間絶縁膜21上にAlパッド31を介して設けられたバンプ電極41とを有し、バンプ電極41下方の領域のシリコン基板1には、トランジスタとしてゲート電極11の周縁部下のシリコン酸化膜が当該ゲート電極11の中央部下のシリコン酸化膜よりも厚いMOSトランジスタ10のみが設けられ、それ以外の領域のシリコン基板1には、トランジスタとしてゲート電極の中央部下からその周縁部下にかけてのシリコン酸化膜の厚さが均一なMOSトランジスタ70が設けられている。

(もっと読む)

101 - 120 / 274

[ Back to top ]