Fターム[5F140BH05]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース、ドレイン領域及びSD近傍領域 (10,828) | 形状、配置 (1,748) | 断面形状 (1,038)

Fターム[5F140BH05]の下位に属するFターム

せり上げSD (488)

せり下げSD(エッチングしているもの) (276)

Fターム[5F140BH05]に分類される特許

161 - 180 / 274

極薄先端を有する新規のトランジスタおよびその製造方法

【課題】低抵抗極薄先端領域を有する新規のトランジスタおよびVLSI生産可能製造方法を提供する。

【解決手段】第1のドープ半導体材料を前記半導体基板上に前記第1の側壁スペーサの外縁に整合して形成し、ドーパントを前記半導体材料から前記基板中に前記側壁スペーサの第1の対の下に拡散させて、一対の先端領域を形成し、側壁スペーサの第2の対を前記第1の半導体基板上に前記側壁スペーサの第1の対の外縁に整合して形成し、ソース/ドレイン・コンタクト領域を形成するために、イオンを前記半導体材料中および前記基板中に前記側壁スペーサの第2の対の外縁に整合させて注入する。

(もっと読む)

フィンベース半導体デバイスのドーピング方法

【課題】マルチゲートデバイスのドーピング方法を提供する。

【解決手段】ドーピング方法は、フィンを基板にパターニングする工程と、ゲートスタックを堆積する工程と、フィンをドーピングする工程を含む。フィンのドーピング工程は、ゲートスタックのパターニング工程後に、少なくともフィンの上面にブロッキングマスク材料を堆積する工程により行われる。ブロッキングマスク材料の堆積工程後に、ドーパントイオンが注入され、ブロッキングマスク材料が、部分的または完全に、フィンの上面をドーパントイオンからブロックする。

(もっと読む)

半導体装置

【課題】 ソース・ドレインとして金属電極が形成された電界効果トランジスタにおいて、短チャネル効果の発生及びリーク電流を抑制する。

【解決手段】 半導体基板11上にゲート絶縁膜14を介して形成されたゲート電極15と、金属電極からなり半導体基板11との界面にショットキー・バリアを形成するソース・ドレイン12,13とを具備してなる電界効果トランジスタを含む半導体装置であって、ソース側及びドレイン側の少なくとも一方の金属電極と半導体基板11との界面に、正孔又は電子に対して、前導体基板11と金属電極とのショットキー・バリアより低いバリアを形成する変調領域101,102が設けられている。

(もっと読む)

半導体装置の製造方法

【課題】ポリメタル構造のゲート電極を有するDRAM装置について、リフレッシュ特性を改善すると共に、配線抵抗の低減を実現する。

【解決手段】ポリメタルゲート電極の製造に際して、まず、ポリシリコンのゲート下部電極6を、その上に形成したマスク窒化膜でパターニングする。次いで、ゲート下部電極6についてリフレッシュ特性改善のための側壁酸化を行う。ゲート下部電極6及びマスク窒化膜の側壁に側壁酸化膜7を形成した後に、マスク窒化膜を除去してゲート下部電極6の表面を露出させ、その露出した表面上にタングステン層を含むゲート上部電極13を形成する。

(もっと読む)

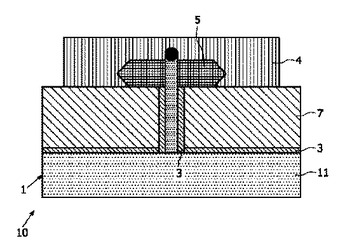

半導体デバイスを製造する方法及びそのような方法で得られる半導体デバイス

本発明は、少なくとも1つの半導体素子を備える半導体本体(1)を備える半導体デバイス(10)を製造する方法に関し、半導体本体(1)の上には、メサ形状半導体領域(2)が形成され、マスキング層(3)が、メサ形状半導体領域(2)の上に蒸着され、その頂部でメサ形状半導体領域(2)の側面と境界を接するマスキング層(3)の一部(3A)が取り除かれ、導電性接続領域(4)が、結果として得られる構造の上に形成され、メサ形状半導体領域(2)のための接点を形成する。本発明によれば、マスキング層(3)の部分(3A)の除去後、導電性接続領域(4)の形成前に、メサ形状半導体領域(2)が、マスキング層(3)の部分(3A)の除去によって自由にされるメサ形状半導体領域(2)の側面で追加的半導体領域(5)によって広げられる。このようにして、極めて低い接触抵抗を有するデバイス(10)が簡単な方法で得られる。好ましくは、メサ形状半導体領域(2)は、VLSのようなさらなるエピタキシアル成長プロセスによってナノワイヤによって形成される。追加的領域(5)は、例えば、MOVPEによって得られ得る。

(もっと読む)

(もっと読む)

半導体装置

【課題】ソース・ドレイン領域の構造を最適化することにより、高いIon/Ioff比を達成する電界効果トランジスタを含む半導体装置を提供する。

【解決手段】第1のゲート電極107と第2のゲート電極108は、チャネル領域101の両側に対向するように、第1のゲート絶縁膜103と第2のゲート絶縁膜104を介して、それぞれ形成され、ソース領域111および前記ドレイン領域121は、第1のゲート電極107と第2のゲート電極108の両側に、チャネル領域101を挟んで形成され、第1のゲート絶縁膜103とチャネル領域104との界面に垂直な方向のソース領域111の厚さ(TSis)が、同じ方向のチャネル領域101の厚さ(TSic)よりも厚く、かつ、ソース領域111と、第1、第2のゲート電極107、108が、ゲート長方向に離間している電界効果トランジスタを含む半導体装置。

(もっと読む)

応力がかけられたチャネル領域を有する改善されたCMOSデバイス及びそれを製造する方法(半導体デバイスおよび該半導体デバイスの形成方法)

【課題】 同じ応力誘起材料を用いて、n−FET及びp−FET内に異なる応力(すなわち、圧縮及び引張)を生成し、それぞれ内部の電子移動度及び正孔移動度を増大させること。

【解決手段】 本発明は、応力がかけられたチャネル領域を有する改善された相補型金属酸化膜半導体(CMOS)デバイスに関する。具体的には、各々の改善されたCMOSデバイスが、半導体デバイス構造体内に配置されたチャネル領域を有する電界効果トランジスタ(FET)を含み、半導体デバイス構造体は、第1の組の等価な結晶面の1つに沿って配向された上面と、第2の異なる組の等価な結晶面に沿って配向された1つ又は複数の付加的な表面とを有する。こうした付加的な表面は、結晶学的エッチングによって容易に形成することができる。さらに、内因性圧縮応力又は引張応力を有する1つ又は複数のストレッサ層が、半導体デバイス構造体の付加的な表面の上に配置され、かつ、FETのチャネル領域に引張応力又は圧縮応力をかけるように配置され、構成される。こうしたストレッサ層は、半導体デバイス構造体とは異なる格子定数を有する半導体材料の擬似格子整合成長によって形成することができる。

(もっと読む)

半導体装置

【課題】短チャネル効果を抑制できる構造であり、しきい値電圧を制御でき、電流駆動力に優れ、高速動作が可能なマルチフィンFETを有する半導体装置を提供することである。

【解決手段】上記の課題を解決した半導体装置の1態様は、半導体基板上に設けられたソース領域及びドレイン領域と、前記ソース領域及びドレイン領域を接続する複数のフィンと、前記半導体基板の上方に設けられ、前記各フィンを覆って設けられたゲート電極と、前記ソース領域若しくはドレイン領域から前記ゲート電極に向けて張り出し、隣接するフィンに接続して形成された張出し領域と、前記ゲート電極に接続する複数のパッド電極と、前記複数のパッド電極を接続する配線とを具備する。

(もっと読む)

埋め込みビットラインの形成方法

【課題】選択的無電解蒸着法を利用した埋め込みビットラインの形成方法を提供する。

【解決手段】埋め込みビットラインの形成方法は、基板をエッチングして形成されたビットライン用溝に無電解金属層を選択的に形成し、シリサイド工程を行ってビットライン用溝の内部にシリサイド膜を形成する。

(もっと読む)

高圧バイポーラCMOS−DMOS集積回路装置およびこれを形成するためのモジュール式方法

エピタキシャル層を含まない基板においてさまざまな半導体装置を製造するために全低温プロセスが用いられる。装置は分離されていないラテラルDMOS、分離されていない拡張されたドレインまたはドリフトされたMOS装置、ラテラルトレンチDMOS、分離されたラテラルDMOS、JFETおよび空乏モード装置、ならびにP−Nダイオードクランプおよびレクチファイヤおよび接合端子を含む。プロセスが高温処理の必要をなくし、「注入されたままの」ドーパントプロファイルを使用するので、残りの装置を生成するのに使用されるプロセスを変更する必要なしに、装置がICに加えられたり省略されたりすることを可能にするモジュール式アーキテクチャを構成する。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】TLPMと保護素子を集積すること。TLPMとともに保護素子を作製すること。

【解決手段】複数のトレンチ5により、p型半導体基板1上のn型ウェル領域2aの表面層を、第1メサ領域33、第2メサ領域34および第3メサ領域35に分割する。第1メサ領域33、第2メサ領域34および第3メサ領域35に、それぞれn型ソース領域7、n型ドレイン領域6およびp型コレクタ領域4bを設ける。n型ウェル領域2a内で、トレンチ5の底面にn型拡張ドレイン領域3a,3bを設ける。n型ソース領域7とn型拡張ドレイン領域3bの間にp型チャネル領域4aを設ける。このような構造により、コレクタ電極9bとソース電極10の間に、p型コレクタ領域4bと、n型ウェル領域2aおよびn型拡張ドレイン領域3bと、p型チャネル領域4aと、n型ソース領域7からなるPNPNサイリスタ構造の保護素子を設ける。

(もっと読む)

半導体装置の製造方法

【課題】不純物濃度を抑えることなくエピタキシャル成長層の端面での垂直成長面の発生を防止でき、これにより特性の優れた半導体装置を得ることが可能な製造方法を提供する。

【解決手段】ゲート電極脇の半導体基板上にエピタキシャル成長層からなるソース・ドレインを備えた半導体装置の製造方法であって、シリコンからなる半導体基板1上にゲート絶縁膜2aを介してゲート電極3aを形成し、ゲート絶縁膜2aおよびゲート電極3aの側壁にTEOSサイドウォール5を形成する。ゲート電極3aおよびTEOSサイドウォール5から露出された半導体基板1の表面層に対して、フッ酸ガスとアンモニアガスとを供給する処理とその後の熱処理とを行う表面ガスエッチング反応による前処理を行い、自然酸化膜6を除去する。その後、前処理された半導体基板1の露出表面上に、ソース・ドレインのエクステンション領域7をエピタキシャル成長させる。

(もっと読む)

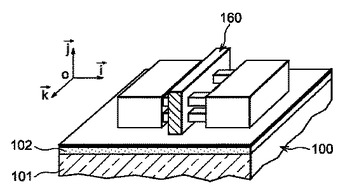

少なくとも1つの電子ビームによって前駆体材料を少なくとも1つの金属材料に分解することを含む、トランジスタゲートを製造する方法

本発明は、電子ビームに露出された後に少なくとも1つの金属材料に分解されることが可能な前駆体材料(150、250、350、450)からトランジスタゲート(160、260、360、460)を製造するマイクロエレクトロニクス法に関する。本発明は、特に、マルチチャネル、FinFET、懸架型チャネルトランジスタ、またはSONもしくはGAAタイプのトランジスタに適合する。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】 十分なキャリア移動度を有するチャネル部を備えた半導体装置およびその製造方法を提供する。

【解決手段】 基板14の絶縁層12上に形成された突起状の第1導電型の第1半導体層13と、第1半導体層13の第1側面および第1側面と対向する第2側面上にゲート絶縁膜16a、16bを介して形成されたゲート電極17と、第1半導体層13の第3側面に、基板14の絶縁層12上から形成された第1半導体層13と異なる第2導電型の第2半導体層18a、18bを有するソース領域19と、第1半導体層13の第3側面と対向する第4側面に、基板14の絶縁層12上から形成された第1半導体層13と異なる第2導電型の第2半導体層18c、18dを有するドレイン領域20とを具備する。

(もっと読む)

高耐圧横型MOSFET

【目的】直線状のセルを有する半導体装置において、端部の曲率部分でのオン耐圧を向上させることができる高耐圧横型MOSFETを提供すること。

【解決手段】n型半導体基板1の表面層に離してnウェル領域4とp型オフセット領域2を形成し、n型ウェル領域4の表面層にp型ソース領域5とn型コンタクト領域6を形成し、p型オフセット領域2の表面層にp型ドレイン領域3を形成し、n型ウェル領域4上とn型半導体基板1上に第1ゲート酸化膜7を形成し、この第1ゲート酸化膜7と接してp型オフセット領域2上にLOCOS8を形成し、第1ゲート酸化膜7上にゲート電極10を形成する。曲率部分のn型ウェル領域4上までを第1ゲート酸化膜7より厚い第2ゲート酸化膜(LOCOS8)で被覆することでn型ウェル領域5の表面の電界集中を緩和することができてオン耐圧の向上を図ることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】SiGe層をFinFETのチャネル領域とし、FinFETのチャネル幅(フィン高さ)の設計に自由度を有するフィン構造のFETを有する半導体装置、及び、その製造方法を提供する。

【解決手段】Si半導体層上にGe濃度が段階的に変化して形成されたバッファ層と、バッファ層との界面のGe濃度に応じたGe濃度でバッファ層上に形成されたSiGe層とにより所定の高さで形成されたフィンと、フィンの側面にゲート絶縁膜を介して形成されたゲート電極と、フィンのゲート電極の両側に形成されたソース領域及びドレイン領域とを有し、フィンにおけるゲート絶縁膜を介してゲート電極と対向したチャネル領域は、SiGe層の領域内に形成されていることを特徴とするフィン構造のFETを有する半導体装置とする。

(もっと読む)

半導体装置およびその製造方法

【課題】トランジスタの微細化に伴うショートチャネル効果やリーク電流の低減を可能とする。

【解決手段】p型シリコン基板101の主平面上に形成されたエピタキシャルSi層と、少なくともエピタキシャル層に形成されたチャネル領域と、該チャネル領域上にゲート絶縁膜106を介して形成されたゲート電極107とを含むトランジスタ構造を有し、このトランジスタ構造同士は互いに素子分離絶縁膜105を挟んで形成される半導体であって、チャネル領域の下部のパンチスルー・ストッパ層102にはチャネル領域よりも高濃度の不純物が含まれ、かつソース・ドレイン拡散層108は素子分離絶縁膜105上には延在しない。

(もっと読む)

半導体装置

【課題】島状半導体層の側壁に形成される三次元構造のトランジスタの優れた特性を生かしつつ、インバータ、NAND、NOR、AND、OR、あるいはそれらの組み合わせを含む論理回路が構成された半導体装置を提供する。

【解決手段】表面に1以上の島状半導体層を有する半導体基板と、各島状半導体層の側壁部に形成されトランジスタもしくは抵抗体として動作する1以上の素子と、1以上の島状半導体層に形成された複数の前記素子が組み合わされて論理回路を構成するように前記素子を互いに接続する導電部とを備えることを特徴とする半導体装置。

(もっと読む)

集積回路用の保護構造

【課題】 本発明は、nチャンネルMOS電界効果トランジスタを有する集積回路において保護のためにトランジスタがバイポーラ状態に迅速に変化し、そのバイポーラ状態が安定している保護構造を提供することを目的とする。

【解決手段】 2個のnチャンネルMOS電界効果トランジスタが対称軸Aに対称に配置され、それらのトランジスタのドレイン領域2 とドレイン接触領域4 の下方にドレイン領域2 とドレイン接触領域4 より軽くドープされたn型抵抗領域10が形成されてドレイン領域2 とドレイン接触領域4 の間の導電接続を構成し、その深さはドレイン領域2 の下のn型抵抗領域よりも深く形成されている。このような構造により破壊電圧に達したときドレイン領域2 とチャンネル11との間がコレクタ接合となるバイポーラトランジスタでn型抵抗領域10がコレクタ接合の一部を形成して大きい電力を吸収できる。

(もっと読む)

半導体装置及びその製造方法

【課題】 従来の半導体製造工程を大きく変更することなく、電界効果型トランジスタの実効的なチャネル面積の増大が可能な半導体装置及び半導体装置の製造方法を提供することを課題とする。

【解決手段】 電界効果型トランジスタの素子分離領域、ソース及びドレイン領域、チャネル領域が、半導体基板表面上に設けた複数の溝に沿って構成されていることを特徴とする半導体装置及び平坦な半導体基板の表面に一定間隔一定幅の線状パターン形成する工程、線状パターンをマスクとして半導体基板をエッチングし複数の溝を形成する工程、及び複数の溝に沿ってチャネル領域が構成された電界効果型トランジスタを形成する工程を含む半導体装置の製造方法によって解決される。

(もっと読む)

161 - 180 / 274

[ Back to top ]