Fターム[5F140BH07]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース、ドレイン領域及びSD近傍領域 (10,828) | 形状、配置 (1,748) | 断面形状 (1,038) | せり下げSD(エッチングしているもの) (276)

Fターム[5F140BH07]に分類される特許

1 - 20 / 276

化合物半導体装置及びその製造方法

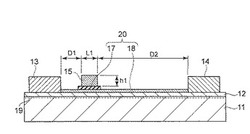

電界効果トランジスタ

【課題】耐圧および電流コラプス抑制性能をさらに向上できる電界効果トランジスタを提供する。

【解決手段】この電界効果トランジスタによれば、ゲート絶縁膜20を、ストイキオメトリなシリコン窒化膜よりもシリコンの比率が高いシリコン窒化膜で作製されたコラプス抑制膜18と上記コラプス抑制膜18上に形成されたSiO2絶縁膜17とを有する複層構造とすることにより、耐圧を向上できるだけでなく、電流コラプスも抑制できる。

(もっと読む)

半導体装置およびその製造方法

【課題】トンネルFETのオン電流の劣化を抑制しつつ、オフ電流を低減することが可能な半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置は、溝が形成された基板と、前記基板上の前記溝に隣接する位置にゲート絶縁膜を介して形成され、前記溝の反対側に位置する第1側面と、前記溝側に位置する第2側面とを有するゲート電極とを備える。さらに、前記装置は、前記ゲート電極の前記第1側面に形成された第1の側壁絶縁膜と、前記ゲート電極の前記第2側面と前記溝の側面に形成された第2の側壁絶縁膜とを備える。さらに、前記装置は、前記基板内において、前記ゲート電極の前記第1側面に対し前記第1の側壁絶縁膜側に形成された、第1導電型のソース領域と、前記基板内において、前記ゲート電極の前記第2側面と前記溝の側面に対し前記第2の側壁絶縁膜側に形成された、第2導電型のドレイン領域とを備える。

(もっと読む)

化合物半導体装置の製造方法、基板評価装置及び基板評価方法

【課題】化合物半導体層を形成する前の基板の状態で非接触のスクリーニングを行うことで、事前に化合物半導体層の不良発生を認識してこれを防止することができ、歩留まりの向上及び製造コストの削減を可能とする信頼性の高い化合物半導体装置を得る。

【解決手段】偏光レーザ12によりSiC基板1の基板面に偏光レーザ光を照射し、検出部13によりSiC基板1からの発光を検出し、表示部14によりSiC基板1の発光強度の面内分布を得て、SiC基板1の窒素混入量を評価した後、SiC基板1の上方に化合物半導体積層構造2を形成する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】比較的簡素な構成で電流コラプスの発生を抑制し、デバイス特性の劣化を抑えた信頼性の高い高耐圧のAlGaN/GaN・HEMTを実現する。

【解決手段】SiC基板1上に化合物半導体積層構造2を備えたAlGaN/GaN・HEMTにおいて、3層のキャップ層2eを用いることに加え、キャップ層2eのドレイン電極5の近傍(ゲート電極6とドレイン電極5との間で、ドレイン電極5の隣接箇所)に高濃度n型部位2eAを形成し、高濃度n型部位2eAでは、そのキャリア濃度が電子供給層2dのキャリア濃度よりも高く、そのエネルギー準位がフェルミエネルギーよりも低い。

(もっと読む)

電界効果トランジスタの製造方法および電界効果トランジスタ

【課題】ドーピング密度を増やすことなく、高濃度キャリア走行部を形成でき、高い移動度と低いオン抵抗を実現できる電界効果トランジスタの製造方法および電界効果トランジスタを提供する。

【解決手段】この電界効果トランジスタ1は、窒素ドープn型SiCドリフト層12のキャリア走行部14を挟むように形成されたソース13とドレイン15とを備える。ソース13とドレイン15は、エッチングによってキャリア走行部14に隣接して形成された段部16,17を有する。キャリア走行部14は、段部16,17の段差面16A,17Aに紫外光を照射することによって段部16,17から延びるように形成された積層欠陥部18を有する。積層欠陥部18は、3C‐SiCの結晶構造を持ち、量子井戸構造のようにふるまうことからキャリアがここに多数閉じ込められる。

(もっと読む)

しきい電圧の変動を減らした高電子移動度トランジスタ及びその製造方法

【課題】しきい電圧の変動を減らした高電子移動度トランジスタ及びその製造方法を提供する。

【解決手段】化合物半導体を含む基板上に形成され、二次元電子ガスチャネルとデプリーション領域とを備えるチャネル層と、二次元電子ガスチャネルに対応するように、チャネル層上に形成された第1チャネル供給層と、チャネル層のデプリーション領域及び第1チャネル供給層の一部の領域上に形成されたデプリーション層と、第1チャネル供給層上に形成され、デプリーション領域を挟んで対向するソース及びドレイン電極と、デプリーション層上に形成されたゲート電極と、を備え、第1チャネル供給層より分極率が小さい第2チャネル供給層を、チャネル層のデプリーション領域及び第1チャネル供給層の一部の領域上に備え、デプリーション層が第2チャネル供給層上に備えられる、高電子移動度トランジスタである。

(もっと読む)

半導体装置

【課題】 ゲート長方向に対し水平に複数本のトレンチを形成することにより単位面積当たりのゲート幅を増大させる高駆動能力横型MOSにおいて、素子面積を増加させずに更に駆動能力を向上させる。

【解決手段】 半導体基板表面から一定の深さに設けられた高抵抗第一導電型半導体のウェル領域と、前記ウェル領域の表面から途中の深さまで達する複数本のトレンチと、前記トレンチが形成する凹凸部の表面に設けられたゲート絶縁膜と、前記トレンチ内部に埋め込まれたゲート電極と前記トレンチ両端付近を除く前記凹凸部領域において前記トレンチ内部に埋め込まれたゲート電極と接触して基板表面に設けられたゲート電極膜と、前記ゲート電極膜と接触して前記トレンチ両端付近のトレンチ内部に半導体基板表面より深い位置に表面が位置するように埋め込まれたゲート電極膜と、前記ゲート電極膜と接触していない半導体面から前記ウェル領域の深さより浅く設けられた2つの低抵抗第二導電型半導体層であるソース領域とドレイン領域を有する半導体装置とした。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ノーマリオフ動作を実現しながら良好な伝導性能を得ることができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1上方に形成された電子走行層3及び電子供給層5と、電子供給層5上方に形成されたゲート電極11g、ソース電極11s及びドレイン電極11dと、電子供給層5とゲート電極11gとの間に形成されたp型半導体層8と、電子供給層5とp型半導体層8との間に形成され、電子供給層5よりもバンドギャップが大きい正孔障壁層6と、が設けられている。

(もっと読む)

代用ソース/ドレインフィンFET加工

【課題】製造コストの低減、およびプロセス時間の短縮を可能とするfinFETの製造方法を提供する。

【解決手段】finFETは、ソース領域、ドレイン領域、およびソース領域とドレイン領域との間のチャネル領域を有するフィンを備えるように形成される。上記フィンは、半導体ウエハ上でエッチングされる。ゲートスタックは、上記チャネル領域に直接接触する絶縁層と、上記絶縁層に直接接触する導電性のゲート材料とを有するように形成される。上記ソース領域および上記ドレイン領域は、上記フィンの第一領域を露出するためにエッチングされる。次に、上記第一領域の一部が、ドーパントでドーピングされる。

(もっと読む)

GaN系半導体装置

【課題】p型のGaN系半導体装置を提供する。

【解決手段】第1導電型のキャリアガスが発生した第1チャネル層106と、第1チャネル層106上に、第1チャネル層106よりバンドギャップが大きいGaN系半導体で形成されたバリア層110と、バリア層110上に、バリア層110よりバンドギャップが小さいGaN系半導体で形成され、第2導電型のキャリアガスが発生した第2チャネル層112と、第2チャネル層112にオーミック接続する第1ソース電極118と、第2チャネル層にオーミック接続する第1ドレイン電極120と、第1ソース電極118及び第1ドレイン電極120の間に形成された第1ゲート電極122と、を備え、第2導電型のキャリアガスのキャリア濃度が、第1ゲート電極122の下の領域で、第1ソース電極118及び第1ドレイン電極120の間の他の領域より低く、かつ、第1ゲート電極122により制御されるGaN系半導体装置。

(もっと読む)

低ノイズ及び高性能のLSI素子、レイアウト及びその製造方法

【課題】低ノイズ及び高性能のLSI素子、レイアウト及びその製造方法を提供する。

【解決手段】NMOS素子及びPMOS素子が何れもアナログ及びデジタルモードのような相異なるモードで動作される半導体素子において、これら素子の要求される動作モードによって特定素子にストレスエンジニアリングを選択的に適用する。フォトレジスト160をデジタル回路領域のPMOSトランジスタのみを覆うように形成し、Ge、Siなどのイオン162をストレスコントロール膜150に注入する。デジタル回路領域のPMOSトランジスタを除くあらゆる領域でストレスコントロール膜150はストレス解除膜またはストレス緩和膜152に変換され、デジタル回路領域のPMOSトランジスタのチャネル104bだけに圧縮応力が印加される状態が残る。

(もっと読む)

半導体装置およびその製造方法

【課題】リセスの下部に形成され不純物の注入量が異なる複数の領域を備える電界緩和層(リサーフ層)を備える半導体装置において、製造工程数の増加を抑えつつ、ディッシングの発生を防止する。

【解決手段】半導体装置は、半導体素子の外周領域であるPウェル2の外縁部に形成されたP型のリサーフ層10を備える。リサーフ層10は、P型不純物が第1面密度で注入された第1リサーフ領域11と、第1リサーフ領域11の外側に配設され、P型不純物が第1面密度よりも小さい第2面密度で注入された第2リサーフ領域12と、第2リサーフ領域12の外側に配設され、P型不純物が第2面密度よりも小さい第3面密度で注入された第3リサーフ領域13とを含む。このうち第1リサーフ領域11および第3リサーフ領域13は、半導体層の上面に形成されたリセス11r,13rの下に形成される。

(もっと読む)

半導体装置の製造方法

【課題】王水を用いることなくニッケルプラチナ膜の未反応部分を選択的に除去しうるとともに、プラチナの残滓が半導体基板上に付着するのを防止しうる半導体装置の製造方法を提供する。

【解決手段】シリコン基板10上に、ゲート電極16と、ゲート電極16の両側のシリコン基板10内に形成されたソース/ドレイン拡散層24とを有するMOSトランジスタ26を形成し、シリコン基板10上に、ゲート電極16及びソース/ドレイン拡散層24を覆うようにNiPt膜28を形成し、熱処理を行うことにより、NiPt膜28とソース/ドレイン拡散層24の上部とを反応させ、ソース/ドレイン拡散層24上に、Ni(Pt)Si膜34a、34bを形成し、過酸化水素を含む71℃以上の薬液を用いて、NiPt膜28のうちの未反応の部分を選択的に除去するとともに、Ni(Pt)Si膜34a、34bの表面に酸化膜を形成する。

(もっと読む)

半導体装置

【課題】従来の半導体装置においては、シリコンエピタキシャル層に結晶欠陥が生じ易いという問題がある。

【解決手段】半導体装置1は、シリコン基板10、歪み付与層20、シリコン層30、FET40、および素子分離領域50を備えている。シリコン基板10上には、歪み付与層20が設けられている。歪み付与層20上には、シリコン層30が設けられている。歪み付与層20は、シリコン層30中のFET40のチャネル部に格子歪みを生じさせる。シリコン層30中には、FET40が設けられている。FET40は、ソース・ドレイン領域42、SD extension領域43、ゲート電極44およびサイドウォール46を含んでいる。ソース・ドレイン領域42と上述の歪み付与層20とは、互いに離間している。FET40の周囲には、素子分離領域50が設けられている。素子分離領域50は、シリコン層30を貫通して歪み付与層20まで達している。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】シリサイド層を有するトランジスタにおいて、オン電流の高いトランジスタを得ることを課題とする。さらに、加熱処理等の工程を増やさずにオン電流の高いトランジスタを得ることを課題とする。

【解決手段】チャネル形成領域、不純物領域及びシリサイド層を有するシリコン膜と、ゲート絶縁膜と、ゲート電極と、不純物領域にシリサイド層を介して電気的に接続する配線とを有し、シリサイド層断面は、チャネル形成領域側の端点から膜厚が増加している第1領域と、第1領域と比べて膜厚が一定である第2領域とを有する半導体装置において、第1領域と第2領域は、シリサイド層断面の端点を通り、水平線とθ(0°<θ<45°)の角度をなす直線がシリサイド層と不純物領域の界面と交わる点を通り、且つ水平線に対し垂直な線で分けられ、シリコン膜の膜厚に対する第2領域の膜厚比は0.6以上である。

(もっと読む)

ハイブリッドMOSFETデバイスの製造方法およびそれにより得られるハイブリッドMOSFET

【課題】第1および第2のチャネル材料をそれぞれ有する第1MOSFETと第2MOSFETを含むハイブリッドMOSFETデバイスの製造方法を提供する。

【解決手段】III−Vオン絶縁体スタックは、続いて第1基板に接続される第2基板の上に形成される。III−V層103および絶縁体層は第1領域から選択的に除去されて、これにより第1基板の半導体層が露出する。第1MOSFETの第1ゲートスタック109は第1領域の露出した半導体層上に形成される。第2MOSFETの第2ゲートスタック109’は第2領域のIII−V層の上に形成される。

(もっと読む)

半導体装置の製造方法

【課題】王水を用いることなくニッケルプラチナ膜の未反応部分を選択的に除去しうるとともに、プラチナの残滓が半導体基板上に付着するのを防止しうる半導体装置の製造方法を提供する。

【解決手段】シリコン基板10上に、ゲート電極16と、ゲート電極16の両側のシリコン基板10内に形成されたソース/ドレイン拡散層24とを有するMOSトランジスタ26を形成し、シリコン基板10上に、ゲート電極16及びソース/ドレイン拡散層24を覆うようにNiPt膜28を形成し、熱処理を行うことにより、NiPt膜28とソース/ドレイン拡散層24の上部とを反応させ、ソース/ドレイン拡散層24上に、Ni(Pt)Si膜34a、34bを形成し、過酸化水素を含む71℃以上の薬液を用いて、NiPt膜28のうちの未反応の部分を選択的に除去するとともに、Ni(Pt)Si膜34a、34bの表面に酸化膜を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化されても高耐圧トランジスタのドレイン耐圧を向上させることができる半導体装置を提供する。

【解決手段】ゲート電極104Aの側面の側方下に位置する領域の半導体基板(活性領域)101の表面部が除去されて掘り下げ部121が形成されている。掘り下げ部121の側壁面及び底面の近傍に位置する部分の半導体基板101中に低濃度ドレイン領域105A2が形成されている。ゲート電極104Aの側面並びに掘り下げ部121の側壁面及び底面の一部を覆うように絶縁性サイドウォールスペーサ108Aが形成されている。絶縁性サイドウォールスペーサ108Aの外側で且つ掘り下げ部121の底面の近傍に位置する部分の半導体基板101中に、低濃度ドレイン領域105A2に囲まれるように高濃度ドレイン領域109A2が形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】第1のトランジスタと第2のトランジスタが、ぞれぞれのドレイン領域とソース領域を共有して同一の半導体基板上に形成される構成の半導体装置の製造において、それぞれのトランジスタのソース領域およびドレイン領域の直下に埋め込み絶縁膜を効率的に形成できる製造方法を提供する。

【解決手段】半導体基板上にそれぞれのトランジスタのソース領域およびドレイン領域に対応してトレンチを形成し、前記トレンチをSiGe混晶層と半導体層を順次形成することにより充填し、さらに第1のトランジスタのソース領域および第2のトランジスタのドレイン領域直下のSiGe混晶層を、素子分離溝を介して選択エッチングにより除去し、第1のトランジスタのドレイン領域および第2のトランジスタのソース領域として共有される拡散領域直下のSiGe混晶層を、前記拡散領域に形成した孔を介して選択エッチングし、除去する。

(もっと読む)

1 - 20 / 276

[ Back to top ]