Fターム[5F140BH05]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース、ドレイン領域及びSD近傍領域 (10,828) | 形状、配置 (1,748) | 断面形状 (1,038)

Fターム[5F140BH05]の下位に属するFターム

せり上げSD (488)

せり下げSD(エッチングしているもの) (276)

Fターム[5F140BH05]に分類される特許

41 - 60 / 274

半導体装置とその製造方法、及び半導体装置の評価方法

【課題】チャネルに応力が印加されるMOSトランジスタの特性のばらつきを防ぐことができる半導体装置の製造方法を提供すること。

【解決手段】半導体基板10の上にゲート絶縁膜を形成する工程と、ゲート絶縁膜の上にゲート電極14cを形成する工程と、ゲート電極14cの側面にサイドウォール15a、15bを形成する工程と、サイドウォール15a、15bを形成した後に、有機アルカリ溶液又はTMAHをエッチング液として用いて、ゲート電極14cの横の半導体基板10に穴10a、10bを形成する工程と、穴10a、10bにソース/ドレイン材料層18a、18bを形成する工程とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】トレンチパワーDMOSトランジスタにおいて、ソース引き出し電極とゲート引き出し電極の短絡を確実に防止する。併せて上記DMOSトランジスタのサイズの縮小を図ること及びソース・ドレイン間絶縁破壊電圧VDSの低下を防止する。

【解決手段】N+型ソース層13の底面の直下のP型ベース層9内に形成されたP+型コンタクト層14を、コンタクト用開口25の内の少なくとも一部の該コンタクト用開口25の底面に露出するN+型ソース層13を貫通するくぼみ部16に露出させる。次にコンタクト用開口25の底面に露出するN+型ソース層13及びくぼみ部16に露出するN+型ソース層13、P+型コンタクト層14に接続し、コンタクト用開口25内をその上端まで埋設して延在するソース引き出し電極17aを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】上部拡散層上にコンタクトパッドを別途形成することなく、コンタクト合わせマージンを向上させる縦型トランジスタ構造を提供する。

【解決手段】本発明の半導体装置は、基板上に、柱状の半導体からなるボディ部(5)と、ボディ部の側面にゲート絶縁膜(10)を介して設けられるゲート電極(11)と、ボディ部の下部に接続される第1の拡散層(9)と、ボディ部の上面に接続される第2の拡散層(16)とを備える縦構造トランジスタを含む半導体装置であって、第2の拡散層(16)は、ボディ部の上面の面積以下の基板平面方向の断面を有する第1部分(14)と、第1部分の上部にボディ部の上面の面積以上の基板平面方向の断面を有する第2部分(15)とを備え、少なくとも第2部分がエピタキシャル成長層であり、隣接する縦型トランジスタ間に第2部分が接触することを防止する絶縁膜(17)を有する。

(もっと読む)

エピタキシャルソース/ドレインが自己整合したマルチゲート半導体デバイス

低寄生抵抗であるチャネル歪みされたマルチゲートトランジスタとその製造方法に係る。ゲートを連結したチャネル側壁の高さがHsiである半導体フィンのチャネル領域の上にゲートスタックを形成されてよく、ゲートスタックに隣接する半導体フィンのソース/ドレイン領域内に、エッチングレートを制御するドーパントを注入してよい。ドーピングされたフィン領域をエッチングして、半導体フィンの、略Hsiに等しい厚みを除去して、ゲートスタックの一部の下にある半導体基板の部分を露呈させるソース/ドレイン延長キャビティを形成してよい。露呈した半導体基板の上に材料を成長させて、再成長したソース/ドレイン・フィン領域を形成して、ソース/ドレイン延長キャビティを充填して、ゲートスタックからの長さを、チャネルの長さに実質的に平行な方向に離れる方向に延ばしてよい。 (もっと読む)

半導体装置及びその製造方法

【課題】応力絶縁膜により、MISトランジスタの駆動能力が劣化することを防止する。

【解決手段】第1のMISトランジスタpTr1は、第1の活性領域10aにおける第1のサイドウォール19Aの外側方下に設けられたトレンチ22内に形成され、第1の活性領域10aにおけるチャネル領域のゲート長方向に第1の応力を生じさせるシリコン混晶層23を含む第1導電型の第1のソースドレイン領域27aと、第1の活性領域10a上に第1のゲート電極14a、第1のサイドウォール19A及び第1のソースドレイン領域27aを覆うように形成され、第1の応力とは反対の第2の応力を生じさせる応力絶縁膜31とを備えている。シリコン混晶層23の最上面は、第1のゲート電極14a直下に位置する半導体基板10の表面よりも高く形成されている。シリコン混晶層23と第1のサイドウォール19Aとの隙間24には、第1の応力緩和膜28aが形成されている。

(もっと読む)

誘電体分離型半導体装置

【課題】高耐圧かつ、電流駆動能力が高く、かつ電流集中による素子破壊の起こりにくい誘電体分離型半導体装置を提供する。

【解決手段】半導体支持基板の上に、絶縁された第一導電型の半導体領域とを有する誘電分離基板に形成した誘電体分離型半導体装置において、第一導電型の半導体領域と絶縁分離領域の間と、前記第1導電型の半導体領域の基板表面側と、に形成されたドレイン領域と、第一導電型のソースと第二導電型の半導体領域のチャネルからなる複数個の単位ソース領域と、第一導電型の半導体領域の基板表面側に形成されたドレイン領域と前記複数個の単位ソース領域の間を制御する複数個のゲート電極とを、備え、隣接する前記単位ソース領域間に絶縁分離領域が、基板底面側から基板表面側に向けて突き出した形状とされ、この絶縁分離領域上の素子表面領域が前記第一導電型の半導体領域より抵抗値が高い。

(もっと読む)

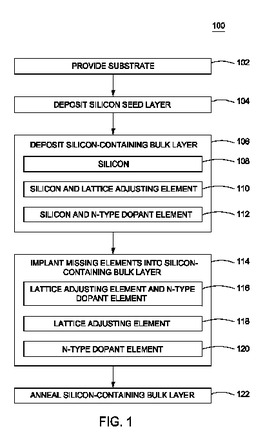

NMOSエピ層の形成方法

制御されたチャネル歪みおよび接合抵抗を有するNMOSトランジスタ、およびその製造方法が、本明細書で提供される。いくつかの実施形態において、NMOSトランジスタを形成するための方法は、(a)p型シリコン区域を有する基板を準備すること、(b)p型シリコン区域の上にシリコンシード層を堆積すること、(c)シリコン、シリコンおよび格子調整元素またはシリコンおよびn型ドーパントを備えるシリコン含有バルク層をシリコンシード層の上に堆積すること、(d)(c)で堆積されたシリコン含有バルク層に欠けている格子調整元素またはn型ドーパントのうちの少なくとも1つをシリコン含有バルク層の中に注入すること、(e)(d)の注入の後、シリコン含有バルク層をエネルギービームを用いてアニールすることを含むことができる。いくつかの実施形態において、基板は、その中に画定されたソース/ドレイン区域を有する、部分的に製造されたNMOSトランジスタデバイスを備えることができる。  (もっと読む)

(もっと読む)

窒化物半導体素子

【課題】ゲート絶縁膜の絶縁破壊を抑制または防止できる構造を有する窒化物半導体素子を提供する。

【解決手段】電界効果トランジスタ1(窒化物半導体素子)は、窒化物半導体の積層構造部3と、ゲート絶縁膜15と、ゲート電極16と、ソース電極18と、ドレイン電極19と、ガードリング層11とを含む。積層構造部3は、n型GaN層4,5、p型GaN層6およびn型GaN層7を積層して構成されている。ゲート絶縁膜15は、n型GaN層5、p型GaN層6およびn型GaN層7に跨るように、積層構造部3の壁面9に形成されている。ゲート電極16は、ゲート絶縁膜15を挟んでp型GaN層6に対向している。ガードリング層11は、p型GaN層6における壁面9に間隔を開けて対向するようにn型GaN層5上に形成されたp型GaN層からなる。

(もっと読む)

半導体装置、および、半導体装置の製造方法

【課題】チャネル領域に強い歪みを印加することによりデバイス特性を改善した半導体装置を提供すること。

【解決手段】半導体基板1と、半導体基板1の第1の面に形成されたゲート絶縁膜2と、ゲート絶縁膜2の上に形成されたゲート電極3と、ゲート電極3の側壁に形成されたゲート側壁絶縁膜4と、ゲート電極3の下の半導体基板1中に形成されるチャネル領域に隣接し、不純物が注入されたソース/ドレイン拡散層領域5、6と、ゲート電極3の上方を除き、ソース/ドレイン拡散層領域5、6の上に形成された応力印加膜8と、を有し、半導体基板1の第1の面におけるソース/ドレイン拡散層領域5、6が形成された領域には、凹部または凸部50、51、60、61が設けられている半導体装置を提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】 オン抵抗を増大させることなく、高耐圧化を実現させることが可能な半導体装置を実現する。

【解決手段】 P型の半導体基板1内には、P型ボディ領域3と、P型ボディ領域3に対して基板面に平行な方向に離間して形成されたN型ドリフト領域5と、N型ドリフト領域内のフィールド酸化膜11で分離された領域に形成された、N型ドリフト領域5より高濃度N型のドレイン領域8と、P型ボディ領域3内に形成された、N型ドリフト領域5より高濃度N型のソース領域6を備える。そして、P型ボディ領域3の一部底面に離散的に連結すると共に、それぞれが基板面に平行な方向に延伸し、各先端がドリフト領域5内に達するよう、N型ドリフト領域5より高濃度のP型埋め込み拡散領域4が形成される。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】オン抵抗を大幅に低減し、十分な高電圧動作且つ高出力を得ることができる信頼性の高い化合物半導体装置を実現する。

【解決手段】ソース電極12及びドレイン電極13の下方の凹部7,8を充填し、電子供給層4の上方を覆う、Siを含むn−GaN層9が形成されており、n−GaN層9は、ソース電極12の下方及びドレイン電極13下方に含まれるSiの方が、ゲート電極15の近傍に含まれるSiよりも濃度が大きくなるように、Si添加量を漸減させながら成長形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】寄生抵抗の低下を図る。

【解決手段】半導体装置は、半導体基板10と、前記半導体基板上のソース/ドレイン領域に形成された第1半導体層11と、前記第1半導体層上に形成された第1部分12aと、前記ソース/ドレイン領域の間に位置するチャネル領域に形成された第2部分12bとを有する第2半導体層12と、前記第2半導体層の前記第1部分上に形成された第3半導体層13と、前記第2半導体層の前記第2部分の周囲に絶縁膜21を介して形成されたゲート電極22と、前記第1半導体層、前記第2半導体層の第1部分および前記第3半導体層内に形成されたコンタクトプラグ31と、を具備し、前記第2半導体層内における前記コンタクトプラグの径は、前記第1半導体層及び前記第3半導体層内における前記コンタクトプラグの径より小さい。

(もっと読む)

蓄積型FINFET、回路、及びその製造方法

【課題】FinFET、集積回路、およびFinFETの形成方法を提供する。

【解決手段】基板120、前記基板上にあり、ソース106とドレイン110との間のチャネル108を含み、前記ソース106、前記ドレイン110、および前記チャネル108は、第1型ドーパントを有し、前記チャネル108は、ゲルマニウム、シリコンゲルマニウム、またはIII−V族半導体の少なくとも1つを含むフィン構造、前記チャネル108上のゲート誘電体層114、および前記ゲート誘電体層114上のゲート116を含むFinFET。

(もっと読む)

高ゲルマニウム濃度のSiGeストレッサの形成方法

【課題】SiGeストレッサの形成方法と集積回路のトランジスタ構造を提供する。

【解決手段】SiGeストレッサを形成する方法であって、前記方法は、ソース領域とドレイン領域間にチャネルを有する半導体基板上のソース領域とドレイン領域の少なくとも1つに第1SiGe層を堆積するステップ、及び前記第1SiGe層の上部を酸化層に変換し、前記第1SiGe層の底部を第2SiGe層に変換するステップを含み、前記第2SiGe層は、前記第1SiGe層より高いGe濃度を有する方法。

(もっと読む)

半導体装置

【課題】高耐圧の電界効果トランジスタを有する半導体装置のキンク現象を抑制または防止する。

【解決手段】高耐圧pMISQHp1のチャネル領域のゲート幅方向の両端の溝型の分離部3と半導体基板1Sとの境界領域に、高耐圧pMISQHp1のソースおよびドレイン用のp+型の半導体領域P1,P1とは逆の導電型のn+型の半導体領域NVkを、高耐圧pMISQHp1の電界緩和機能を持つp−型の半導体領域PV1,PV1(特にドレイン側)に接しないように、そのp−型の半導体領域PV1,PV1から離れた位置に配置した。このn+型の半導体領域NVkは、溝型の分離部3よりも深い位置まで延在されている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ゲート電極7作製後にチャネル部12を作製する縦型MISFETの製造方法において、ゲート絶縁膜10に損傷を与えたり移動度を劣化させたりすることなく、孔底面に形成された絶縁膜や、自然酸化膜を除去する。

【解決手段】単結晶半導体基板1または単結晶半導体層に形成された不純物領域8の上に、第一絶縁層4、5と、ゲート電極層7と、第二絶縁層5、4と、をこの順に積層した積層体を形成し、前記積層体に不純物領域8が露出する孔を形成し、少なくとも前記孔の側壁に露出しているゲート電極層7、および、前記孔の底面に露出している不純物領域8の上に絶縁膜10を形成し、ゲート電極層7の露出部分の上に形成された絶縁膜10の上に半導体膜を重ねて形成し、不純物領域8の上に形成された絶縁膜を除去し、孔の底面に露出している不純物領域8に接し、孔底面から孔の開口部までつながる半導体部を形成する半導体装置の製造方法を提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】pMOSトランジスタにcSiGeとeSiGeを適用し、且つゲート絶縁膜におけるダメージ発生を防止でき、素子特性の向上及びしきい値制御性の向上をはかる。

【解決手段】pMOSトランジスタのチャネル部及びソース・ドレイン領域にSiGeを用いた半導体装置において、Si基板202上の一部に形成され、pMOSトランジスタのチャネルとなる第1のSiGe層205と、第1のSiGe層205上にゲート絶縁膜206を介して形成されたゲート電極208と、pMOSトランジスタのソース・ドレイン領域に埋め込み形成され、且つチャネル側の端部が基板表面よりも深い位置でチャネル側に突出するように形成された第2のSiGe層214と、第1のSiGe層205と第2のSiGe層214とを分離するように、基板の表面部でSiGe層205,214間に挿入されたSi層222とを備えた。

(もっと読む)

MOSトランジスタ及びMOSトランジスタを備えた半導体装置の製造方法

【課題】縦型トランジスタにおいて、柱状半導体層上部のシリサイドの細線効果を低減すること、また、シリサイドと上部拡散層間の界面抵抗を低減することによりトランジスタ特性を改善すること、またコンタクトとゲート間のショートが発生しない構造を実現すること。

【解決手段】柱状半導体層と、前記柱状半導体層の底部に形成される第1のドレイン又はソース領域と、該柱状半導体層の側壁を包囲するように第1の絶縁膜を介して形成されるゲート電極と、前記柱状半導体層上面上部に形成されるエピタキシャル半導体層とを含み、前記第2のソース又はドレイン領域が少なくとも前記エピタキシャル半導体層に形成され、前記第2のソース又はドレイン領域の上面の面積は、前記柱状半導体層の上面の面積よりも大きいことを特徴とするMOSトランジスタ。

(もっと読む)

電界効果トランジスタ

【課題】オン抵抗が低く耐圧が高い電界効果トランジスタを提供すること。

【解決手段】窒化物系化合物半導体からなる電界効果トランジスタであって、基板と、前記基板上に形成されたバッファ層と、前記バッファ層上に形成された高抵抗層又は下地層と、前記高抵抗層又は下地層上に形成された、炭素を含有するキャリア濃度制御層と、前記キャリア濃度制御層上に形成されたキャリア走行層と、前記キャリア走行層上に形成された、前記キャリア走行層とはバンドギャップエネルギーが異なるキャリア供給層と、前記キャリア供給層から所定の深さに到るまで形成されたリセス部と、前記キャリア供給層上に前記リセス部を挟んで形成されたソース電極およびドレイン電極と、前記キャリア供給層上にわたって前記リセス部内を覆うように形成されたゲート絶縁膜と、前記リセス部において前記ゲート絶縁膜上に形成されたゲート電極と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】ソース、ドレインの低抵抗化及び寄生容量の低減化のための構造、所望のゲート長、ソース、ドレイン形状、柱状半導体の直径が得られるSGTの製造方法を提供する。

【解決手段】第1の平面状半導体層上に第1の柱状半導体層を形成する工程と、第1の柱状半導体層の下部と第1の平面状半導体層に第1の第2導電型半導体層を形成する工程と、第1の柱状半導体層の底部及び第1の平面状半導体層上に第1の絶縁膜を形成する工程と、第1の柱状半導体層の周囲にゲート絶縁膜およびゲート電極を形成する工程と、ゲート電極の上部且つ第1の柱状半導体層の上部側壁と、ゲート電極の側壁に第2の絶縁膜をサイドウォール状に形成する工程と、第1の第2導電型半導体層と第2の第2導電型半導体層との間に第1導電型半導体層を形成する工程と、第1の第2導電型半導体層の上部表面と、第2の第2導電型半導体層の上部表面に金属と半導体の化合物を形成する工程とを含む。

(もっと読む)

41 - 60 / 274

[ Back to top ]