Fターム[5F140BH12]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース、ドレイン領域及びSD近傍領域 (10,828) | 不純物分布 (3,598) | 平面分布の形状、配置 (82)

Fターム[5F140BH12]に分類される特許

1 - 20 / 82

半導体装置およびその製造方法

【課題】スイッチング素子として利用される高耐圧かつ低オン抵抗な半導体装置を安価に提供する。

【解決手段】第1導電型の不純物を含有し、互いに対向する第1の主面と第2の主面とを有する半導体基板と、第2導電型の不純物を第1の濃度で含有し、前記半導体基板の前記第1の主面に露出するように形成された第1の拡散領域と、前記第2導電型の不純物を前記第1の濃度よりも高い第2の濃度で含有し、前記半導体基板の前記第1の主面に露出するように前記第1の拡散領域の側方に形成された第2の拡散領域と、前記第1導電型の不純物を含有し、前記半導体基板の前記第1の主面に露出するように前記第1の拡散領域の上方に形成された第3の拡散領域と、前記第2の拡散領域と絶縁膜を介して対向する制御電極と、を備え、前記第1の拡散領域と前記第2の拡散領域とは、前記制御電極に印加される電圧に応じて制御される電流の主経路を形成する。

(もっと読む)

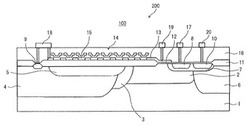

半導体装置

【課題】横型DMOSの素子面積の増大を抑制し高耐圧化をはかる。

【解決手段】第1の半導体素子100Aは、第1半導体層12Aと、第2半導体層14Aと、第2半導体層に隣接する第3半導体層16Aと、第1絶縁層20Aと、第2半導体層の表面に選択的に設けられた第1ベース領域30Aと、第1ベース領域の表面に選択的に設けられた第1ソース領域32Aと、第1絶縁層の内部に設けられた第1ゲート電極40Aと、第1ベース領域の下に設けられ、第1半導体層の表面から第1ベース領域の側に延在する第1ドリフト層18Aと、第1ソース領域32Aに対向し、第1絶縁層20Aを挟んで第3半導体層16Aの表面に設けられた第1ドレイン領域34Aを有す。第1ドリフト層18Aの不純物元素の濃度は、第1半導体層12Aの不純物元素の濃度よりも低い。第1ドリフト層の不純物元素の濃度は、第2半導体層14Aの不純物元素の濃度よりも高い。

(もっと読む)

半導体装置およびその製造方法

【課題】高耐圧MOSFETの耐圧を向上させる。

【解決手段】MOSFETのドレイン領域を構成するLDD層6内に、LDD層6よりも不純物濃度層が低いN−−層11を形成して、チャネル領域側のドレイン領域端部の不純物濃度を低下させる。また、ソース領域側のLDD層7をLDD層6よりも浅い接合深さで、且つLDD層6よりも低い不純物濃度で形成する。これにより、オン状態およびオフ状態のいずれの状態においてもドレイン領域の電界を緩和し、インパクトイオンおよびパンチスルーの発生を防ぐ。

(もっと読む)

横型の絶縁ゲート型バイポーラトランジスタを備えた半導体装置

【課題】オン電圧の低減と、破壊耐量確保、高速スイッチングを同時に実現できる横型IGBTを提供する。

【解決手段】エミッタ側にn型バリア層15を形成することで、ホールのバリアとして機能させ、コレクタ側から注入されたホールがエミッタ側のチャネルpウェル層6に流れ出てホール濃度が低下することを防止する。これにより、エミッタ近傍のn-型ドリフト層2内のキャリア濃度を上げることが可能となり、オン電圧の低減が可能となる。また、コレクタ側において、コレクタ電極12のうちp+型層4aと接触している部分をオーミック接触、p型層4bと接触している部分をショットキー接触とする。このショットキー接触とされた部分において、コレクタ側からのホールの注入が抑制され、蓄積キャリアを低減して、寄生バイポーラトランジスタがオンし難くなるようにできる。よって、低オン電圧を維持しながらスイッチング耐圧を確保することが可能となる。

(もっと読む)

半導体装置

【課題】素子面積を増加させることなく、高耐圧の半導体装置を実現させる。

【解決手段】第1方向に沿ったソース領域、ゲート電極を挟んでソース領域とは反対側に第1方向に沿ったドレイン領域、一部がゲート電極下面と対向しソース領域とドレイン領域との間に設けた絶縁体層、一部がゲート電極下面と対向し絶縁体層よりもソース領域側に設けたベース領域、一部が第2方向に第2長さを有してゲート電極下面と対向し、ベース領域よりも絶縁体層側に設けたドリフト領域、を有する素子活性領域部、ゲート絶縁膜の上に設けたゲート電極、ソース領域、一部がゲート電極下面と対向して設けた絶縁体層、一部がゲート電極下面と対向して絶縁体層よりもソース領域側に設けたベース領域、一部が第1方向に第2長さよりも短い第1の長さを有してゲート電極下面と対向してベース領域よりも絶縁体層側に設けたドリフト領域、を有する素子終端領域部と、を備える。

(もっと読む)

半導体装置

【課題】耐圧の向上が図られる半導体装置を提供する。

【解決手段】n-型半導体領域には、ドレイン領域となるn-型の拡散領域が形成されている。n-型の拡散領域の周囲を取囲むようにp型の拡散領域が形成されている。p型の拡散領域には、ソース領域となるn+型の拡散領域が形成されている。n-型の拡散領域の直下には、p-型の埋め込み層13が形成されている。n-型の半導体領域の領域には、高電位が印加されるn+型の拡散領域が形成され、そのn+型の拡散領域の表面上には電極が形成されている。電極とドレイン電極とは、配線20によって電気的に接続されている。配線20の直下に位置する部分に、p-埋め込み層13に達するトレンチ3aが形成されて、ポリシリコン膜81が形成されている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ESD耐量を向上させたLDMOSFETを備える半導体装置を提供する。

【解決手段】半導体層200よりも高濃度のP型の押込拡散領域440は、半導体層200の表層から底面まで設けられている。押込拡散領域440よりも低濃度のP型の第1ウェル領域300は、半導体層200に、平面視で一部が押込拡散領域440と重なるように設けられている。N型のドレインオフセット領域540は、半導体層200に、平面視で第1ウェル領域300と接するように設けられている。ドレインオフセット領域540よりも高濃度のN+型のドレイン領域520は、ドレインオフセット領域540内に設けられている。ドレインオフセット領域540よりも高濃度のN型の第2ウェル領域560は、半導体層200のうち、ドレインオフセット領域540の下に位置して、平面視でドレイン領域520と重なる領域に設けられている。

(もっと読む)

半導体装置

【課題】回路面積の増大を抑制しつつ高耐圧の半導体装置を得る。

【解決手段】第1導電型の第1半導体層は、第1方向を長手方向として素子領域から延びて素子終端領域まで形成され、第1の不純物濃度を有し、MOSトランジスタのドレイン領域として機能する。また、第1導電型の第2半導体層は、第1方向を長手方向として素子領域から延びて素子終端領域まで形成され、第1の不純物濃度より小さい第2の不純物濃度を有し、第1半導体層と接続されるように配置されてMOSトランジスタのドリフト層として機能する。素子領域及び素子終端領域は、第1方向と直交する第2方向の幅が同一であり、第2方向に沿った断面に関し、素子終端領域における第2半導体層の幅は、素子領域における第2半導体層の幅よりも大きい。

(もっと読む)

電界効果型トランジスタ、電界効果型トランジスタの製造方法、固体撮像装置、及び電子機器

【課題】 ゲート電極の微細化が可能な電界効果型トランジスタを提供する。

【解決手段】 本開示に係る電界効果型トランジスタは、基板10と、基板10上に形成され、フィン領域13と該フィン領域13の両端にそれぞれ形成されるソース領域14とドレイン領域15とを有する半導体層と、フィン領域13の少なくとも2面の一部と接する凸部171を有するゲート電極17と、を備える。

(もっと読む)

半導体装置

【課題】横型構造のパワートランジスタにおいて、寄生サイリスタのラッチアップ耐量を改善するとともに、ターンオフ時間を短縮する。

【解決手段】エミッタ電極(21)下部に設けられるn+エミッタ層(6)を、所定の間隔で互いに離れて配置される単位領域(60)で構成する。単位領域においてエミッタ電極とのコンタクトを取るとともに、pベース層(5)よりも高濃度でp+層(45)を少なくともエミッタ層の下方に設ける。

(もっと読む)

MOSトランジスタおよび半導体集積回路装置の製造方法

【課題】埋込絶縁膜によりゲート絶縁膜の実効的膜厚がドレイン端近傍において増大される構成の高電圧MOSトランジスタにおいて、耐圧特性を劣化させずにオン抵抗を低減させる。

【解決手段】第1導電型の第1のウェル11NW第2導電型の第2のウェル11PWとが形成された半導体基板11と、チャネル領域11CHと、ソースエクステンション領域11aと、第1のウェル11NW中に形成された埋込絶縁膜11Oxと、第2のウェル11PWと埋込絶縁膜11Oxの間に形成されたオフセット領域11offと、埋込絶縁膜11Oxに対してオフセット領域11offとは反対の側に形成された、第1導電型を有するドレインエクステンション領域11bと、チャネル領域11CHとオフセット領域11offおよび埋込絶縁膜11Oxを覆って、ゲート絶縁膜12Gとn+型のポリシリコンゲート電極13Gよりなるゲート電極構造と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】基板に対して斜め方向からイオン注入を行う工程を含む半導体装置の製造方法においてゲート電極サイズの縮小化とリーク電流特性の改善を両立することができる製造方法を提供する。

【解決手段】

半導体基板の表面にゲート電極を形成する。ゲート電極のゲート長方向と交差するゲート幅方向における両端面を被覆するレジストマスクを形成する。半導体基板にゲート長方向成分およびゲート幅方向成分を有する注入方向で不純物イオンを注入して半導体基板の表面のゲート電極を挟む両側にゲート電極とオーバーラップした低濃度不純物層を形成する。ゲート電極の側面を覆うサイドウォールを形成する。ゲート電極およびサイドウォールをマスクとして不純物イオンを注入して半導体基板の表面のゲート電極を挟む両側にゲート電極から離間した高濃度不純物層を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電圧の閾値電圧がばらつくことを抑制することができると共に、チャネル抵抗を低減させることができる半導体装置を提供する。

【解決手段】ベース領域4、ソース領域6、ドレイン領域7の不純物濃度を均一とし、第1、第2トレンチ8a、8bをベース領域4よりも浅く形成する。このような半導体装置では、ベース領域4、ソース領域6、ドレイン領域7の不純物濃度が均一とされているため、ゲート電圧の閾値電圧がばらつくことを抑制することができ、また、ソース領域6およびドレイン領域7を深くすることによりチャネル領域を有効に活用でき、チャネル抵抗を低減することができる。さらに、第1、第2トレンチ8a、8bをベース領域4より浅く形成しているため、ベース領域4のうち第1、第2トレンチ8a、8bより深く形成されている部分にはチャネル領域が形成されず、ソース領域6から深さ方向に電流が流れることを抑制することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】3次元構造のパワーMOSトランジスタやIBGTの破壊耐量を改善する。

【解決手段】一つの実施形態の半導体装置には、N+基板1に溝21が設けられ、溝21に積層形成されるN層2、N−層3、P層4、及びN+層5が溝21を覆うように設けられる。N+層5に、N+基板1に対して垂直方向では一部がN+層5を貫通してP層4表面が露呈され、N+基板1に対して水平方向では一部がN+層5を貫通してP層4側面が露呈するように溝22が設けられ、溝22にP+層6が溝22を覆うように設けられる。N+基板1に対して垂直方向では、N+層5を貫通してP層4表面が露呈され、N+基板1に対して水平方向では、P層4を貫通して一端でN−層3側面が露呈し、他端でN+層5側面が露呈し、P+層6の間及び側面と離間して配置形成される溝23が設けられる。溝23に、トレンチゲート11が溝23を覆うように設けられる。

(もっと読む)

半導体装置及びその製造方法

【課題】MOSFET動作からIGBT動作に切り替わるときのコレクタ電圧を上昇させずに、アバランシェ耐量を向上させる半導体装置を提供する。

【解決手段】P-型基板の表面部に形成されたN型リサーフ領域と、P型ベース領域と、N+型エミッタ/ソース領域105と、ゲート絶縁膜と、N型リサーフ領域内に形成されたN+型ドレイン領域109及びP+型コレクタ領域108と、ゲート絶縁膜上に形成されたゲート電極107と、P+型コレクタ領域108及びN+型ドレイン領域109に電気接続されたコレクタ/ドレイン電極と、N+型エミッタ/ソース領域105に電気接続されたエミッタ/ソース電極と、N型リサーフ領域内であってP型ベース領域及びN+型ドレイン領域109とは離隔しP+型コレクタ領域108の側面と対向して形成された、N型リサーフ領域よりも高いキャリア濃度のバッファ領域114とを備える半導体装置。

(もっと読む)

半導体装置及びその製造方法

【課題】耐圧を向上した半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、第1半導体領域、第2半導体領域、第3半導体領域、第4半導体領域、ゲート領域、ゲート絶縁膜及び電界緩和領域を備える。第1導電形の第1半導体領域は、第1部分と第1方向に延出した第2部分とを有する。第1導電形の第2半導体領域は、第1部分上の第3部分と第2部分と隣接する第4部分とを有する。第2導電形の第3半導体領域は、第3部分上の第5部分と第4部分と隣接する第6部分とを有する。第1導電形の第4半導体領域は、第5部分上で第6部分と隣接する。ゲート領域は、第2半導体領域、第3半導体領域及び第4半導体領域を第2方向に貫通するトレンチ内に設けられる。ゲート絶縁膜は、トレンチ内壁とゲート領域との間に設けられる。第2導電形の電界緩和領域は、第3部分と第5部分との間に設けられ、第3半導体領域よりも不純物濃度が低い。

(もっと読む)

半導体装置及びその製造方法

【課題】耐圧性の維持と低オン抵抗化との両立が可能なLDMOSトランジスタを提供する。

【解決手段】半導体装置は、第1導電型のドリフト拡散領域10と、第2導電型のボディ拡散領域2と、第1導電型のソース拡散領域6と、ドリフト拡散領域10の上部に形成されたトレンチ内に埋め込まれ、ボディ拡散領域2とは離間した位置に形成された絶縁膜14と、ドリフト拡散領域10の上部に形成され、絶縁膜14から見てソース拡散領域6と逆の方向に隣接する第1導電型のドレイン拡散領域7と、ボディ拡散領域2上からドリフト拡散領域10上を越えて絶縁膜14上にまで形成されたゲート電極5とを備えている。また、ドリフト拡散領域10は、基板内部領域11と、基板内部領域11よりも高濃度の第1導電型不純物を含む表面領域12とを有している。

(もっと読む)

非対称スペーサをゲートとして備えるLDMOSトランジスタ

【課題】本発明は、横方向拡散金属酸化物半導体(LDMOS)トランジスタと、これを製造する方法を提供する。

【解決手段】LDMOSトランジスタはp型基板上に形成されたn型エピタキシャル層と、LDMOSトランジスタのゲートとして機能する非対称導体スペーサとを備える。LDMOSトランジスタはまた、非対称導体スペーサの両側のソース領域及びドレイン領域と、イオン注入を非対称導体スペーサに行うことで形成されたチャネル領域とを備える。非対称導体スペーサの高さはソース領域からドレイン領域に向かって増加する。チャネル領域は、基本的に完全に非対称導体スペーサの下に存在し、従来技術のLDMOSトランジスタのチャネル領域の長さよりも短い長さを有する。本発明のLDMOSトランジスタはまた、当該トランジスタの活性領域を囲むフィールド酸化物層と、非対称導体スペーサをn型エピタキシャル層から絶縁する薄い誘電体層とを備える。

(もっと読む)

半導体装置の製造方法

【課題】高耐圧な半導体装置の製造方法を提供する。

【解決手段】半導体層に対してマスクを用いて選択的にイオン注入を行い、半導体層に第1導電型の第1の半導体領域と、前記第1の半導体領域よりも第1導電型不純物濃度が低い第1導電型の第2の半導体領域とを同時に形成する工程と、第1の半導体領域上に第2導電型のソース領域を形成する工程と、第2の半導体領域上であってソース領域との間にゲート電極を挟む位置に第2導電型のドレイン領域を形成する工程と、半導体層におけるゲート電極とドレイン領域との間の表層部にドレイン領域に接しドレイン領域よりも不純物濃度が低い第2導電型のドリフト領域を形成する工程とを備えている。

(もっと読む)

リセスゲート構造を有する絶縁ゲート型炭化珪素ラテラル電界効果トランジスタ

【課題】短チャネル化を可能とし、オン抵抗と寄生容量の低減を図った絶縁ゲート型炭化珪素ラテラル電界効果トランジスタを提供する。

【解決手段】ドリフト領域(5)表面の一部に電界緩和領域(9)を設け、ソース領域(3)とドリフト領域(5)との間に凹部(リセス)(8)を形成したリセスゲート構造を有し、凹部(リセス)(8)底面の両端部近傍にソース領域(3)、ドリフト領域(5)の薄い領域(3a、5a)を設ける。

(もっと読む)

1 - 20 / 82

[ Back to top ]