Fターム[5F140BH49]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース、ドレイン領域及びSD近傍領域 (10,828) | 不純物濃度が規定されているもの (547)

Fターム[5F140BH49]に分類される特許

161 - 180 / 547

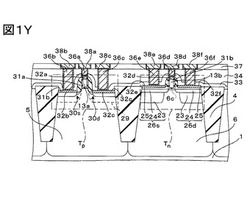

半導体装置及びその製造方法

【課題】歪みの高いキャリア移動領域における寄生抵抗及びエネルギー障壁を小さくするための半導体装置を提供する。

【解決手段】半導体基板1上にゲート絶縁膜7を介して形成されたゲート電極13bと、半導体基板1のうちゲート電極13bの下方に形成されるチャネル領域6cと、チャネル領域6cの両側方に形成され、第1炭素濃度で炭素を含み、第1リン濃度でリンを含む第1の炭化シリコン層23と、第1の炭化シリコン層23上にチャネル領域6cに接合して形成され、第1リン濃度より多い第2リン濃度でリンを含み、第1炭素濃度以下の第2炭素濃度で炭素を含む第2の炭化シリコン層24とを有する。

(もっと読む)

高kゲート誘電体のための、不純物酸素を捕捉する半導体構造および該構造を形成する方法(高kゲート誘電体のための捕捉金属スタック)

【課題】CMOS集積過程での高温処理の後であっても一定の閾値電圧を維持する高kゲート誘電体の提供。

【解決手段】高kゲート誘電体30と、下部金属層40、捕捉金属層50、および上部金属層60を含む金属ゲート構造とのスタックを提供する。該捕捉金属層は、次の2つの基準、1)Si+2/yMxOy→2x/yM+SiO2の反応によるギブス自由エネルギの変化が正である金属(M)であること、2)酸化物形成に対する酸素原子あたりのギブス自由エネルギが、下部金属層の金属および上部金属層の金属より大きな負である金属であること、を満たす。これらの基準を満たす捕捉金属層は、酸素原子がゲート電極を通って高kゲート誘電体に向け拡散するときに該酸素原子を捕捉する。さらに、該捕捉金属層は、高kゲート誘電体の下の酸化ケイ素界面層の厚さを遠隔から低減する。この結果、ゲート誘電体全体の等価酸化膜厚(EOT)の変動が抑制される。

(もっと読む)

半導体装置

【課題】ハイサイド素子として用いても誤動作が少なく、かつ耐圧を高く維持することのできる半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBの内部には、p-エピタキシャル領域EP1が形成されている。p-エピタキシャル領域EP1の主表面側には、p-エピタキシャル領域EP2が形成されている。p-エピタキシャル領域EP2の主表面側には、n型ドリフト領域DRIとp型ボディ領域BOとが形成されている。p-エピタキシャル領域EP1とp-エピタキシャル領域EP2との間には、これらの領域を電気的に分離するためにフローティング電位のn+埋め込み領域NBが形成されている。n+埋め込み領域NBとp-エピタキシャル領域EP2との間には、p-エピタキシャル領域EP2よりも高いp型不純物濃度を有するp+埋め込み領域PBが形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル領域に印加される応力分布のピークとソース領域近傍に発生する電位分布のピークの位置を最適化することで、キャリア速度を向上させて飽和電流特性を向上させることを可能にする。

【解決手段】半導体基板11に形成されたチャネル領域12と、前記チャネル領域12の一方側に形成されたソース領域19と、前記チャネル領域12の他方側に形成されたドレイン領域20と、前記チャネル領域12上にゲート絶縁膜13を介して形成されたゲート電極14と、前記チャネル領域12に応力を印加する第1、第2応力導入層21、23を有し、前記チャネル領域12と前記ソース領域19とのpn接合境界と、前記チャネル領域12と前記ドレイン領域20とのpn接合境界の間に、前記ソース領域19側の応力分布のピークと前記ドレイン領域20側の応力分布のピークが位置する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】突出部の側面が凹凸状とされ、前記側面を覆うようにゲート酸化膜を形成したときに、実効的なチャネル長が増加して、ピラー型MOSトランジスタの電流駆動能力が低下するという課題があった。

【解決手段】基板と、前記基板の一面から垂直方向に突出された突出部7とを備え、突出部7の先端側の上部拡散層と、基端側の下部拡散層と、側面7cを覆うゲート絶縁膜14と、ゲート絶縁膜14を覆うゲート電極15と、を有し、チャネルが前記垂直方向となるピラー型MOSトランジスタ51を具備し、突出部7が平面視八角形状であり、突出部7の側面7cが{100}面からなる4つの主表面8a、8b、8c、8dと、{110}面および{111}面からなり、前記主表面8a、8b、8c、8dよりも面積が小さい4つの副表面9a、9b、9c、9dとからなる半導体装置101を用いることにより、上記課題を解決できる。

(もっと読む)

半導体装置

【課題】横型の電界効果トランジスタを備えた半導体装置であって、素子面積を大きくしても特性が均一な半導体装置を提供する。

【解決手段】第1導電型の半導体層11と、第2導電型のディープウエル12と、第1導電型のウエル13と、前記ウエル内に形成された第2導電型のソース層15と、第2導電型のドレイン層17と、前記ディープウエルの上層部分に形成され、前記ドレイン層に接続される第2導電型のコンタクト層19と、前記ソースドレイン間の領域の直上域に設けられたゲート電極21と、第2導電型のドリフト層18と、を備え、前記ソース層と前記ドレイン層との間に逆バイアス電圧が印加された状態において、前記ソース層と前記ドレイン層との間ではパンチスルーが発生せず、前記ドレイン層と前記ウエルとの間の第1の空乏層と、前記ウエルと前記ディープウエルとの間の第2の空乏層とが前記ウエルと前記ドレイン層の接合耐圧以下で繋がる。

(もっと読む)

半導体素子

【課題】構造が複雑なフィールドプレート構造を用いずに、ゲート電極端での電界集中を緩和することができる半導体素子を提供する。

【解決手段】MOSFET10は、基板上にバッファ層を介して形成されたp−GaN層14と、ゲート絶縁膜15と、ゲート電極20と、ソース電極と、ドレイン電極17とを有する。ゲート電極20は、ゲート電圧を印加するための電極で、ドーパントが高濃度にドーピングされたポリシリコンを用いた第1の領域(ゲート電極1)21と、高抵抗のポリシリコンを用いた第2の領域(ゲート電極2)22とを有する。両ゲート電極21、22間に抵抗勾配部23がある。第2の領域22では緩やかに電位が変化する電位勾配30ができる。これにより、ゲート電極端31において、電圧の微分である電界がピーク32で示すように小さくなり、ゲート電極端31での電界集中を緩和することができる。

(もっと読む)

電界効果トランジスタ

【課題】高いしきい値電圧と大きい動作電流とを両立した電界効果トランジスタを提供すること。

【解決手段】基板と、前記基板上に形成され、窒化物系化合物半導体からなり、チャネル層を含む半導体層と、前記チャネル層上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成されたゲート電極と、前記半導体層上において前記ゲート電極を挟むように配置されたソース電極およびドレイン電極と、を備え、前記チャネル層の表面の、少なくとも前記ゲート電極直下の領域が、窒素極性の表面を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】 低いオン抵抗を維持しつつ、従来構成よりも更に耐圧低下を抑制したLDMOSトランジスタ及びその製造方法を提供する。

【解決手段】 P型基板1上に形成された、N型ウェル2と、ウェル2内に形成されたP型ボディ領域6と、ウェル2内においてボディ領域6よりも深い位置に形成されたP型の埋め込み拡散領域4と、ボディ領域6内に形成されたN型のソース領域9と、ウェル2内において、素子分離領域を介してボディ領域6と離間して形成したN型のドリフト領域7と、ドリフト領域7内に形成されたN型のドレイン領域10と、少なくとも前記ボディ領域9の一部上方、及びボディ領域9とドレイン領域10に挟まれた位置におけるウェル領域2の上方にわたってゲート絶縁膜を介して形成されたゲート電極7と、有し、ドリフト領域7並びにドレイン領域10が、ボディ領域6を取り囲むようにリング状に形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】内部回路の誤動作を誘発させない保護回路を有する半導体装置を提供する。

【解決手段】P型Si基板101と、ESD保護素子1Aと、被保護素子1Bとを備えた半導体装置1であって、ESD保護素子1Aは、ソースN型拡散領域107Aと、P型Si基板101内においてソースN型拡散領域107Aを覆い、ソースN型拡散領域107Aの下方から少なくともゲート電極106Aの下方の一部まで形成され、P型Si基板101の基本領域よりもP型不純物濃度が高い高濃度P型拡散領域103とを備え、被保護素子1Bは、ドレインN型拡散領域108Bと、P型Si基板101内においてドレインN型拡散領域108Bと接する低濃度P型拡散領域104とを備え、ESD保護素子1Aのドレイン電極112Aと被保護素子1Bのドレイン電極112Bとが接続され、高濃度P型拡散領域103は、低濃度P型拡散領域104よりもP型不純物濃度が高い。

(もっと読む)

スレショルド電圧を有する電界効果トランジスタ、及びその製造方法

【課題】相異なるスレショルド電圧を有する電界効果トランジスタを提供する。

【解決手段】ドープ半導体ウエル上に、複数種のゲート・スタック(100〜600)が形成される。ドープ半導体ウエル(22、24)上に、高誘電率(high−k)ゲート誘電体(30L)が形成される。一つのデバイス領域中に金属ゲート層(42L)が形成され、他のデバイス領域(200、400、500、600)ではhigh−kゲート誘電体は露出される。該他のデバイス領域中に、相異なる厚さを有するスレショルド電圧調整酸化物層が形成される。次いで、スレショルド電圧調整酸化物層を覆って導電性ゲート材料層(72L)が形成される。電界効果トランジスタの一つの型は、high−kゲート誘電体部分を包含するゲート誘電体を包含する。電界効果トランジスタの他の型は、high−kゲート誘電体部分と、相異なる厚さを有する第一スレショルド電圧調整酸化物部分とを包含するゲート誘電体を包含する。相異なるゲート誘電体スタックと、同一のドーパント濃度を有するドープ半導体ウエルを用いることによって、相異なるスレショルド電圧を有する電界効果トランジスタが提供される。

(もっと読む)

半導体装置およびその製造方法

【課題】GIDL等の局所的な電界集中により発生するリークおよび短チャネル効果の発生を抑えた半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、半導体基板2上にゲート絶縁膜11を介して形成されたゲート電極12と、半導体基板2中のゲート電極12の両側に形成され、ゲート電極12側のエクステンション領域151とゲート電極12の反対側の深い領域152とを有し、導電型不純物を含むソース・ドレイン領域15と、を有し、ソース・ドレイン領域15のエクステンション領域151は、ゲート電極12側の高拡散領域151aと、最下部の半導体基板2の表面からの深さが高拡散領域151aの最下部の半導体基板2の表面からの深さよりも浅く、高拡散領域151aと深い領域152との間に設けられた低拡散領域151bと、を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】MIPS構造を有する電界効果トランジスタにおいて、金属ゲート電極とポリシリコンゲート電極との接触抵抗を低減することにより、AC動作を向上させる。

【解決手段】半導体装置1は、半導体基板10上に電界効果トランジスタを有する。電界効果トランジスタは、ゲート絶縁膜25、27とゲート電極63、71と、を備える。さらに、ゲート電極63、71は第1金属からなる第1電極層22と、第2金属からなる第2電極層26、34と、シリコン層からなる第3電極層62、70と、を含む積層構造である。第2金属は、シリコン層の多数キャリアに対する第1電極層22と第3電極層62、70とのバンド不連続を緩和する仕事関数を有する材料である。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】コスト増や大型化を招くことなく、耐圧特性に優れた半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体層13と、半導体層13上のゲート電極15、ソース電極16sおよびドレイン領域16dと、を備えたMOSFET1は、半導体層13中であってこの半導体層13の上面および下面それぞれから離間する中間領域に所定の導電性を備えたドーパント(例えばシリコン(Si))を含む縦方向電界緩和領域19を備えている。

(もっと読む)

半導体装置の製造方法

【課題】

製造工程を簡略化しつつ、特性の優れた第1のMOSトランジスタと第2のMOSトランジスタとを製造する半導体装置の製造方法を提供する。

【解決手段】

半導体基板に、第1のMOSトランジスタ領域、第2のMOSトランジスタ領域を画定する素子分離領域を形成し、第1のMOSトランジスタ領域、第2のMOSトランジスタ領域に第1導電型の不純物をイオン注入し、第1導電型のウェルを形成し、第1のMOSトランジスタ領域、第2のMOSトランジスタ領域上に絶縁ゲート電極を形成し、第2のMOSトランジスタのドレイン領域を覆うマスクを介して、半導体基板法線方向から傾いた複数方向から第1導電型の不純物をイオン注入し、第1のMOSトランジスタ領域の前記絶縁ゲート電極下方に対称的なチャネルドーズ領域、第2のMOSトランジスタ領域の前記絶縁ゲート電極下方に非対称なチャネルドーズ領域を形成し、半導体装置を製造する。

(もっと読む)

ソース/ドレインゾーンに沿って調節したポケット部分を具備する非対称的電界効果トランジスタを有する半導体構成体の構成及び製造

【課題】 半導体ボディの上部表面に沿って設けられている非対称的絶縁ゲート電界効果トランジスタ(100U又は102U)は、該トランジスタボディ物質のチャンネルゾーン(244又は284)によって横方向に分離された第1及び第2ソース/ドレインゾーン(240及び242又は280及び282)を包含している。

【解決手段】 ゲート電極(262又は302)がチャンネルゾーン上方でゲート誘電体層(260又は300)の上側に位置している。該ボディ物質の横方向に隣接した物質よりも一層高度にドープした該ボディ物質のポケット部分(250又は290)が該S/Dゾーンの内のほぼ第1のもののみに沿って該チャンネルゾーン内に延在している。該ポケット部分の垂直ドーパント分布は、互いに離隔されている夫々の位置(PH−1乃至PH−3)において複数個の局所的最大(316−1乃至316−3)に到達すべく調節されている。該調節は、典型的に、該ポケット部分の垂直方向ドーパント分布が上部半導体表面近くで比較的平坦であるように実施される。その結果、該トランジスタのリーク電流は減少されている。

(もっと読む)

ソース/ドレイン延長部、ハローポケット及びゲート誘電体厚さの異なる構成を有する同極性の電界効果トランジスタの構成及び製造

【課題】 一群の高性能同極性絶縁ゲート電界効果トランジスタ(100,108,112,116,120及び124又は102,110,114、118,112及び126)が、アナログ及び/又はデジタル適用例用の広く多様なトランジスタを提供する半導体製造プラットフォームに適した横方向ソース/ドレイン延長部、ハローポケット、及びゲート誘電体厚さの選択可能な異なる構成を有している。

【解決手段】 各トランジスタは、一対のソース/ドレインゾーン、ゲート誘電体層、及びゲート電極を有している。各ソース/ドレインゾーンは主要部分及び一層軽度にドープした横方向延長部を有している。該トランジスタの内の一つのソース/ドレインゾーンの内の一つの横方向延長部が該トランジスタの別のもののソース/ドレインゾーンの内の一つの横方向延長部よりも一層高度にドープされており又は/及びそれよりも上部半導体表面下側により少ない深さに延在している。

(もっと読む)

電界効果トランジスタのソース延長部及びドレイン延長部が異なるドーパントで画定される半導体構成体の構成及び製造

【課題】 半導体ボディの上部表面に沿って設けられた絶縁ゲート電界効果トランジスタ(100)は、チャンネルゾーン(244)によって横方向に分離された一対のソース/ドレインゾーン(240及び242)を有している。

【解決手段】 ゲート電極(262)が該チャンネルゾーン上方でゲート誘電体層(260)の上側に存在している。各ソース/ドレインゾーンは、主要部分(204M又は242M)及び該主要部分と横方向に連続的であり且つ該ゲート電極下側を横方向に延在する一層軽度にドープした横方向延長部(240E又は242E)を包含している。該横方向延長部は、該チャンネルゾーンを上部半導体表面に沿って終端させており、異なる原子量の一対の半導体ドーパントによって夫々ほぼ画定される。該トランジスタが非対称的装置であり、該ソース/ドレインゾーンはソース及びドレインを構成する。該ソースの横方向延長部は該ドレインの横方向延長部よりも一層軽度にドープされており且つ一層高い原子量のドーパントで画定される。

(もっと読む)

延長型ドレイン電界効果トランジスタを有する半導体構成体の構成及び製造

【課題】 拡張型ドレイン絶縁ゲート電界効果トランジスタ(104又は106)が、第1ウエル領域(184A又は186A)の一部によって構成されているチャンネル(322又は362)ゾーンによって横方向に分離されている第1及び第2ソース/ドレインゾーン(324及び184B又は364及び186B/136B)を包含している。

【解決手段】 ゲート誘電体層(344又は384)が該チャンネルゾーンの上側に存在している。該第1ソース/ドレインゾーンは、通常は、ソースである。通常はドレインである該第2S/Dゾーンは、少なくとも部分的には第2ウエル領域(184B又は186B)で構成されている。該半導体ボディのウエル分離部分(136A又は212U/136B)が該ウエル領域の間を延在しており且つ各ウエル領域よりも一層軽度にドープされている。該ウエル領域の構成は、該半導体ボディのIGFETの部分における最大電界をして上部半導体表面の十分に下側、典型的には該ウエル領域同士が互いに最も近い箇所におけるか又はその近くで発生させる。該IGFETの動作特性は動作時間と共に安定である。

(もっと読む)

電界効果トランジスタ

【課題】耐圧性が高い電界効果トランジスタを提供すること。

【解決手段】p型の導電型を有する基板と、前記基板上に形成された高抵抗層と、前記高抵抗層上に形成され、p型の導電型を有するp型半導体層を前記基板側に配置したリサーフ構造を有する半導体動作層と、前記半導体動作層上に形成されたソース電極、ドレイン電極、およびゲート電極と、を備える。好ましくは、前記リサーフ構造は、前記p型半導体層上に形成されたn型の導電型を有するリサーフ層を備える。また、好ましくは、前記リサーフ構造は、前記p型半導体層上に形成されたアンドープのキャリア走行層と、前記キャリア走行層上に形成され該キャリア走行層とはバンドギャップエネルギーが異なるキャリア供給層とを備える。

(もっと読む)

161 - 180 / 547

[ Back to top ]