Fターム[5F140BH49]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース、ドレイン領域及びSD近傍領域 (10,828) | 不純物濃度が規定されているもの (547)

Fターム[5F140BH49]に分類される特許

141 - 160 / 547

半導体装置およびその製造方法

【課題】トランジスタの耐圧を高く保ちつつ、素子分離能力の低下を防ぐ。

【解決手段】基板102の一面のチャネル領域108において、ゲート幅方向に断続的に深さが変化するように形成されたトレンチ162内部を埋め込むように形成されたゲート電極122を含むトランジスタにおいて、ソース領域112およびドレイン領域113の下方には、それぞれ第1のオフセット領域106および第2のオフセット領域107が形成される。ここで、第1のオフセット領域106および第2のオフセット領域107は、それぞれ、素子分離絶縁膜110と接する領域における下端が素子分離絶縁膜110の下端よりも上方に位置するように形成されるとともに、トレンチ162端部の下方にも形成されている。

(もっと読む)

半導体装置とその製造方法

【課題】SiGe層を用いてPチャネル型トランジスタのチャネル形成領域に圧縮応力を印加すると共に、リーク電流を低減する。

【解決手段】半導体装置120は、半導体基板100の表面部に形成されたソース領域及びドレイン領域122と、これらに挟まれたチャネル形成領域上にゲート絶縁膜101を介して形成されたゲート電極102とを含むPチャネル型トランジスタを備える。ゲート電極102の両側それぞれにおいて半導体基板100にリセスが形成され、リセスに、SiGeからなる第1エピタキシャル層111と、その上に形成され且つSiからなる第2エピタキシャル層112と、その上に形成され且つSiGeからなり、チャネル形成領域を挟む第3エピタキシャル層113とを備える。ソース領域及びドレイン領域122は、第3エピタキシャル層113中に形成され、且つ、それぞれの接合深さがいずれも第3エピタキシャル層133の深さよりも浅い。

(もっと読む)

埋め込みストレッサを有する高性能FETを形成するための方法および構造

【課題】 高性能の半導体構造およびかかる構造を製造する方法を提供する。

【解決手段】 半導体構造は、半導体基板12の上面14上に位置する、例えばFETのような少なくとも1つのゲート・スタック18を含む。構造は更に、少なくとも1つのゲート・スタックのチャネル40上にひずみを誘発する第1のエピタキシ半導体材料34を含む。第1のエピタキシ半導体材料は、少なくとも1つのゲート・スタックの対向側に存在する基板内の1対のくぼみ領域28の実質的に内部で少なくとも1つのゲート・スタックの設置場所に位置する。くぼみ領域の各々において第1のエピタキシ半導体材料の上面内に拡散拡張領域38が位置する。構造は更に、拡散拡張領域の上面上に位置する第2のエピタキシ半導体材料36を含む。第2のエピタキシ半導体材料は、第1のエピタキシ半導体材料よりも高いドーパント濃度を有する。

(もっと読む)

半導体装置

【課題】高耐圧で大きな電流駆動能力をもつLOCOSオフセット型MOS型電界効果トランジスタを提供する。

【解決手段】LOCOSオフセット型MOS型電界効果トランジスタのドレイン側のオフセット領域に、LOCOS酸化膜を伴うN型第1低濃度ドレインオフセット領域5と、LOCOS酸化膜を伴わないN型第2低濃度ドレインオフセット領域6を設け、共にゲート電極で覆うように設けたので、N型第1低濃度ドレインオフセット領域5でオフセット領域にかかる電界を緩和し高耐圧を得て、N型第2低濃度ドレインオフセット領域6でオフセット領域のキャリアを増加させ大きな電流駆動能力を得ることができる。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極に対する不純物の突き抜けを抑止する。

【課題を解決するための手段】半導体装置の製造方法は、基板上方に成膜した多結晶シリコンをエッチングして基板の第1領域上方に第1ゲート電極を形成し、基板の第2領域上方に第2ゲート電極を形成し、第1領域及び第1ゲート電極を覆う第1パターンを形成し、第2ゲート電極及び第1パターンをマスクにして第2領域に第1不純物を第1ドーズ量で注入して第2領域に第1エクステンション領域を形成し、第1ゲート電極、第1領域及び第2ゲート電極の上面を露出させた第2パターンを形成し、第1エクステンション領域を覆い、第1ゲート電極、第2ゲート電極及び第2パターンをマスクにして第1領域に第2不純物を第1ドーズ量よりも多いドーズ量で注入して第1領域に第2エクステンション領域を形成するとともに、第1ゲート電極及び第2ゲート電極の少なくとも上部をアモルファス化する。

(もっと読む)

トレンチDMOSトランジスタの製造方法

トレンチDMOSトランジスタの製造方法であって、半導体基板上に酸化物層及びバリア層を形成するステップと、トレンチを形成するために、酸化物層及び半導体基板をエッチングするステップと、トレンチの内壁にゲート酸化物層を形成するステップと、バリア層上にポリシリコン層を形成し、トレンチを充填するステップと、トレンチゲートを形成するために、ポリシリコン層をエッチバックするステップと、バリア層及び酸化物層を除去するステップと、拡散層を形成するために、トレンチゲートの両側の半導体基板内にイオンを注入するステップと、拡散層上をフォトレジスト層で覆い、ソース/ドレイン配置を定義するステップと、拡散層内にイオンを注入するステップと、トレンチゲートの両側に側壁を形成するステップと、拡散層及びトレンチゲート上に金属シリサイド層を形成するステップとを含む。低コスト及び改善された製造効率を伴う効果的な結果が達成される。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 ゲートとドレインの間で生じる電界集中を緩和する半導体装置を提供する。

【解決手段】本発明によれば,半導体基板上にゲート絶縁膜を介して形成された第1のゲート電極と、前記半導体基板上に前記ゲート絶縁膜を介して形成され、かつ、第1のゲート電極の側面に絶縁性のスペーサを介して配置された第2のゲート電極と、第1及び第2のゲート電極を挟むように前記半導体基板上に形成されたソース領域及びドレイン領域と、第1のゲート電極下方における前記半導体基板の一部の領域を挟むように形成され、第2のゲート電極及び前記ソース領域及びドレイン領域と重なるように形成された電界緩和領域と、を備える半導体装置が提供される。

(もっと読む)

半導体装置

【課題】 半導体装置に関し、ソース・ドレイン領域を実効的に埋込Si混晶層で構成する際の電気的特性を向上する

【解決手段】 一導電型シリコン基体と、一導電型シリコン基体上に設けたゲート絶縁膜と、ゲート絶縁膜の上に設けたゲート電極とゲート電極の両側の一導電型シリコン基体に設けた逆導電型エクステンション領域と、逆導電型エクステンション領域に接するとともに、一導電型シリコン基体に形成された凹部に埋め込まれた逆導電型Si混晶層とを備えた半導体装置であって、逆導電型Si混晶層が、第1不純物濃度Si混晶層/第2不純物濃度Si混晶層/第3不純物濃度Si混晶層を有し、第2不純物濃度を第1不純物濃度及び第3不純物濃度よりも高くする。

(もっと読む)

半導体装置

【課題】ドレイン端での電流集中を防止して静電放電に対する耐性に優れた半導体装置を提供する。

【解決手段】保護素子1は、MOS構造のデバイスの一部に、縦型バイポーラトランジスタQ1と寄生バイポーラトランジスタQ2とを形成した構造になっている。N+ドレイン領域3とゲート直下のチャネル領域4との間にはNドリフト領域5が形成されている。N+ソース領域6に隣接してP+ベースコンタクト領域7が形成されている。ソース側に縦型トランジスタQ1を形成して、静電放電時に発生したホール電流を縦型トランジスタQ1に流すようにしたため、N+ドレイン領域のベース側端部での電流集中を緩和できる。

(もっと読む)

電界効果トランジスタの製造方法

【課題】高集積度化でき、電気射特性を維持しながら、低コスト化できる電界効果トランジスタの製造方法を実現する。

【解決手段】誘電性絶縁部層2’によって被覆されているバルクシリコンウエハ基板1’上に島状の各活性エリア10を互いに隣り合うようにそれぞれ設定する。バルクシリコンウエハ基板1’の表面上において、各活性エリア10を電界効果トランジスタの本体領域をフィン部3、5の形状で突出するように露出させて形成するために、誘電性絶縁部層2’を厚さ方向にエッチバックして絶縁体層2を形成する。上記本体領域に、チャネル領域部、上記チャネル領域部上のゲート誘電体8、ゲート誘電体8上のゲート電極4、および、ゲート電極4の自己整合マスクにより、チャネル領域部とは反対の伝導性型である不純物原子のドープによりソース領域部5およびドレイン領域部3を形成する。

(もっと読む)

半導体装置

【課題】寄生容量を増やさずにソフトエラー率を低減することのできる半導体装置を提供する。

【解決手段】半導体基板の主表面に形成された第1導電型ウェルと、第1導電型ウェルの表面に形成されたトランジスタと、半導体基板の主表面に形成された素子分離絶縁領域と、第1導電型ウェルの表面に前記トランジスタと素子分離絶縁領域を隔てて形成され、底面の深さがおおよそ当該素子分離絶縁領域の底面と等しく、第1導電型ウェルより不純物濃度が高い第1導電型高濃度領域と、第1導電型高濃度領域の表面に形成されたウェルコンタクト電極と、を備える。

(もっと読む)

リセスゲート構造を有する絶縁ゲート型炭化珪素ラテラル電界効果トランジスタ

【課題】短チャネル化を可能とし、オン抵抗と寄生容量の低減を図った絶縁ゲート型炭化珪素ラテラル電界効果トランジスタを提供する。

【解決手段】ドリフト領域(5)表面の一部に電界緩和領域(9)を設け、ソース領域(3)とドリフト領域(5)との間に凹部(リセス)(8)を形成したリセスゲート構造を有し、凹部(リセス)(8)底面の両端部近傍にソース領域(3)、ドリフト領域(5)の薄い領域(3a、5a)を設ける。

(もっと読む)

リセスゲート型炭化珪素電界効果トランジスタおよびその製造方法

【課題】短ゲート(チャネル)化しても短チャネル効果を抑制し、オン抵抗の低いSiC MISFETを得る。

【解決手段】一導電型のSiC半導体領域(2)内にソース、ドレイン領域(3、4)を形成し、ソース、ドレイン領域で挟まれたSiC半導体領域部分に形成され、ソース、ドレイン領域に接する二つの側面と両側面を接続する底面とからなる所定深さの凹部(リセス)(5)を形成し、凹部底面の両端近傍に隣接するソース、ドレイン領域の一部(3a、4a)を他の部分より薄くしたSiC MISFET。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置及びその製造方法に関し、高誘電率膜を用いた相補型トランジスタの実効仕事関数を調整して適切なしきい値電圧を実現する際に、エッチング工程数を低減するとともに、エッチングダメージの発生を回避する。

【解決手段】 nチャネル絶縁ゲートトランジスタのSiO2より誘電率の高い第1のゲート絶縁膜と第1金属ゲート電極との間にアルミニウム膜を設けるとともに、pチャネル絶縁ゲートトランジスタのSiO2より誘電率の高い第2ゲート絶縁膜と第2金属ゲート電極との間に酸化アルミニウム膜を設ける。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】微細なトレンチを採用するトレンチDMOSFETにおいて、ドレイン−ソース間の絶縁破壊電圧を高くするため、低濃度のドリフト層の形成領域を如何に確保するかが課題となる。

【解決手段】TNDMOS形成のためのトレンチT1の底部のN型ウエル層2の表面から内部に延在し、P型ボディ層3と接続するN型埋め込みドリフト層5を形成する。次にトレンチT1の両側壁にゲート電極7a、スペーサー8aを重畳して形成する。次に、ゲート電極7a及びスペーサー8aをマスクとしてリン等をイオン注入しN型埋め込みドリフト層5内にN+型ドレイン層11を形成する。これによりN+型ドリフト層11からP型ボディ層3底部まで延在する低濃度のN型埋め込みドリフト層5を確保する。なお、N+型ドレイン層11を形成しないで、トレンチT1の両側壁に、N型埋め込みドリフト層5を共通のドレイン層とする2つのTDMOSを形成しても良い。

(もっと読む)

半導体装置およびその製造方法

【課題】低オン抵抗かつ高耐圧で高速スイッチング可能な半導体装置をキャリアのライフタイムコントロールの為の格子欠陥を形成していない半導体基板で実現する。

【解決手段】P型Siからなる基板1の表面部に形成されたN型不純物層であるリサーフ領域2と、P型不純物層であるベース領域3と、高濃度のN型不純物層であるエミッタ/ソース領域8と、リサーフ領域2内に形成された低濃度のP型不純物層であるコレクタ領域4と、コレクタ領域4に隣接して形成され別断面に位置する高濃度のN型不純物層であるドレイン領域と、高濃度のP型不純物層であるベース接続領域10と、ゲート絶縁膜6と、ゲート電極7とからなる横型ハイブリットIGBTにおいて、コレクタ領域4が別断面に位置するドレイン領域よりも浅く形成されている。

(もっと読む)

不揮発性半導体記憶装置及びディプレッション型MOSトランジスタ

【課題】トランジスタの耐圧を向上し、動作信頼性を向上出来る不揮発性半導体記憶装置及びディプレッション型MOSトランジスタを提供すること。

【解決手段】ゲート電極26と、第1不純物濃度を有するチャネル領域22と、第1不純物濃度よりも大きな第2不純物濃度を有するソース・ドレイン拡散領域21と、チャネル領域22とソース・ドレイン拡散領域21とが重複する領域に形成され、第2不純物濃度よりも大きな第3不純物濃度を有する重複領域24と、第2不純物濃度よりも大きな第4不純物濃度を有するコンタクト領域23と、ソース・ドレイン拡散領域21の一部領域内に形成され、第2不純物濃度よりも大きく且つ第4不純物濃度よりも小さい第5不純物濃度を有する不純物拡散領域27とを備え、不純物拡散領域27は、コンタクト領域23に接し且つ重複領域24に離隔するようにして形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】閾値バラつきが小さく、特性変動の少ない半導体装置およびその製造方法を提供する。

【解決手段】エピタキシャル成長法を用いた選択再成長によりゲート領域以外のAlGaN層を厚くするリセス構造のノーマリーオフ型の窒化物半導体装置において、トラップ準位の多い、エピタキシャル成長層と選択再成長層との界面に高濃度ドープ層5またはプレーナドーピング層52を設ける。

(もっと読む)

半導体装置およびその製造方法

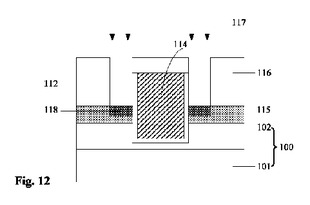

【課題】トレンチゲート構造を有するトランジスタにおいて、サブスレッショルド特性を良好にする。

【解決手段】半導体装置100は、第1導電型のソース領域112およびドレイン領域113、これらの間に第2導電型のチャネル領域108が形成された基板102と、チャネル領域108において、ゲート幅方向に断続的に深さが変化するように形成されたトレンチ162を埋め込むように形成されたゲート電極122とを有するトランジスタを含む。チャネル領域108において、基板102表面およびトレンチ162の底部には、それぞれ第2の高濃度領域132および第1の高濃度領域130が形成されており、第2導電型の不純物濃度がトレンチ162側方における第2導電型の不純物濃度よりも高くなっている。また、第1の高濃度領域130の第2導電型の不純物濃度が第2の高濃度領域132の第2導電型の不純物濃度以上である。

(もっと読む)

半導体装置の製造方法

【課題】チャネルに大きな歪を生じさせることができ、制御を容易に行うことができる半導体装置の製造方法を提供する。

【解決手段】半導体基板1上に、絶縁膜3、多結晶シリコン膜4及びアモルファスシリコン膜5を含む積層体を、ゲート電極の平面形状に形成する。多結晶シリコン膜4及びアモルファスシリコン膜5の側方にサイドウォール6を形成する。サイドウォール6をマスクとして半導体基板1の表面にp型不純物を導入して不純物導入領域7を形成する。サイドウォール6をマスクとして不純物導入領域7の表面に溝8を形成する。溝8内にSiGe層9を選択成長させる。アモルファスシリコン膜5を選択的に除去して、多結晶シリコン膜4を露出する。多結晶シリコン膜4上に導電層11を形成する。

(もっと読む)

141 - 160 / 547

[ Back to top ]