Fターム[5F140BH49]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース、ドレイン領域及びSD近傍領域 (10,828) | 不純物濃度が規定されているもの (547)

Fターム[5F140BH49]に分類される特許

121 - 140 / 547

半導体装置及びその製造方法

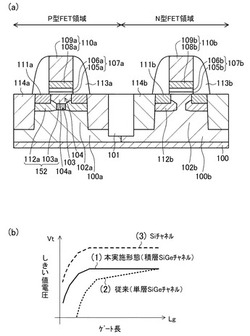

【課題】Geを含む半導体で構成されるチャネル領域を有するP型FETにおいて、逆短チャネル特性の発生を抑制しつつ、短チャネル特性を改善する。

【解決手段】半導体装置は、半導体基板100上に形成されたP型FETを備えている。P型FETは、半導体基板100上に形成され、Geを含有する第1の半導体層103と、第1の半導体層103上に形成され、第1の半導体層103よりも低濃度のGeを含有する第2の半導体層104と、第2の半導体層104上にゲート絶縁膜107aを間に挟んで形成されたゲート電極110aと、第2の半導体層104のうちゲート電極110aの両側方に位置する部分に形成されたp型エクステンション領域111aと、第1の半導体層103内に設けられ、且つp型エクステンション領域111aの下に形成されたn型不純物領域152とを有している。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】エピタキシャル成長を行わなくても素子形成が行え、かつ、バンチングが発生することを防止できるようにする。

【解決手段】エピタキシャル成長を行わず、素子を構成する各領域をイオン注入のみによって形成すると共に、SiC基板1としてオフ角を有しないオン基板を用いる。これにより、イオン注入領域を活性化するための熱処理によってバンチングが発生しないようにできる。したがって、エピタキシャル成長を行わなくても素子形成が行え、かつ、バンチングが発生することを防止できるSiC半導体装置とすることができる。

(もっと読む)

半導体装置、および、半導体装置の製造方法

【課題】チャネル領域に強い歪みを印加することによりデバイス特性を改善した半導体装置を提供すること。

【解決手段】半導体基板1と、半導体基板1の第1の面に形成されたゲート絶縁膜2と、ゲート絶縁膜2の上に形成されたゲート電極3と、ゲート電極3の側壁に形成されたゲート側壁絶縁膜4と、ゲート電極3の下の半導体基板1中に形成されるチャネル領域に隣接し、不純物が注入されたソース/ドレイン拡散層領域5、6と、ゲート電極3の上方を除き、ソース/ドレイン拡散層領域5、6の上に形成された応力印加膜8と、を有し、半導体基板1の第1の面におけるソース/ドレイン拡散層領域5、6が形成された領域には、凹部または凸部50、51、60、61が設けられている半導体装置を提供する。

(もっと読む)

半導体装置およびその製造方法

【課題】短チャネル効果の発生を抑制できる半導体装置及びその製造方法の提供。

【解決手段】本発明の半導体装置は、半導体基板1の活性領域上にゲート絶縁膜5aを介して形成されたゲート電極105と、ゲート電極105側面を覆う第1絶縁膜サイドウォール5bと、ゲート電極105を挟んで形成されたソース領域108S及びドレイン領域108Dにおいて、側面が第1絶縁膜サイドウォール5bに接して半導体基板1上面に形成されたシリコン層109と、第1絶縁膜サイドウォール5bを介してゲート電極105側面と対向し、底面がシリコン層109上面に接して形成された第2絶縁膜サイドウォール5dと、シリコン層109内下層部に設けられたLDD不純物層109aと、シリコン層109内上層部に設けられた高濃度不純物層109bと、LDD不純物層109aの下方、半導体基板1の表面側に形成されたポケット不純物層108aとを具備する。

(もっと読む)

電界効果トランジスタ

【課題】蛇行した形状に形成されたリセス部を備えることにより、オン抵抗を低減することができる電界効果トランジスタを提供することを目的とする。

【解決手段】電界効果トランジスタ1は、チャネル層11と、チャネル層11とヘテロ接合を構成するキャリア供給層12と、キャリア供給層12の表面から掘り下げて形成されたリセス部13と、リセス部13に沿って形成された第1絶縁層31と、第1絶縁層31の上に形成された第1ゲート電極23と、リセス部13に対してチャネル長方向の一方側に形成されたソース電極21と、リセス部13に対してチャネル長方向の他方側に形成されたドレイン電極22とを備える。リセス部13は、ソース電極21とドレイン電極22とが平面視で平行に対向するチャネル長の範囲内において、蛇行しながらチャネル長方向と交差する方向に延長されている。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル層の厚みのバラツキを抑制できるJFET、MOSFETもしくはMESFETを備えた半導体装置およびその製造方法を提供する。

【解決手段】n+型層3に対して異方性エッチングを行うことによって凹部4を形成したのち、この凹部4内にエピタキシャル成長させることによってn型チャネル層5を形成する。これにより、n型チャネル層5を一定の膜厚かつ一定の濃度で形成することが可能となる。このため、従来の構造と異なり、n型チャネル層5の膜厚が一定なバラツキのない構造とすることが可能となる。したがって、JFETの特性も一定とすることが可能となる。

(もっと読む)

高耐圧MOSトランジスタおよび半導体集積回路装置、高耐圧半導体装置

【課題】半導体基板上に他のCMOS素子と集積して形成される高耐圧MOSトランジスタの、工程数を抑制しながら、ドレイン耐圧特性を向上させる。

【解決手段】半導体基板21と、ゲート電極23と、第2の導電型のソース領域21Sと、第2の導電型のドレイン領域21Dと、ソースエクステンション領域21aと、ドレインエクステンション領域21bと、を含み、ソースエクステンション領域21aとドレインエクステンション領域21bとの間にはチャネル領域が形成され、ソース領域21Sおよびソースエクステンション領域21aの下方には第1のウェル21PWが、第1の導電型で、素子分離領域21Iの下端部を超える深さで形成され、第1のウェル21PWの下方には第2のウェル21DNWが第2の導電型で形成され、第1のウェル21PWおよび第2のウェル21DNWは、ドレインエクステンション領域21b、ドレイン領域21Dの下には形成されない。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの高耐圧特性を維持しながらオン抵抗を低減する。

【解決手段】第1高濃度拡散層109及び第2高濃度拡散層108はそれぞれ第1導電型であり、平面視においてゲート電極106を介して互いに対向している。第1低濃度拡散層103は第1導電型であり、第1高濃度拡散層109を内側に含むように形成されている。第1高濃度拡散層109は、平面視でゲート電極106から離間しており、第1低濃度拡散層103は、平面視において第1高濃度拡散層109よりもゲート電極の近くまで形成されている。第1埋込層114は第1導電型であり、第1高濃度拡散層109の下方からゲート電極106に向けて延在している。第2埋込層112は第1導電型であり、第1埋込層114とゲート電極106とを接続している。

(もっと読む)

高移動度チャネル(High−MobilityChannels)を有する装置のソース/ドレイン工学

【課題】高移動度チャネルを有する装置のソース/ドレイン工学を提供する。

【解決手段】集積回路構造は、基板及び基板の上方のチャネルを備える。チャネルは、III族元素とV族元素から構成される第一III-V族化合物半導体材料からなる。ゲート構造はチャネルの上方に設置される。ソース/ドレイン領域はチャネルに隣接し、本質的に、シリコン、ゲルマニウム、及び、それらの組み合わせからなる群から選択されるドープされたIV族半導体材料から形成されるIV族領域を含む。

(もっと読む)

半導体装置、半導体集積回路装置及び半導体装置の製造方法

【課題】高耐圧且つ低オン抵抗な半導体装置及びこれを含む半導体集積回路装置を歩留まり良く、安価に提供する。

【解決手段】第1導電型の半導体基板(1)と、前記第1導電型と反対の第2導電型であって前記半導体基板の表面側に形成されたソース領域(11)、低濃度ドレイン領域(12)及び高濃度ドレイン領域(13)と、前記半導体基板上に形成されたゲート絶縁膜(14)と、前記ゲート絶縁膜上に形成されたゲート電極と、を備える半導体装置(10)であって、

前記ゲート電極は、前記低濃度ドレイン領域の少なくとも一部を覆うように形成され、且つ、前記低濃度ドレイン領域の上方において開孔(16)を有することを特徴とする半導体装置。前記低濃度ドレイン領域と高濃度ドレイン領域とは互いに隣接することが好ましい。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】縦型MOSトランジスタを備えた半導体装置を形成する際のゲート電極とコンタクトプラグとの短絡を防止することが可能な半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、前記半導体基板上にシリコン窒化膜(SiN膜)からなるマスク窒化膜のパターンを形成したのちに、溝および半導体ピラーを前記半導体基板に形成する第一工程と、前記マスク窒化膜を残存させたまま、前記溝を覆うゲート絶縁膜を形成したのちに前記半導体ピラーよりも低い高さのゲート電極を形成する第二工程と、前記溝を覆うように、シリコン酸窒化膜(SiON膜)からなるライナー膜を形成したのちに、前記ライナー膜上を覆い、かつ、前記溝内を充填するように層間膜(SOD膜)を形成する第三工程と、前記マスク窒化膜をエッチングにより選択的に除去する第四工程と、を採用する。

(もっと読む)

半導体装置とその製造方法

【課題】高耐圧で、特性の優れた半導体装置を提供する。

【解決手段】素子分離領域STIと、ウェルPWと、活性領域を横断するゲート電極Gと、ゲート電極の一方の側からゲート電極下方に入り込んで形成された低濃度ドレイン領域LDDと、ゲート電極の他方の側からゲート電極下方に入り込み、低濃度ドレイン領域とオーバーラップし、低濃度ドレイン領域より浅い、チャネル領域CHと、ゲート電極の他方の側に形成されたソース領域Snと、ゲート領域の一方の側に、ゲート電極から離間したドレイン領域Dnと、を有し、ゲート電極と高濃度ドレイン領域Dnとの間の中間領域の実効不純物濃度は、オーバーラップ領域の不純物濃度より高い。

(もっと読む)

シリコン選択エッチ方法

基板上に設けられるシリコン層をエッチングする方法は、シリコン層に第1のトレンチを異方性エッチングすること;第1のトレンチ内のシリコン表面を選択的に異方性ウェットエッチングすることであって、該ウェットエッチングが、シリコン表面を、芳香族トリ(低級)アルキル第四級オニウム水酸化物と、非対称テトラアルキル第四級ホスホニウム塩とを含む水性組成物に曝すことを含み、該ウェットエッチングが、シリコン層の(110)面及び(100)面をおよそ等しい速度で(111)面よりも優先的にエッチングして、(111)面に側壁を有する拡大されたトレンチを形成する、選択的に異方性ウェットエッチングすることを含む。応力をシリコン層の少なくとも一部分に導入するプロセスの一環として、このようにして作製したトレンチ内にシリコン合金をエピタキシャル堆積させてもよい。 (もっと読む)

半導体ヘテロ電界効果トランジスタ

【課題】ピエゾ電界により発生するシートキャリアの利用とチャネル部におけるピエゾ電界により深いディプレッション形成の抑制とを提供できる半導体ヘテロ電界効果トランジスタを提供する。

【解決手段】第1及び第3の領域23a、23cの主面24a、24cの法線ベクトルNV1、NV3は、該III族窒化物半導体のc軸Cxに直交する面に対して有限な角度で傾斜する。第2の領域23bの主面24bの法線ベクトルNV2は、該III族窒化物半導体のc軸Cxに直交する面に沿って延在する。第2の領域23bにおけるチャネル層25の第2の領域25bのピエゾ分極PZC2は、III族窒化物半導体領域23からバリア層27への方向に向いている。第1及び第3の領域23a、23cにおけるチャネル層25の第1及び第3の領域25a、25cのピエゾ分極PZC1、PZC3は、バリア層27からIII族窒化物半導体領域23への方向に向いている。

(もっと読む)

半導体装置の製造方法

【課題】RC型トランジスタのチャネル領域の高さを所望の範囲に調整するとともに、前記チャネル領域に近接して残存する薄皮状のバリ部を完全に除去して、半導体装置を製造するという課題があった。

【解決手段】半導体基板1の一面に、溝部と、溝部に囲まれ、側壁面の少なくとも一部が傾斜面である凸部39とを形成してから、溝部を埋める素子分離用絶縁膜を形成する第1工程と、素子分離用絶縁膜をマスクの一部にして半導体基板1の一面をドライエッチングして凸部39内に凹部27を設けるとともに、凹部27と素子分離用絶縁膜との間にチャネル領域4となる薄肉部41を形成する第2工程と、ウェットエッチングにより、薄肉部41の高さを調整する第3工程と、を有する半導体装置の製造方法を用いることにより、上記課題を解決できる。

(もっと読む)

半導体装置およびその製造方法

【課題】ホットキャリアの発生を大幅に抑制して、トランジスタの長期信頼性を高める。

【解決手段】基板102の一面のチャネル領域108において、ゲート幅方向に断続的に深さが変化するように形成されたトレンチ162内部を埋め込むように形成されたゲート電極122を含むトランジスタにおいて、ソース領域112およびドレイン領域113の下方には、それぞれ第1のオフセット領域106および第2のオフセット領域107が形成される。ここで、第2のオフセット領域107は、ゲート長方向の断面において第2のオフセット領域107とチャネル領域108とのPN境界線のトレンチ162底部の角部を始点としたソース領域112に向けた横方向の距離をx、トレンチ162底部の角部を始点とした下方向の距離をyとして、合計距離x+yが0.1μm以上である。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】高電圧を印加しても壊れにくい電界効果トランジスタを提供する。

【解決手段】電界効果トランジスタは、基板1、チャネル層3及びバリア層4と、バリア層4上にこの順で離間して設けられたソース電極6、ゲート電極7およびドレイン電極8とを備え、ソース電極6の直下に第1のn型不純物拡散領域12が設けられ、ドレイン電極8の直下に第2のn型不純物拡散領域13が設けられ、第2のn型不純物拡散領域の下側の前記チャネル層3および第2のn型不純物拡散領域の前記ゲート電極側の前記チャネル層3および前記バリア層4に第3のn型不純物拡散領域15が設けられる。第3のn型不純物拡散領域15は第2のn型不純物拡散領域13よりも低いn型不純物濃度を有し、ゲート電極とドレイン電極との間に電圧が印加されたときバリア層4およびチャネル層3においてその絶縁破壊強度を超える電界集中が生じることを抑制する。

(もっと読む)

半導体装置およびその製造方法

【課題】複数のトレンチを含むトレンチゲート構造のトランジスタにおける特性ばらつきを低減する。

【解決手段】トレンチゲート構造を有するトランジスタを含む半導体装置100において、ゲート幅方向において、複数のトレンチ162は、両側方に形成された素子分離絶縁膜110とそれぞれ接して形成されたトレンチ162aおよびトレンチ162bを含み、トレンチ162aおよびトレンチ162bのゲート幅方向の幅が、これらの間に形成された他のトレンチ162cのゲート幅方向の幅以上となるように形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】トランジスタの耐圧を高く保ちつつ、素子分離能力の低下を防ぐ。

【解決手段】基板102の一面のチャネル領域108において、ゲート幅方向に断続的に深さが変化するように形成されたトレンチ162内部を埋め込むように形成されたゲート電極122を含むトランジスタにおいて、ソース領域112およびドレイン領域113の下方には、それぞれ第1のオフセット領域106および第2のオフセット領域107が形成される。ここで、第1のオフセット領域106および第2のオフセット領域107は、それぞれ、素子分離絶縁膜110と接する領域における下端が素子分離絶縁膜110の下端よりも上方に位置するように形成されるとともに、トレンチ162端部の下方にも形成されている。

(もっと読む)

金属ゲートとストレッサーを有するゲルマニウムフィンFET

【課題】金属ゲートとストレッサーを有するゲルマニウムフィンFETを提供する。

【解決手段】集積回路構造は、n型フィン電界効果トランジスタ(fin field effect transistor、FinFET)とp型FinFETからなる。n型FinFETは、基板上の第一ゲルマニウムフィン、第一ゲルマニウムフィンの上面と側壁上の第一ゲート誘電体、及び、第一ゲート誘電体上の第一ゲート電極からなる。p型FinFETは、基板上の第二ゲルマニウムフィン、第二ゲルマニウムフィンの上面と側壁上の第二ゲート誘電体、及び、第二ゲート誘電体上の第二ゲート電極からなる。第一ゲート電極と第二ゲート電極は、ゲルマニウムの固有エネルギーレベルに近い仕事関数を有する同一材料で形成される。

(もっと読む)

121 - 140 / 547

[ Back to top ]