Fターム[5F140BJ20]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン電極 (8,852) | 2層目より上層の材料 (1,508) | 金属 (1,434) | 金属化合物(窒化物、酸化物) (313)

Fターム[5F140BJ20]に分類される特許

101 - 120 / 313

半導体装置の製造方法

【課題】

微細化したMOSトランジスタを含む半導体装置において、リーク/ショートの可能性を抑制する。

【解決手段】

半導体装置の製造方法は、活性領域上に、ゲート絶縁膜とシリコン膜とを形成し、シリコン膜上方にゲート電極用レジストパターンを形成し、レジストパターンをマスクとして、シリコン膜を厚さの途中までエッチングしてレジストパターン下方に凸部を残し、レジストパターンを除去した後シリコン膜を覆うダミー膜を形成し、ダミー膜を異方性エッチングして、凸部の側壁にダミー膜を残存させつつ、平坦面上のダミー膜を除去し、ダミー膜をマスクとして、シリコン膜の残りの厚さをエッチングしてゲート電極を形成し、ゲート電極両側の半導体基板に、ソース/ドレイン領域を形成し、シリコン領域にシリサイドを形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ゲート電極7作製後にチャネル部12を作製する縦型MISFETの製造方法において、ゲート絶縁膜10に損傷を与えたり移動度を劣化させたりすることなく、孔底面に形成された絶縁膜や、自然酸化膜を除去する。

【解決手段】単結晶半導体基板1または単結晶半導体層に形成された不純物領域8の上に、第一絶縁層4、5と、ゲート電極層7と、第二絶縁層5、4と、をこの順に積層した積層体を形成し、前記積層体に不純物領域8が露出する孔を形成し、少なくとも前記孔の側壁に露出しているゲート電極層7、および、前記孔の底面に露出している不純物領域8の上に絶縁膜10を形成し、ゲート電極層7の露出部分の上に形成された絶縁膜10の上に半導体膜を重ねて形成し、不純物領域8の上に形成された絶縁膜を除去し、孔の底面に露出している不純物領域8に接し、孔底面から孔の開口部までつながる半導体部を形成する半導体装置の製造方法を提供する。

(もっと読む)

半導体装置の製造方法

【課題】 半導体装置の製造方法に関し、シリサイドを構成する金属のサイドウォールの直下への潜り込みの影響を低減する。

【解決手段】 シリコン基板上にゲート電極を形成する工程と、ゲート電極の側壁に、第1絶縁膜による第1サイドウォールと、第1サイドウォール上にあって、第1絶縁膜とはエッチング特性の異なる第2絶縁膜による第2サイドウォールを形成する工程と、シリコン基板および第2サイドウォールを含む表面に金属をスパッタリングにより堆積させ、金属の一部をシリコン基板に侵入させる工程と、シリコン基板上に堆積した金属を除去する工程と、金属の除去工程の後に熱処理を行って、スパッタリングによってシリコン基板に侵入した金属とシリコン基板中のシリコン原子とを反応させてシリサイド層を形成する工程とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】高誘電率ゲート絶縁膜およびメタルゲート電極を備えたCMISFETの性能を向上させる。

【解決手段】高誘電率ゲート絶縁膜として機能するHf含有絶縁膜4a,4b上にメタルゲート電極であるゲート電極GE1,GE2が形成され、ゲート電極GE1,GE2は、金属膜7a,7b,7cの積層膜からなる金属膜7とその上のシリコン膜8との積層構造を有している。金属膜7の最下層の金属膜7aは、窒化チタン膜、窒化タンタル膜、窒化タングステン膜、炭化チタン膜、炭化タンタル膜または窒化タングステン膜からなり、金属膜7bは、ハフニウム膜、ジルコニウム膜またはアルミニウム膜からなり、金属膜7cは、金属膜7aと同種の材料からなる膜である。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の向上に寄与し得る半導体装置の製造方法を提供する。

【解決手段】半導体基板10上にトランジスタ34を形成する工程と、半導体基板上及びトランジスタ上に複数の部分膜36a、38a、40a、42を積層することにより、複数の部分膜を有する第1の絶縁層44を形成する工程と、第1の絶縁層上に、第1の絶縁層とエッチング特性が異なる第2の絶縁層46を形成する工程と、第1の絶縁層をエッチングストッパとして、第2の絶縁層をエッチングすることにより、第2の絶縁層にコンタクトホールを形成する工程と、コンタクトホール内に露出する第1の絶縁層をエッチングする工程とを有し、第1の絶縁層を形成する工程では、複数の部分膜のうちの最上層の部分膜以外の部分膜に対して膜を収縮させるキュア処理を行い、複数の部分膜のうちの最上層の部分膜に対してキュア処理を行わない。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電率膜のゲート絶縁膜を含むMISFETを有する半導体装置に関し、メタルゲート材料の仕事関数と半導体基板の仕事関数との間の関係によって閾値電圧を容易且つ浅い値に制御しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板上に酸化シリコンを主体とする第1の絶縁膜を形成し、第1の絶縁膜上に酸化ハフニウムを主体とする第2の絶縁膜を形成し、熱処理を行い第2の絶縁膜上にシリコンを析出させ、シリコン上にシリコンに対して酸化作用を有する第3の絶縁膜を形成し、第3の絶縁膜上に金属膜のゲート電極を形成し、熱処理を行い第3の絶縁膜の酸化作用によってシリコンを酸化させる。

(もっと読む)

半導体装置及びその製造方法

【課題】活性領域における電界の部分的な集中を防止する。

【解決手段】半導体装置は、分離絶縁領域(6)に囲まれた活性領域に形成された第1の拡散領域と第2の拡散領域と、第1の拡散領域と第2の拡散領域との間に形成された溝状のトレンチ領域と、トレンチ領域上に形成されたゲート絶縁膜(10)と、トレンチ領域を埋め込むようにゲート絶縁膜上に形成されたゲート電極(11)と、ゲート絶縁膜と分離絶縁領域とで挟まれた領域のうち上層側に位置する領域に形成された保護絶縁膜(4)と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】工程増を招くことなく、極めて高い歩留まりでゲート電極について均一で十分なフル・シリサイド化を確実に実現する。

【解決手段】ゲート電極104a,104b及びソース/ドレイン領域107a,107bのNiシリサイド化を行うに際して、1回目のNiシリサイド化の後に1回目のmsecアニール処理であるフラッシュランプアニール処理を行い、2回目のNiシリサイド化、更には必要であれば2回目のフラッシュランプアニール処理を行って、ソース/ドレイン領域107a,107b上には1回目のフラッシュランプアニール処理で形成されたNiSi層111bを維持した状態で、フル・シリサイドゲート電極115a,115bを形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】同一の工程で、同一半導体基板上に異なる構造のトランジスタを形成する半導体装置の提供。

【解決手段】半導体基板上に第一及び第二のゲート電極40,41を形成する工程と、第一のゲート電極の側壁面に第一の絶縁層122を形成するとともに、第二のゲート電極のゲート幅方向両側の半導体基板上にエピタキシャル成長層9aを形成する工程と、第二のゲート電極の側壁面に第二の絶縁層を形成する工程と、第一の絶縁層及び第二の絶縁層を覆うように第三の絶縁層を形成する工程と、第二の絶縁層を覆う第三の絶縁層を除去する工程と、第一のゲート電極のゲート幅方向両側の半導体基板及びエピタキシャル成長層にそれぞれ不純物を拡散させて、第一及び第二の不純物拡散領域6,8を形成する工程と、第一及び第二の不純物拡散領域にコンタクトプラグ12,15を接続させる工程と、を具備してなることを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置及びその製造方法

【課題】歪みの高いキャリア移動領域における寄生抵抗及びエネルギー障壁を小さくするための半導体装置を提供する。

【解決手段】半導体基板1上にゲート絶縁膜7を介して形成されたゲート電極13bと、半導体基板1のうちゲート電極13bの下方に形成されるチャネル領域6cと、チャネル領域6cの両側方に形成され、第1炭素濃度で炭素を含み、第1リン濃度でリンを含む第1の炭化シリコン層23と、第1の炭化シリコン層23上にチャネル領域6cに接合して形成され、第1リン濃度より多い第2リン濃度でリンを含み、第1炭素濃度以下の第2炭素濃度で炭素を含む第2の炭化シリコン層24とを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】高誘電率ゲート絶縁膜およびメタルゲート電極を備えたCMISFETの性能を向上させる。

【解決手段】nチャネル型MISFETQnは、半導体基板1のp型ウエルPWの表面上に、ゲート絶縁膜として機能するHf含有絶縁膜3aを介して形成されたゲート電極GE1を有し、pチャネル型MISFETQpは、n型ウエルNWの表面上に、ゲート絶縁膜として機能するHf含有絶縁膜3bを介して形成されたゲート電極GE2を有している。ゲート電極GE1,GE2は、金属膜7とその上のシリコン膜8との積層構造を有している。Hf含有絶縁膜3aは、Hfと希土類元素とSiとOとNとからなる絶縁材料膜またはHfと希土類元素とSiとOとからなる絶縁材料膜であり、Hf含有絶縁膜3bは、HfとAlとOとNとからなる絶縁材料膜またはHfとAlとOとからなる絶縁材料膜である。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】突出部の側面が凹凸状とされ、前記側面を覆うようにゲート酸化膜を形成したときに、実効的なチャネル長が増加して、ピラー型MOSトランジスタの電流駆動能力が低下するという課題があった。

【解決手段】基板と、前記基板の一面から垂直方向に突出された突出部7とを備え、突出部7の先端側の上部拡散層と、基端側の下部拡散層と、側面7cを覆うゲート絶縁膜14と、ゲート絶縁膜14を覆うゲート電極15と、を有し、チャネルが前記垂直方向となるピラー型MOSトランジスタ51を具備し、突出部7が平面視八角形状であり、突出部7の側面7cが{100}面からなる4つの主表面8a、8b、8c、8dと、{110}面および{111}面からなり、前記主表面8a、8b、8c、8dよりも面積が小さい4つの副表面9a、9b、9c、9dとからなる半導体装置101を用いることにより、上記課題を解決できる。

(もっと読む)

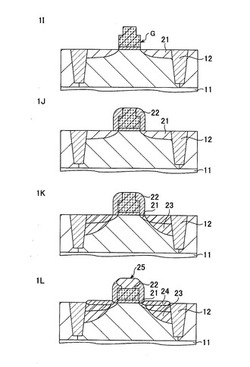

半導体装置および半導体装置の製造方法

【課題】素子分離構造の面積を増大させることなく、素子分離構造の表面の後退量を低減させる。

【解決手段】半導体基板11の表面よりも低い位置に埋め込み絶縁層12を埋め込み、埋め込み絶縁層12と材料の異なるキャップ絶縁層13を半導体基板11と埋め込み絶縁層12と間の段差12aの肩の部分にかからないようにして埋め込み絶縁層12上に形成する。

(もっと読む)

半導体装置の製造方法

【課題】ハーフピッチサイズが32nm以下のCMISデバイスを有する半導体装置において、nチャネル型電界効果トランジスタおよびpチャネル型電界効果トランジスタのそれぞれの閾値電圧を適切に設定することのできる技術を提供する。

【解決手段】pMIS形成領域に、主としてAlが拡散した高誘電体膜5h(例えばHfO2膜)により構成されるゲート絶縁膜5ならびに下層メタルゲート電極6Dと上層メタルゲート電極6Uとの積層膜からなるメタルゲート電極6を有するpMIS100pを形成し、nMIS形成領域に、主としてLa(ランタン)が拡散した高誘電体膜5h(例えばHfO2膜)により構成されるゲート絶縁膜11ならびに上層メタルゲート電極6Uからなるメタルゲート電極12を有するnMIS100nを形成する。

(もっと読む)

半導体装置の製造方法

【課題】 トランジスタのスイッチング速度低下を防止することが可能な半導体装置の製造方法を提供する。

【解決手段】 本発明では、半導体基板100上にゲート絶縁膜104を形成する工程と、ゲート絶縁膜104上に金属膜107を形成する工程と、金属膜107上に金属シリコン化合物膜108を連続して堆積する工程と、金属シリコン化合物膜108上にシリコン膜110を形成する工程と、金属膜107、金属シリコン化合物膜108及びシリコン膜110を加工する工程と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】複数の同種の製造装置を用いて半導体装置を製造する場合に、製品間での寸法のばらつきの発生を抑制できる技術を提供する。

【解決手段】制御機器CDをそれぞれの露光機に対して個別に配置する。露光処理が完了した各ロットは、どの露光機で露光処理がなされたかによって分類され、露光機毎に、露光機を調整するためのパラメータが製品情報収集部CD1に収集され、最適製造条件計算部CD2にて処理条件が計算され、計算された処理条件が設定される。すべてのロットは、露光処理を行う露光機が予め割り当てられ、露光処理が済んでいないロットは、分類機CMによって割り当てられた露光機へ振り分けられ、制御機器CDによって求められた処理条件で露光処理が行われる。

(もっと読む)

半導体装置およびその製造方法

【課題】耐熱性に優れたシリサイド層をソース・ドレイン領域に有するp型MOSFETを備える半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、半導体基板2上にゲート絶縁膜11を介して形成されたゲート電極12と、半導体基板2上のゲート電極12の両側に形成されたエレベーテッド層15と、エレベーテッド層15上に形成されたSi:C16層と、半導体基板2、エレベーテッド層15、およびSi:C16内のゲート電極12の両側に形成されたp型のソース・ドレイン領域19と、Si:C層16上に形成されたシリサイド層17と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】(110)面を主面とする半導体基板に形成されたp型MISトランジスタを備えた半導体装置において、p型MISトランジスタのさらなる性能向上を図る。

【解決手段】半導体装置は、(110)面を主面とする半導体基板10に形成されたp型MISトランジスタPTrを備えた半導体装置である。p型MISトランジスタPTrは、半導体基板10における第1の活性領域10a上に形成された第1のゲート絶縁膜13aと、第1のゲート絶縁膜13a上に形成され第1の金属膜14a及び第1の金属膜14a上に形成された第1のシリコン膜15aからなる第1のゲート電極14Aとを備えている。第1の金属膜14aは、膜厚が1nm以上であって且つ10nm以下である。

(もっと読む)

半導体装置及びその製造方法

【課題】シェアードコンタクト形成時に、ゲート電極が溶解されて形状異常となるのを防止する。

【解決手段】半導体装置は、基板1上にゲート絶縁膜2を介して形成されたゲート電極31と、基板1のゲート電極31の両側方に形成された不純物領域32及び33とを有するトランジスタと、トランジスタ上を覆うように基板1上に形成された層間絶縁膜11及び12と、不純物領域32及び33及びゲート電極31に電気的に接続するシェアードコンタクト14とを備える。ゲート電極31の側面下部を覆うように第1のサイドウォール5、第1のサイドウォール5におけるゲート電極31とは反対側に第2のサイドウォール6、第1のサイドウォール5上に、ゲート電極31の側面上部と第2のサイドウォール6とに挟まれるように第3のサイドウォール9bが形成されている。第2及び第3のサイドウォール6及び9bは、第1のサイドウォール5とは異なる材料からなる。

(もっと読む)

半導体装置の製造方法

【課題】配線層に銅配線を使用する半導体装置において、半導体基板の裏面に付着した銅原子が半導体基板の裏面から内部へと拡散することを抑制し、半導体基板の主面に形成されているMISFETなどの半導体素子の特性劣化を抑制できる技術を提供する。

【解決手段】半導体基板1Sの主面に形成される銅拡散防止膜を銅拡散防止膜DCF1aとし、半導体基板1Sの裏面に形成される銅拡散防止膜を銅拡散防止膜DCF1bとする。本実施の形態1の特徴は、半導体基板1Sの裏面に銅拡散防止膜DCF1bを形成する点にある。このように、銅配線の形成工程の前に、半導体基板1Sの裏面に銅拡散防止膜DCF1bを形成することにより、半導体基板1Sの裏面から銅原子(銅化合物を含む)が拡散することを防止できる。

(もっと読む)

101 - 120 / 313

[ Back to top ]