Fターム[5F140BJ21]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン電極 (8,852) | 結晶性、不純物 (46)

Fターム[5F140BJ21]に分類される特許

1 - 20 / 46

半導体装置及びその製造方法

【課題】半導体基板における抵抗やコンタクト抵抗を低減させた半導体装置及びその製造方法を提供すること。

【解決手段】半導体装置は、シリコン層と、シリコン層に形成され、第1不純物を含有する金属シリサイド層と、を備える。シリコン層は、金属シリサイド層が形成されていない領域において、第1不純物に起因するエンド・オブ・レンジ欠陥を有していない。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート絶縁膜をHigh−k材料で構成し、ゲート電極をメタル材料で構成するHK/MGトランジスタを有する半導体装置において、安定した動作特性を得ることのできる技術を提供する。

【解決手段】素子分離部2で囲まれた活性領域14に位置し、後の工程でコア用nMISのゲートGが形成される領域Ga1のみに、Nch用ゲートスタック構造NGを構成する積層膜を形成し、上記領域Ga1以外の領域NGa1には、Pch用ゲートスタック構造PGを構成する積層膜を形成する。これにより、コア用nMISのゲートGが形成される領域Ga1へ素子分離部2から引き寄せられる酸素原子の供給量を減少させる。

(もっと読む)

半導体装置およびその製造方法

【課題】サリサイドプロセスで金属シリサイド層を形成した半導体装置の性能を向上させる。

【解決手段】ゲート電極GEと上部に金属シリサイド層11bが形成されたソース・ドレイン領域とを有するMISFETが半導体基板1の主面に複数形成されている。金属シリサイド層11bは、Pt,Pd,V,Er,Ybからなる群から選択された少なくとも一種からなる第1金属元素およびニッケルのシリサイドからなる。半導体基板1の主面に形成された複数のMISFETのソース・ドレイン領域のうち、ゲート長方向に最も近接して隣り合うゲート電極GE間に配置されたソース・ドレイン領域のゲート長方向の幅W1cよりも、金属シリサイド層11bの粒径が小さい。

(もっと読む)

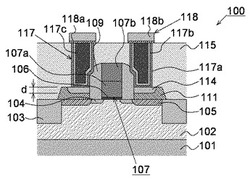

エピタキシャルソース/ドレインが自己整合したマルチゲート半導体デバイス

低寄生抵抗であるチャネル歪みされたマルチゲートトランジスタとその製造方法に係る。ゲートを連結したチャネル側壁の高さがHsiである半導体フィンのチャネル領域の上にゲートスタックを形成されてよく、ゲートスタックに隣接する半導体フィンのソース/ドレイン領域内に、エッチングレートを制御するドーパントを注入してよい。ドーピングされたフィン領域をエッチングして、半導体フィンの、略Hsiに等しい厚みを除去して、ゲートスタックの一部の下にある半導体基板の部分を露呈させるソース/ドレイン延長キャビティを形成してよい。露呈した半導体基板の上に材料を成長させて、再成長したソース/ドレイン・フィン領域を形成して、ソース/ドレイン延長キャビティを充填して、ゲートスタックからの長さを、チャネルの長さに実質的に平行な方向に離れる方向に延ばしてよい。 (もっと読む)

オーミック電極およびその製造方法

【課題】オーミック特性を有し且つアモルファス構造であるオーミック電極層がp型SiC半導体の表面に直接積層されているp型SiC半導体のオーミック電極およびその製造方法をを提供する。

【解決手段】下記式の(I)〜(IV)で示される4つの直線および曲線で囲まれる組成域(但し、x=0の線上を除く)のTi(1−x−y)Si(x)C(y)三元素混合膜からなり、且つアモルファス構造であるオーミック電極層がp型SiC半導体の表面に直接積層されているp型SiC半導体のオーミック電極およびその製造方法。(I)x=0(0.35≦y≦0.5)(II)y=1.778(x−0.375)2+0.1(0≦x≦0.375)(III)y=−1.120x+0.5200(0.1667≦x≦0.375)(IV)y=−2.504x2−0.5828x+0.5(0≦x≦0.1667)

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1に形成したnチャネル型MISFETQnのソース・ドレイン用のn+型半導体領域7bおよびゲート電極GE1上と、pチャネル型MISFETQpのソース・ドレイン用のp+型半導体領域8bおよびゲート電極GE2上とに、ニッケル白金シリサイドからなる金属シリサイド層13bをサリサイドプロセスで形成する。その後、半導体基板1全面上に引張応力膜TSL1を形成してから、pチャネル型MISFETQp上の引張応力膜TSL1をドライエッチングで除去し、半導体基板1全面上に圧縮応力膜CSL1を形成してからnチャネル型MISFETQn上の圧縮応力膜CSL1をドライエッチングで除去する。金属シリサイド層13bにおけるPt濃度は、表面が最も高く、表面から深い位置になるほど低くなっている。

(もっと読む)

半導体装置

【課題】半導体または誘電体と、金属との界面において、接合する金属の実効仕事関数を最適化することを可能にするとともに、抵抗を可及的に低くすることを可能にする。

【解決手段】半導体膜4aと、半導体膜上に形成された酸化膜6bと、酸化膜上に形成された金属膜12aと、を備え、酸化膜がTi酸化膜であって、酸化膜に、V、Cr、Mn、Fe、Co、Ni、Nb、Mo、Tc、Ru、Rh、Pd、Ta、W、Re、Os、Ir、Ptから選ばれた少なくとも一つの元素が添加されている。

(もっと読む)

電界効果型トランジスタ

【課題】従来の電界効果型トランジスタでは、ソース領域およびドレイン領域に形成する高濃度不純物のイオン注入工程によりアモルファス化される半導体基板表面が、低濃度不純物拡散領域と高濃度不純物拡散領域との境界部において、活性化熱処理により結晶欠陥を誘発し、電界効果型トランジスタの信頼性を著しく低下させる問題があった。

【解決手段】本発明の電界効果型トランジスタは、ソース領域およびドレイン領域を構成する部分の上部に緩衝膜を設けることで、高濃度不純物のイオン注入を行っても、この領域の半導体基板表面がアモルファス化することを防ぐことができる。これにより、低濃度不純物拡散領域と高濃度不純物拡散領域との境界部において、再結晶化による結晶欠陥の発生を防ぐことができる。

(もっと読む)

半導体装置及びその製造方法

【課題】炭素含有シリコン領域を有するn型MISトランジスタを備えた半導体装置において、チャネル領域のゲート長方向に印加される引っ張り応力の大きさを、効果的に増大させる。

【解決手段】少なくともn型MISトランジスタNTrを有する半導体装置において、n型MISトランジスタnTrは、半導体基板10における第1の半導体領域10a上に形成された第1のゲート絶縁膜13aと、第1のゲート絶縁膜13a上に形成された第1のゲート電極14aと、第1のゲート電極14aの側面上に形成された第1のサイドウォール18Aと、第1のサイドウォール18Aの外側方に形成された炭素含有シリコン領域27とを備え、炭素含有シリコン領域27の上面高さは、第1の半導体領域10aにおける第1のゲート絶縁膜13aの下に位置する領域の上面高さよりも高い。

(もっと読む)

半導体装置の製造方法

【課題】消費電力の少ない半導体装置の製造方法を提供する。

【解決手段】ゲート電極13の多結晶シリコン領域と、ゲート電極13下のチャネル領域11Cを挟んで配置された一対の単結晶シリコン領域11S,11Dとが形成されたシリコン基板11に対して、単結晶シリコン領域11S,11D上に単結晶のSiGe混晶層領域14A,14Bを成長させ、且つ多結晶シリコン領域13上に多結晶のSiGe混晶層領域14Cを成長させる工程と、Clを含むガスを用いて、一対の単結晶シリコン領域11S,11D上に成長したSiGe混晶層領域14A,14Bの表面側の一部を取り除くと共に、多結晶シリコン領域13上に成長したSiGe混晶層領域14Cを取り除く工程と、一対の単結晶シリコン領域上のSiGe混晶層領域14A,14B上に単結晶のシリコン層15A,15Bを成長させる工程と、シリコン層15A,15Bをシリサイド化する工程と、を有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体基板上に設けられるNiPtSi電極の熱安定性を向上させる半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体基板と、この半導体基板中のチャネル領域と、チャネル領域上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、チャネル領域の両側に形成され、NiおよびPtを主成分とする金属半導体化合物層からなるソース/ドレイン電極とを備え、金属半導体化合物層と半導体基板との界面において、金属半導体化合物層の単一の結晶粒と半導体基板との境界部の最大Pt濃度が、界面の平均Pt濃度よりも高いことを特徴とする半導体装置および半導体装置の製造方法。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体基板上に設けられる金属半導体化合物電極の界面抵抗を低減する半導体装置およびその製造方法を提供する。

【解決手段】半導体基板と、半導体基板上に形成され、Sを1×1020atoms/cm3以上含有する界面層と、界面層上に形成され、略全域にSを1×1020atoms/cm3以上含有する金属半導体化合物層と、金属半導体化合物層上の金属電極を有することを特徴とする半導体装置。半導体基板上に金属膜を堆積し、第1の熱処理により、金属膜を半導体基板と反応させて、金属半導体化合物層を形成し、金属半導体化合物層に、飛程が金属半導体化合物層の膜厚未満となる条件でSをイオン注入し、第2の熱処理により、Sを再配置することを特徴とする半導体装置の製造方法。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ショットキー接触を発生させることなく、炭素の析出を抑制することにより配線の密着性を向上したオーミック電極を有する炭化珪素半導体装置およびその製造方法を提供する。

【解決手段】

SiC半導体装置においてオーミック電極を形成する際に、SiC層11の一方の主表面上には、1種の第1の金属元素からなる、第1の金属層12を形成する。また、第1の金属層の、SiC層11と対向する表面とは反対側の表面上(図1における上側)に、SiからなるSi層13を形成する。このようにして形成した積層構造10Aに対して熱処理を行なう。以上により、電極の表面層への炭素原子の析出や、SiとSiCとによるショットキー接触の形成が抑制された、配線との良好な密着性を示すオーミック電極を有する炭化珪素半導体装置を得ることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】寄生抵抗の低減に対して有利な半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板11と、前記半導体基板上にゲート絶縁膜12を介して設けられるゲート電極13と、前記半導体基板中に前記ゲート電極を挟むように隔離して設けられるエクステンション領域LDDと、前記エクステンション領域の両側を挟むように前記半導体基板中に設けられ、前記半導体基板とは異なる格子定数有し、前記半導体基板に歪みを付与する歪み付与層22と、前記エクステンション領域の両側の前記半導体基板中に前記ゲート電極を挟むように隔離して設けられるソース/ドレインS/Dと、前記ソース/ドレイン上に設けられるシリサイド層SS/Dとを具備し、前記歪み付与層と前記半導体基板との界面Si-Siは、少なくとも前記シリサイド層の底面の一部に一致する。

(もっと読む)

半導体装置の製造方法

【課題】所望のシリサイド膜を形成することが可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板10に形成されたシリコンを主成分とするソース・ドレイン拡散層3上、および半導体基板に形成されソース・ドレイン拡散層に隣接する素子分離絶縁膜の上に、金属を堆積して金属膜を形成し、第1の加熱温度の第1の加熱処理によりソース・ドレイン拡散層のシリコンとソース・ドレイン拡散層上の金属とを反応させて、ソース・ドレイン拡散層の上部をシリサイド化してシリサイド膜106を形成し、シリサイド膜を酸化させないようにして、素子分離絶縁膜の上の金属膜の少なくとも表面を選択的に酸化して、金属酸化膜105を形成し、第1の加熱温度よりも高い第2の加熱温度の第2の加熱処理によりシリサイド膜のシリコンの濃度を増加させ、素子分離絶縁膜上の金属酸化膜および金属膜の未反応部分を選択的に除去する。

(もっと読む)

半導体装置およびその製造方法

【課題】ソース/ドレイン拡散層に形成されるシリサイド層のスパイクやコンタクトの突き抜けを抑制して、接合リークの発生を低減するとともに、シリサイド層を低抵抗化した半導体装置およびその製造方法を提供する。

【解決手段】半導体装置1は、半導体基板10の上に形成されたトランジスタを有する。トランジスタのゲート電極は、ポリシリコン電極14とその上に形成されたシリサイド層32から構成される。さらに、低濃度ドーピング領域16、高濃度ドーピング領域からなるソース/ドレイン拡散層20、ソース/ドレイン拡散層20上のシリサイド層30を備える。シリサイド層30の表面は、半導体基板10の表面よりも上方に位置している。また、シリサイド層30はシリサイド化反応抑制金属を含み、シリサイド層30の表面から所定の深さに至る領域において、シリサイド層30の表面から基板側へ向かってシリサイド化反応抑制金属の濃度が高くなる濃度プロファイルを有する。

(もっと読む)

配線構造、薄膜トランジスタ基板およびその製造方法、並びに表示装置

【課題】純AlまたはAl合金のAl系合金配線と半導体層との間のバリアメタル層を省略することが可能なダイレクトコンタクト技術であって、幅広いプロセスマージンの範囲においてAl系合金配線を半導体層に直接かつ確実に接続することができる技術を提供する。

【解決手段】本発明の配線構造は、基板の上に、基板側から順に、半導体層と、純AlまたはAl合金のAl系合金膜とを備えた配線構造であって、前記半導体層と前記Al系合金膜との間に、基板側から順に、窒素、炭素、およびフッ素よりなる群から選択される少なくとも一種の元素を含有する(N、C、F)層と、AlおよびSiを含むAl−Si拡散層との積層構造を含んでおり、且つ、前記(N、C、F)層を構成する窒素、炭素、およびフッ素のいずれかの元素は、前記半導体層のSiと結合している。

(もっと読む)

コンタクト形成方法、半導体装置の製造方法および半導体装置

【課題】 低抵抗率のコンタクトを実現した半導体装置の製造方法を提供する。

【解決手段】 半導体装置のp型またはn型コンタクト領域となるべきシリコン部分へp型またはn型不純物をイオン注入する工程と、該イオン注入工程の後に、注入されたイオンを活性化するための熱処理を行うことなしに前記コンタクト領域表面にコンタクト用の金属の膜を形成する工程と、加熱によって前記金属を前記シリコン部分と反応させ前記金属のシリサイドを形成する工程とを含む。なお、前記注入されたイオンを前記金属の膜が形成された後の熱処理によって活性化する工程を同時に行なうことが望ましい。

(もっと読む)

半導体装置の製造方法

【課題】サリサイドプロセスで金属シリサイド層を形成した半導体装置の性能を向上させる。

【解決手段】ゲート絶縁膜7、ゲート電極8a,8b、ソース・ドレイン用のn+型半導体領域9b及びp+型半導体領域10bを形成してから、半導体基板1上に金属膜及びバリア膜を形成し、第1の熱処理を行って金属膜とゲート電極8a,8b、n+型半導体領域9bおよびp+型半導体領域10bとを反応させることで、金属膜を構成する金属元素MのモノシリサイドMSiからなる金属シリサイド層41を形成する。その後、バリア膜および未反応の金属膜を除去してから、第2の熱処理を行い金属シリサイド層41を安定化させる。これ以降、半導体基板1の温度が第2の熱処理の熱処理温度よりも高温となるような処理は行わない。第2の熱処理の熱処理温度は、金属元素MのダイシリサイドMSi2の格子サイズと半導体基板1の格子サイズが一致する温度よりも低くする。

(もっと読む)

半導体装置、キャパシタ、および電界効果トランジスタ

【課題】半導体と金属との界面において、接合する金属の実効仕事関数を最適化した半導体装置を提供することを可能にする。

【解決手段】半導体膜4aと、半導体膜上に形成された酸化膜6bと、酸化膜上に形成された金属膜12aとを備え、酸化膜がHf酸化膜或いはZr酸化膜であって、酸化膜に、V、Cr、Mn、Nb、Mo、Tc、W、Reから選ばれた少なくとも一つの元素が添加されている。

(もっと読む)

1 - 20 / 46

[ Back to top ]