Fターム[5F140BK20]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン領域、電極及びSD近傍領域の製造 (13,929) | ソース・ドレイン領域形成後の処理 (2,202) | 熱処理 (1,739)

Fターム[5F140BK20]の下位に属するFターム

活性化 (1,499)

Fターム[5F140BK20]に分類される特許

161 - 180 / 240

炭素を混合したSI膜を使用した極浅接合形成の方法

基板上に極浅接合を形成する方法を提供する。特定の実施形態では、基板上に極浅接合を形成する方法を提供する。基板をプロセスチャンバ内に配置する。基板上にシリコンカーボン層を堆積する。シリコンカーボン層にドーパントを曝露させる。基板を950℃より高温に加熱して、シリコンカーボン層内のドーパントを十分にアニーリングする。特定の実施形態では、基板を約1000〜約1100℃に加熱する。特定の実施形態では、基板を約1030〜約1050℃に加熱する。また特定の実施形態では、急なp−n接合を有する構造を提供する。 (もっと読む)

引張歪みを有し、結晶方位に沿って方向付けられた、電荷キャリア移動度が増加したチャネルを有するトランジスタ

シリコン層(102)の結晶学的特徴に対してチャネル長方向を適切に方向付けることにより、歪みのあるシリコン/炭素材料(109)の歪み生成効果が従来の技術よりも著しく向上する。1つの例示的実施形態では、チャネル(103)は(100)の表面方向に対して<100>の方向に沿って方向づけられ、これにより電子移動度がほぼファクター4増加する。  (もっと読む)

(もっと読む)

ドーパントを阻止する超格子を有する半導体素子及び関連方法

半導体素子は、少なくとも1つの金属-酸化物電界効果型トランジスタ(MOSFET)を有して良い。前記少なくとも1つのMOSFETは、主部、該主部に隣接するチャネル層、及び前記主部と前記チャネル層との間に設けられたドーパントを阻止する超格子を有して良い。前記ドーパントを阻止する超格子は、複数の層からなる複数の積層群を含んで良い。前記ドーパントを阻止する超格子の層が構成する各群は、基本半導体部分を画定する複数の積層された基本半導体分子層、及び隣接する基本半導体部分の結晶格子内部に束縛された少なくとも1層の非半導体分子層を有して良い。  (もっと読む)

(もっと読む)

insituまたはexsitu熱処理と組み合わされた改良型電界効果トランジスタ向けのイオン注入(FETデバイスを製造する方法およびFETデバイス)

【課題】所望のドーパント密度プロファイルを達成することができ、アモルファス化される層の厚さが十分に限定され、または歪み緩和のレベルが十分に低く、あるいはこれらがともに達成されるイオン注入法を提供することにある。

【解決手段】本発明は、イオン注入ステップをin situまたはex situ熱処理と組み合わせて、注入誘起性のアモルファス化(超薄シリコン・オン・インシュレータ層のFETのソース/ドレイン(S/D)領域の潜在的な問題)、および歪まされたS/D領域の注入誘起性の塑性緩和(その下の基板層と格子不整合の状態にある埋込みS/D領域によってチャネル歪みが誘起される歪みチャネルFETの潜在的な問題)をともに回避し、またはともに最小化し、あるいは一方を回避し、もう一方を最小化する方法を教示する。第1の実施形態では、イオン注入を高温で実行することによって、イオン注入がin situ熱処理と組み合わされる。第2の実施形態では、熱注入を実行する能力を有する手段を必要としない「デバイデッド−ドーズ−アニール−イン−ビトウィーン」(DDAB)法において、イオン注入がex situ熱処理と組み合わせられる。

(もっと読む)

半導体装置及びその製造方法

【課題】従来の半導体装置では、電極パッドに過電圧が印加された際に、チップ内の回路素子が破壊されるという問題があった。

【解決手段】本発明の半導体装置では、N型のエピタキシャル層3は分離領域4、5により複数の素子形成領域に区画されている。素子形成領域の1つにMOSトランジスタ1が形成されている。MOSトランジスタ1の周囲には、PN接合領域34、35を有する保護素子が形成されている。PN接合領域34、35は、MOSトランジスタ1のPN接合領域32、33より接合耐圧が低い。この構造により、ソース電極用のパッドに負のESDサージが印加された際、PN接合領域34、35がブレークダウンし、MOSトランジスタ1を保護することができる。

(もっと読む)

半導体装置の製造方法

【課題】超高速昇降温アニールによるスリップ転位や脆性破壊に対するウェハ強度を確保できる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、バルク内部の酸素析出物密度が5×106〜5×107cm−3で、そのサイズが100nmより小さく、且つ溶存酸素濃度が1.1×1018〜1.2×1018cm−3のSi基板の主表面に不純物をイオン注入する工程と、前記Si基板に昇降温速度が1×105℃/secより高い超高速昇降温アニールを施し、前記不純物を電気的に活性化して半導体素子の少なくとも一部を形成する工程とを具備する。

(もっと読む)

半導体装置及びその製造方法

【課題】LDMOSトランジスタのチャネル領域形成の精度を向上させる。他の素子(MOSトランジスタ)と混載する場合において、各素子の特性を損なわない半導体装置及びその製造方法を提供する。

【解決手段】第1のポリシリコン層6をマスクとしてイオン注入し、自己整合的にボディ層8を形成する。次に、第1のポリシリコン層6を含めた半導体基板1の表面にポリシリコン層12を例えばCVD法で形成する。次に、ポリシリコン層12をエッチバックし、第1のポリシリコン層6の少なくとも側壁に、ゲート電極の一部となる第2のポリシリコン層13を形成する。第2のポリシリコン層13の側面をマスクとしてボディ層8にイオン注入し、自己整合的にソース領域23を形成する。このようにボディ層8とソース領域23の両者を自己整合的に形成し、第2のポリシリコン層13の幅でチャネルの長さを調節する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】

ボロン(B)を浅く、高濃度にドープすることのできる半導体装置の製造方法を提供する。

【解決手段】

半導体装置の製造方法は、(a)半導体基板にボロン(B)をイオン注入する工程と、(b)半導体基板にフッ素(F)または窒素(N)をイオン注入する工程と、(c)工程(a)、(b)を行った後、半導体基板のイオン注入を行った領域に加熱時間が100msec以下であるアニールを行う工程と、(d)工程(c)の後、半導体基板のイオン注入を行った領域にアニールを行う工程と、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、ゲート絶縁膜の膜厚が増加することを抑制することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10上に絶縁膜20を形成するステップと、絶縁膜上に第1の金属膜30を形成するステップと、第1の金属膜の上方に、酸素分子1モルあたりの金属酸化物を生成する際の生成エネルギーが負であって、かつ生成エネルギーの絶対値が第1の金属膜より大きい第2の金属膜50を形成するステップと、第1及び第2の金属膜にパターニングを行うステップと、所定の熱処理を行うステップとを備える。

(もっと読む)

半導体装置の製造方法

【課題】装置構成に合わせて、最終的なゲート電極の寸法が均一になるように複数の工程を管理して、ゲート電極の加工寸法のウエハ面内ばらつきを最小化することができる製造技術を提供する。

【解決手段】第1のプロセス装置101と、1つ以上後の第2のプロセス装置111とを有する半導体製造システムを用い、プロセス装置101で処理されたウエハ105の計測データを基に、ウエハ上に形成された薄膜膜厚もしくは構造体の高さがウエハ面内で均一になるように、プロセス装置111におけるウエハ115の処理方向を制御する。すなわち、ゲート寸法のモデル式にしたがいゲート電極の下地構造形成時のウエハ処理方向を制御(または素子分離等の下地構造を考慮して露光装置においてレジスト転写形成時にショット毎にドーズ量を制御)することで、エッチング加工後のゲート長をウエハ面内で均一化する。

(もっと読む)

選択的堆積

基板の表面上にシリコン含有材料をエピタキシャルに形成する方法は、プロセスチャンバー温度及び圧力の調整を通じてハロゲン含有ガスをエッチングガス及び担体ガスの両方として使用する。HClをハロゲン含有ガスとして使用するのが有益である。なぜなら、HClを担体ガスからエッチングガスへ変換することが、チャンバー圧力の調整で容易に遂行できるからである。 (もっと読む)

半導体装置の製造方法、電子光学装置の製造方法および電子機器の製造方法

【課題】不純物ドープ半導体膜を形成する際の熱負荷を低減する。また、熱負荷を低減することで、TFTの特性を向上させる。

【解決手段】半導体膜3および絶縁膜5を順次形成し、これらの膜よりなる積層膜した後、この積層膜を選択的に除去することにより、プール部7bおよびこのプール部7bに連結した一対の溝7aを形成し、プール部7bにドープ高次シラン組成物溶液9を充填し、この溶液9を溝7a内部に導入した後、熱処理によりドープシリコン膜9Aを形成する。次いで、溝7a間に位置する絶縁膜5上にゲート電極を形成することによりTFTを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】300V程度の高いソース・ドレイン耐圧Bvdsを有するとともに、低いオン抵抗を有した高耐圧MOSトランジスタを提供する。

【解決手段】ソース層55の側からゲート電極54の下方へ延びたN型のボディ層63が形成されている。第1のドリフト層65より深くエピタキシャル半導体層51の中に拡散され、第1のドリフト層65の下方からゲート電極54の下方へ延びて、このゲート電極54の下方でボディ層63とPN接合を形成するP型の第2のドリフト層64が形成されている。この第2のドリフト層64とソース層55との間のボディ層63の表面がチャネル領域CH2となる。第1のドリフト層65は電界集中の生じやすいゲート電極54の左端E1から離して形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】高いゲート耐圧、高いソース・ドレイン耐圧を有するとともに、低いオン抵抗を有した高耐圧MOSトランジスタを提供する。

【解決手段】エピタキシャル・シリコン層2上には、LOCOS膜4を介してゲート電極5が形成されている。LOCOS膜4の左側にはP型の第1のドリフト層6が形成され、ゲート電極5を間に挟んでLOCOS膜4の右側のエピタキシャル・シリコン層2の表面には、第1のドリフト層6と対向してP+型のソース層7が配置されている。第1のドリフト層6より深くエピタキシャル・シリコン層2の中に拡散され、第1のドリフト層6の下方からLOCOS膜4の左側下方へ延びるP型の第2のドリフト層9が形成されている。LOCOS膜4の左端下方の第2のドリフト層9の下部には凹部Rが形成されている。

(もっと読む)

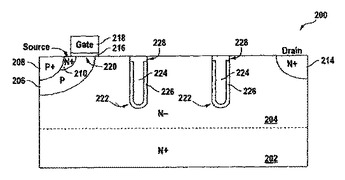

セルフバイアス電極を有するラテラルパワーデバイス

第1導電タイプのドリフト領域及び当該ドリフト領域内の第2導電タイプのウェル領域を含み、当該ウェル領域及び当該ドリフト領域の間でpn接合を形成する半導体パワートランジスタである。第1導電タイプの第1ハイドープシリコン領域が当該ウェル領域にありかつ第2ハイドープシリコン領域が当該ドリフト領域にある。当該第2ハイドープシリコン領域が当該ウェル領域から横方向に離間されており、導電状態において当該と連ジスたがバイアスするときに電流が当該ドリフト領域を介して第1と第2ハイドープシリコン領域の間を横方向に流れる。当該ドリフト領域内に当該電流の流れに対して垂直方向に伸長する複数のトレンチの各々が当該トレンチ側壁の少なくとも一部及び導電性電極の少なくとも1つをライニングする誘電層を含む。  (もっと読む)

(もっと読む)

エッチング方法及び半導体装置の製造方法

【課題】Si(シリコン)、SiN、レジスト、NiSi、CoSi、酸化物等に対するSiGe(シリコンゲルマニウム)の選択比をあげることができ、Si(シリコン)とSiGe(シリコンゲルマニウム)のヘテロ構造部分に対する加工精度を高くできるエッチング方法及びこれを用いた半導体装置の製造方法を提供すること。

【解決手段】SiGe(シリコンゲルマニウム)層と、SiGe(シリコンゲルマニウム)層の上に形成されたSi(シリコン)層と、を含むヘテロ構造体をエッチングするマイクロ波プラズマエッチング方法であって、反応ガスとしてフッ化物ガスのみを用い、その流量を10〜800sccm、処理圧力を266Pa以下、マイクロ波パワーを150〜400W、処理温度を5〜25℃として、SiGe(シリコンゲルマニウム)層を選択的に等方性エッチングする。

(もっと読む)

半導体装置及びその製造方法

【課題】 CMOS型半導体装置に関して、低濃度ソース・ドレイン拡散層の形成に、イオン注入を用いず、熱処理を用いて逆導電型不純物を含有する絶縁膜から低濃度の逆導電型不純物を熱拡散させる場合、熱拡散源として、PSG膜とBSG膜とが必要であり、プロセスが複雑となっていた。

【解決手段】 PSG膜もしくはBSG膜のいずれかのみを熱拡散源として熱処理を行うことにより、容易に浅い低濃度ソース・ドレイン拡散領域を形成することが可能な半導体装置およびその製造方法を提供する。

(もっと読む)

半導体装置およびその製造方法

【課題】応力制御膜に生ずる複数の歪によって異なる複数種のトランジスタのチャネル移動度を向上させる。

【解決手段】シリコン基板21上にn型FET素子領域30aとp型FET素子領域30bとを形成し、ゲート電極25a,25bおよびソース・ドレイン領域28a,28bを内包すると共に、p型FET素子領域30bに対して最適化された真性応力を有する応力制御膜31を形成し、n型FET素子領域30a上の応力制御膜31に対して化学反応処理を施すことによって、n型FET素子領域30a上に他とは異なる真性応力を有する応力制御膜31aにす。こうして、互いに異なる応力を両FET素子領域30a,30bに作用させてチャネル領域の電子移動度を向上させ、ドレイン電流を向上させる。

(もっと読む)

異なる高さのコンタクト線を有する高密度MOSFET回路を製造するための構造および方法

【課題】異なる高さのコンタクト線を有する高密度MOSFET回路を製造するための構造、方法などを提示すること。

【解決手段】このMOSFET回路は、コンタクト線(500、1300)と、コンタクト線(500、1300)の近くに位置するゲート(310、1210)とを含む。コンタクト線(500、1300)は、ゲート(310、1210)の高さよりも低い高さを含む。このMOSFET回路はさらに、ゲート(310、1210)の近くに位置するゲート・スペーサ(710、715、1610、1615)を含み、コンタクト線(500、1300)とゲート(310、1210)との間のコンタクト線(500、1300)の近くに位置するコンタクト線スペーサを含まない。

(もっと読む)

半導体装置およびその製造方法

【課題】ショートチャネル効果を抑制しつつ、キャリアの移動度を向上させた半導体装置およびその製造方法を提供する。

【解決手段】本実施形態に係る半導体装置は、半導体基板1と、半導体基板1上にゲート絶縁膜2を介して形成されたゲート電極3と、ゲート電極3下におけるチャネル領域を挟むように半導体基板1に埋め込まれて形成され、半導体基板1とは格子間隔の異なる材料からなる半導体層10とを有し、半導体層10は、チャネル領域側に配置された第1半導体層11と、第1半導体層11よりも不純物濃度が大きい第2半導体層12とを有する。

(もっと読む)

161 - 180 / 240

[ Back to top ]