Fターム[5F140BK20]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン領域、電極及びSD近傍領域の製造 (13,929) | ソース・ドレイン領域形成後の処理 (2,202) | 熱処理 (1,739)

Fターム[5F140BK20]の下位に属するFターム

活性化 (1,499)

Fターム[5F140BK20]に分類される特許

221 - 240 / 240

ゲート及びチャネル内に歪を誘起させてCMOSトランジスタの性能を向上させる方法

【課題】 ゲート内の応力を調節することによってトランジスタ・チャネル内に歪を誘起させること。

【解決手段】 相補型金属酸化物半導体トランジスタを製造する方法は、異なる型のトランジスタ、例えばN型金属酸化物半導体(NMOS)トランジスタ及びP型金属酸化物半導体(PMOS)トランジスタ(第1及び第2型トランジスタ)を基板(12)上に形成する。この方法は、これらのNMOSトランジスタ及びPMOSトランジスタ上に任意の酸化物層を形成し、次いでNMOSトランジスタ及びPMOSトランジスタを硬い材料(50)、例えば窒化ケイ素層で覆う。この後、この方法は、この硬い材料層(50)の一部をパターン形成し、硬い材料層がNMOSトランジスタ上にのみ残るようにする。次に、この方法は、NMOSトランジスタを加熱し(178、204)、次いで硬い材料層(50)の残存部分を除去する。PMOSトランジスタ(PFET)のゲート(20)又はチャネル領域内に応力を生じさせることなく、NMOSトランジスタ(NFET)のゲート(22)内に圧縮応力、チャネル領域内に引張応力(70)を生じさせることによって、この方法は、PFETの性能を低下させることなく、NFETの性能を改善する。

(もっと読む)

集積回路の領域に、特にトランジスタの電極にコンタクト・パッドを生成するための方法

【課題】コンパクト・パッドの生成について改善された方法を提供する。

【解決手段】領域(51)は、該領域の表面の少なくとも一部に伸長する区域(510)であって、該領域に対して選択的に除去することが可能な材料から形成される区域を作成するよう、局所的に変更される。該領域は、絶縁材料(7)で覆われており、該区域の表面に出現するオリフィス(90)が、該絶縁材料内に形成される。該選択的に除去が可能である材料は、該区域に代わってキャビティ(520)を形成するように、該区域から、オリフィスを介して除去される。キャビティおよびオリフィスは、少なくとも1つの導電性材料(91)で充填される。

(もっと読む)

レーザ・アニールによる固相エピタキシャル成長(epitaxy)再結晶化

MOS型トランジスタの浅く急峻な傾斜ドレイン拡張部を製造するための方法(70)を説明する。この方法では、半導体製品の製造におけるレーザSPERアニール・プロセスを用いて、ドレイン拡張部内で固相エピタキシャル成長再結晶化が成される。一つの方法(70)は、基板のチャネル領域に隣接する基板の拡張領域内深くにゲルマニウムなどの重イオン種を打ち込んで深い非晶化領域を形成し、その後、チャネル領域に隣接する基板の拡張領域内にボロン又は別のこのようなドーパント種を打ち込む、事前非晶化プロセス(74)を含む。打ち込んだドーパントを、その後、低温でプレアニール(78)して接合深さ及びドーピング濃度を定める。その後、拡張部及び/又は深いソース/ドレイン領域を、チャネル領域に近接する領域の固相エピタキシャル成長再結晶化を提供する高温のレーザでアニールして(84)、急峻な傾斜を有する超高ドーピング濃度及び活性化レベルを達成する。  (もっと読む)

(もっと読む)

半導体装置、その製造方法、および情報処理装置

【課題】ソース・ドレイン領域の占有面積が小さい半導体装置およびその製造方法を提供する。

【解決手段】半導体装置1910は、素子分離領域101と活性領域102とを有する半導体基板100と、活性領域102上にゲート絶縁膜103を介して設けられ、側壁の少なくとも一部がゲート電極側壁絶縁膜105で覆われたゲート電極104と、ゲート電極104の両側にゲート電極側壁絶縁膜105を介してそれぞれ設けられたソース領域106およびドレイン領域106とを備えている。ソース領域106およびドレイン領域106の少なくとも一方は、コンタクト配線と接触するための第2の面を有し、第2の面は、第1の面AA’に対して傾いており、第2の面は、素子分離領域の表面と80度以下の角度で交差する。

(もっと読む)

半導体装置の製造方法

【課題】導通時における駆動力を向上させる。

【解決手段】所定の開口を有するマスク層を用いて、基板1とドレイン領域2からなる半導体基体の一主面側に所定の溝15を形成する工程と、少なくとも溝15の側壁に接して、該溝15からはみ出すように埋め込み領域11を形成する工程と、半導体基体並びに埋め込み領域11に接するようにヘテロ半導体層30を形成する工程と、ヘテロ半導体層30をパターニングし、ヘテロ半導体領域3を形成する工程とを含む。

(もっと読む)

半導体の構造とトランジスタ、および半導体の構造とトランジスタとを形成する方法

セルリーケージ、ゲート閾値電圧制御の困難性の改善、チャンネル内での浮動基体効果の改善を目的とする。

【解決手段】

本発明は上面のある半導体基板を有するトランジスタを含む。1対のソース/ドレイン領域が半導体基板の中に形成され、またチャネル領域が半導体基板の中に形成されて半導体基板の上面に対して一般的に垂直に延びる。ゲートが半導体基板の中で1対のソース/ドレイン領域の間に形成される。

(もっと読む)

高性能なサブ0.1マイクロメートルトランジスタ用のソース/ドレイン構造

【課題】チャネルパンチスルーおよび短チャネル効果が低減された、高性能な短チャネル長のトランジスタ構造を提供すること。

【解決手段】本発明によるトランジスタ構造(10)は、基板内に形成されたp型ウェル12を備える。ゲート構造(14)は、ソース領域(18)とドレイン領域(20)との間に挿入されたチャネル領域(16)上に形成される。ゲート構造(14)は、ゲート誘電体24上にゲート電極(22)と、ゲート(22)の面に沿った側壁26を有する。ソース領域(18)は、n型の低濃度ドープ領域(32)と、n+領域34とを有するが、ソースhalo領域は有しない。ドレイン領域(20)は、n型の低濃度ドープ領域42と、n+領域44と、p型ドレインhalo領域(50)とを有する。ドレインhalo領域(50)は、ドレイン領域にイオンを斜めに注入することにより形成された、ドープ領域である。

(もっと読む)

半導体装置

【課題】高耐圧化と低オン抵抗化を図ることができる半導体装置を提供する。

【解決手段】半導体基板1上に形成されたpウエル領域であるP−well35と、このP−well35の表面層に形成されるpオフセット領域であるP−off5と、P−off5の表面からP−well35に達するように形成したトレンチ19と、このトレンチ19の側壁にゲート酸化膜20を介して形成したゲート電極21と、トレンチ底に形成した拡張ドレイン領域である拡張ドレイン領域であるN−body6と、このN−body6と接するようにトレンチ19内部上方に向かって形成されたドレイン領域となるnエピタキシャル層30と、Pwell35の表面層に形成したソース領域となる上部のn+ 領域8とで構成する。この構成では、タングステン層23を形成する箇所にドレイン領域となるnエピタキシャル層30を形成するために、トレンチ19を広げることなく、ゲート電極21とドレイン領域となるnエピタキシャル層30の間隔を広げることができるために、高耐圧化と、低オン抵抗化を図ることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】pMISFET及びnMISFETにおけるキャリアのモビリティーの向上を図ること。

【解決手段】nMISFETとpMISFETとからなるCMISFETを具備する半導体装置であって、nMISFETは、第1のゲート電極14bと、この第1のゲート電極の側面に形成された圧縮応力を有する第1のスペーサ15を具備し、pMISFETは、第2のゲート電極14aと、この第2のゲート電極の側面に形成された圧縮応力が第1のスペーサ15より小さい第2のスペーサ16とを具備してなる。

(もっと読む)

半導体装置及びその製造方法

【課題】 MIS構造のトランジスタの微細化と、ドレイン出力アナログ信号のソースへのリークの低減とを両立できるようにした半導体装置及びその製造方法を提供する。

【解決手段】 MOSトランジスタ100を微細化しても寄生抵抗増大の副作用を伴わせないようにするために、LDD構造のソース60及びドレイン70を非対称構造にする。つまり、N−−層73の不純物濃度は、Esatの低減を目的に低くしておく。また、N−層63の不純物濃度は、寄生抵抗低減を目的にN−−層73よりも高くする。さらに、シリコン基板1のソース60側だけにポケットインプラを行って、P−層80を形成する。これにより、アナログCMOSとしては短チャネルに部類される0.35[μm]ゲート長トランジスタにおいて、ドレイン電圧誘起Vth低下現象(DIBL)と、ピンチオフ点でのチャネル変調効果(CLM)とを同時に低減可能である。

(もっと読む)

半導体装置の製造方法

【課題】 不純物のプロファイルを精度よく制御することが可能な半導体装置の製造方法を提供する。

【解決手段】 半導体領域1に不純物元素のイオンを注入する工程と、半導体領域に、所定元素としてIV族の元素又は不純物元素と同一導電型であって不純物元素よりも質量数が大きい元素のイオンを注入してアモルファス状態の結晶欠陥領域5を形成する工程と、不純物元素及び所定元素が注入された領域にフラッシュランプの光を照射してアニールを行い、アモルファス状態の結晶欠陥領域の結晶欠陥を回復させるとともに不純物元素を活性化する工程と、を備え、フラッシュランプの光を照射してアニールを行う工程を、結晶欠陥領域のアモルファス状態が維持される温度で半導体領域を予め加熱した状態で行う。

(もっと読む)

選択的堆積プロセスを使用したMOSFETデバイスの作製方法

本発明の実施形態により、高ドーパント濃度を含有するエピタキシャルシリコンゲルマニウム材料を選択的に堆積するなど、シリコン含有材料を堆積するためのプロセスが提供される。一実施例において、1つの層を別の層の上部に堆積するために、少なくとも2つの異なるプロセスガスに基板が曝される。1つのプロセスガスは、ジクロロシラン、ゲルマニウム源、およびエッチャントを含有し、次のプロセスガスは、シランおよびエッチャントを含有する。他の実施例において、プロセスガスが、ジクロロシラン、メチルシラン、および塩化水素、またはシラン、メチルシラン、および塩化水素を含有する。一態様において、堆積された層が、結晶格子内に格子間部位を有し、格子間部位内に約3at%以下の炭素を含有し、引き続き、結晶格子の置換部位内に炭素を包含するようにアニーリングされる。別の態様において、シリコンゲルマニウム積層体が、約25at%以下、約25at%以上、および約5at%以下のゲルマニウム濃度を含有する第1、第2、および第3の層を有する。 (もっと読む)

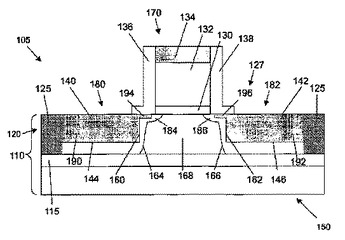

半導体装置及び半導体装置の製造方法

本発明は、半導体装置(105)及びこの装置の製造方法に関する。本発明の好ましい実施例は、シリコン半導体基板(110)、酸化膜層(115)及び活性層(120)を含む半導体装置(105)である。活性層では、絶縁領域(125)及び活性領域(127)が形成された。活性領域(127)は、ソース(180)、ドレイン(182)及び基体(168)を含む。ソース(180)及びドレイン(182)は、ソースエクステンション(184)及びドレインエクステンション(186)も含む。活性層(120)はゲート(170)を有する。ゲート(170)の両側にL字型側壁スペーサが位置する。ソース(180)及びドレイン(182)は、シリサイド領域(190、192)も含む。これらの領域の特徴は、側壁(136、138)の下に位置されたエクステンション(194、196)を有することである。これらのエクステンション(194、196)は、半導体装置(105)の性能を著しく改善するように、ソース(194)及びドレイン(196)の直列抵抗を大きく低減する。  (もっと読む)

(もっと読む)

MIS型電界効果トランジスタ

下地SiGe層1上に歪みSi層2をエピタキシャル成長させ、ゲート絶縁膜3aとゲート電極4aを形成した後、ゲート電極4aをマスクにして、下地SiGe層1及び歪みSi層2に不純物をイオン注入し(図2(a))、活性化のための熱処理を行ってソース・ドレイン領域6を形成する(図2(b)、(c))。このとき、歪みSi層2の膜厚は、最終的なMISFETのソース・ドレイン領域6の不純物濃度が最大となる深さをTp(=Rp)としたとき、2Tp以下にする。 (もっと読む)

固相エピタキシャル再成長を用いてドーピングプロファイルの深さを低減した半導体基板及び同半導体基板の生産方法

半導体デバイスの生産方法であって、a)半導体基板を準備し、b)半導体基板の最上面上に絶縁層を設け、c)適当な注入によって、前記半導体基板の最上層中にアモルファス層を作り、d)所定のドーピングプロファイルを伴う前記アモルファス層を作るための前記絶縁層を通して、前記半導体基板中へドーパントを、前記ドーピングプロファイルが前記絶縁層内に位置するピーク値を持つように注入し、e)前記アモルファス層を再成長させ、前記ドーパントを活性化する固相エピタキシャル再成長作用を適用することを含む半導体デバイスの生産方法。  (もっと読む)

(もっと読む)

固相エピタキシャル再成長を用いて接合の漏損を低減させた半導体基板及び同半導体基板の生産方法

半導体デバイスの生産方法であって、(a)半導体基板を準備し、(b)適当な注入によって、第1の深さを有する第1のアモルファス層を前記半導体基板の最上層に作成し、(c)第1のドーピングプロファイルを伴う前記第1のアモルファス層を設けるために前記半導体基板の中に第1のドーパントを注入し、(d)前記第1のアモルファス層を部分的に再成長させ、前記第1の深さより小さい第2の深さを有する第2のアモルファス層を形成し、前記第1のドーパントを活性化する第1の固相エピタキシャル再成長作用を適用し、(e)前記第1のドーピングプロファイルより高いドーピング濃度を伴う第2のドーピングプロファイルを伴う前記第2のアモルファス層を設けるために前記半導体基板の中に第2のドーパントを注入し、(f)前記第2のアモルファス層を再成長させ、前記第2のドーパントを活性化するために、第2の固相エピタキシャル再成長作用を適用することを含む半導体デバイスの生産方法。  (もっと読む)

(もっと読む)

等方性エッチングプロセスを使ったショットキーバリアMOSFET製造方法

【課題】電流の流れを調整するトランジスタデバイスの組立て方法において、更なる駆動電流を可能にし、デバイスの動作を最適化するプロセスを提供すること。

【解決手段】本発明の一実施形態における方法は、チャンネル領域に対するショットキーバリア接合位置のより良い制御を与えるために、メタルソースドレイン接触の形成に先行して等方性エッチングプロセスを利用する。このショットキーバリア10接合の配置の制御性からの改善により、更なる駆動電流を可能にし、デバイスの動作を最適化する。

(もっと読む)

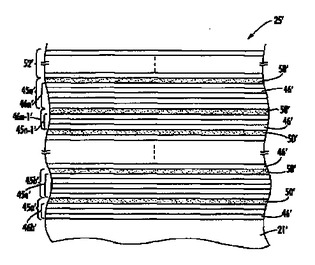

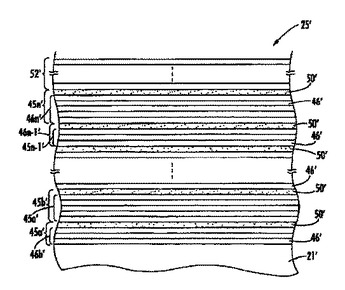

バンド設計超格子を有する半導体装置

半導体装置は、複数の積層された層群を有する超格子を有する。また装置は、電荷キャリアが積層された層群と平行な方向に超格子を通って輸送される領域を有する。超格子の各層群は、基本半導体部分を定形する複数の積層された基本半導体分子層と、該基本半導体部分上のエネルギーバンド調整層と、を有する。さらにエネルギーバンド調整層は、少なくとも一つの非半導体分子層を有し、この層は、連接する基本半導体部分の結晶格子内に閉じ込められる。従って超格子は、平行な方向において、エネルギーバンド調整層がない場合に比べて大きな電荷キャリア移動度を有する。

(もっと読む)

(もっと読む)

バンド設計超格子を有するMOSFETを有する半導体装置

半導体装置は、基板と、該基板に隣接する少なくとも一つのMOSFETとを有する。MOSFETは、超格子チャンネルを有し、該超格子チャンネルは、複数の積層された層群を有する。またMOSFETは、超格子チャンネルと水平方向に隣接するソースおよびドレイン領域と、超格子上に設置されたゲートと、を有し、超格子チャンネルを通って、積層された層群と平行な方向に電荷キャリアの輸送が生じる。超格子チャンネルの各層群は、基本半導体部分を定形する複数の積層された基本半導体分子層と、該基本半導体部分上のエネルギーバンド調整層と、を有する。エネルギーバンド調整層は、基本半導体部分に隣接する結晶格子内に取り込まれた、少なくとも一つの非半導体分子層を有し、超格子チャンネルは、平行な方向において、エネルギーバンド調整層がない場合に比べて大きな電荷キャリア移動度を有する。

(もっと読む)

(もっと読む)

バンド設計超格子を有する半導体装置

半導体装置は、複数の積層された層群を有する超格子を有する。超格子の各層群は、基本半導体部分を定形する複数の積層された基本半導体分子層と、該基本半導体部分上のエネルギーバンド調整層と、を有する。さらにエネルギーバンド調整層は、少なくとも一つの非半導体分子層を有し、この層は、連接する基本半導体部分の結晶格子内に閉じ込められる。従って超格子は、平行な方向において、エネルギーバンド調整層がない場合に比べて大きな電荷キャリア移動度を有する。  (もっと読む)

(もっと読む)

221 - 240 / 240

[ Back to top ]