Fターム[5F140BK20]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン領域、電極及びSD近傍領域の製造 (13,929) | ソース・ドレイン領域形成後の処理 (2,202) | 熱処理 (1,739)

Fターム[5F140BK20]の下位に属するFターム

活性化 (1,499)

Fターム[5F140BK20]に分類される特許

21 - 40 / 240

半導体装置の製造方法

【課題】ソース/ドレイン領域と基板との間の容量の低下を防止でき、パンチスルー現象を低減することができる半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、半導体基板上に第1絶縁膜を介してゲート電極を形成する工程と、前記ゲート電極の上面及び側面を覆う第2絶縁膜を形成する工程と、前記第2絶縁膜をマスクとして前記半導体基板の表面に溝部を形成する工程と、前記溝部の底面上に、該溝部の側壁の上部の露出を残す厚さで第3絶縁膜を形成する工程と、前記露出された溝部の側壁の上部を起点としたエピタキシャル成長により、前記第3絶縁膜上に前記半導体のエピタキシャル層を形成する工程と、前記エピタキシャル層に不純物を導入してソース/ドレイン領域を形成する工程と、を有することを特徴とする

(もっと読む)

半導体装置及びその製造方法

【課題】貼り合わせSOI基板を使用せずに、容易なプロセスにより、高速なMIS電界効果トランジスタを提供する。

【解決手段】p型のSi基板1上に、一部に空孔4を有するシリコン酸化膜2が設けられ、空孔4を挟んでシリコン酸化膜2上に延在したp型のSOIC基板(Si)5が設けられ、シリコン窒化膜3により素子分離されている。空孔4に自己整合して、SOIC基板5上にゲート酸化膜10を介してゲート電極11が設けられ、ゲート電極11の側壁にサイドウォール12が設けられ、SOIC基板5には、ゲート電極11に自己整合してn型ソースドレイン領域(7、8)及びサイドウォール12に自己整合してn型ソースドレイン領域(6、9)が設けられ、n型ソースドレイン領域には、バリアメタル15を有する導電プラグ16を介してバリアメタル18を有するCu配線19が接続されている構造からなるNチャネルのMIS電界効果トランジスタ。

(もっと読む)

MISFET及びその製造方法

【課題】 LDD領域の長さを精度良く調整可能で、高周波動作に適用できる非対称な横方向二重拡散型MISFETを提供する。

【解決手段】 第1導電型のウェル1の上方にゲート絶縁膜3を介してゲート電極5を形成する工程、ウェル1に第2導電型の不純物イオン注入によりドレイン領域7を形成する工程、ウェル1の上方にゲート電極5が形成されるゲート電極領域とドレイン領域7を少なくとも覆い、ゲート電極領域とドレイン領域の間が開口したマスクパターン層を形成する工程、マスクパターン層をマスクとして自己整合的に、マスクパターン層で覆われていない領域に第2導電型の不純物イオン注入によりドレイン領域より低濃度のLDD拡散領域6を形成する工程、及び、ウェル1のゲート電極5を挟んでドレイン領域7の反対側の領域に第2導電型の不純物イオン注入によりLDD拡散領域より高濃度のソース領域を形成する工程を有する。

(もっと読む)

半導体集積回路装置の製造方法

【課題】低抵抗で、かつ接合リーク電流の少ないCoシリサイド層を形成することのできるサリサイドプロセスを提供する。

【解決手段】Co純度が99.99%以上で、FeおよびNiの含有量が10ppm以下、より好ましくはCo純度が99.999%の高純度Coターゲットを用いたスパッタリング法によってウエハの主面上に堆積したCo膜をシリサイド化することにより、MOSFETのゲート電極(8n、8p)、ソース、ドレイン(p+型半導体領域13、n+型半導体領域14)の表面に低抵抗で接合リーク電流の少ないCoSi2層(16b)を形成する。

(もっと読む)

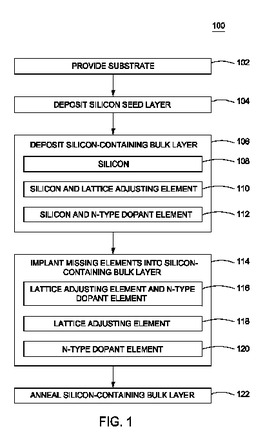

NMOSエピ層の形成方法

制御されたチャネル歪みおよび接合抵抗を有するNMOSトランジスタ、およびその製造方法が、本明細書で提供される。いくつかの実施形態において、NMOSトランジスタを形成するための方法は、(a)p型シリコン区域を有する基板を準備すること、(b)p型シリコン区域の上にシリコンシード層を堆積すること、(c)シリコン、シリコンおよび格子調整元素またはシリコンおよびn型ドーパントを備えるシリコン含有バルク層をシリコンシード層の上に堆積すること、(d)(c)で堆積されたシリコン含有バルク層に欠けている格子調整元素またはn型ドーパントのうちの少なくとも1つをシリコン含有バルク層の中に注入すること、(e)(d)の注入の後、シリコン含有バルク層をエネルギービームを用いてアニールすることを含むことができる。いくつかの実施形態において、基板は、その中に画定されたソース/ドレイン区域を有する、部分的に製造されたNMOSトランジスタデバイスを備えることができる。  (もっと読む)

(もっと読む)

量子井戸型半導体装置

量子井戸型半導体装置、および量子井戸型半導体装置を形成する方法について示した。本方法は、基板の上部に配置され、量子井戸チャネル領域を有するヘテロ構造を提供するステップを有する。また、この方法は、ソースおよびドレイン材料領域を形成するステップを有する。また、この方法は、ソースおよびドレイン材料領域に溝を形成するステップを有し、ドレイン領域から分離されたソース領域が提供される。また、この方法は、溝内のソース領域とドレイン領域の間に、ゲート誘電体層を形成するステップと、溝内のゲート誘電体層の上部に、ゲート電極を形成するステップとを有する。  (もっと読む)

(もっと読む)

半導体デバイス及びその製造方法

【課題】従来よりも界面準位密度を低減させることができる半導体デバイス及びその製造方法を提供する。

【解決手段】窒素ガス雰囲気下で低ダメージなECRプラズマを用いたECRプラズマ処理を行うことにより、III−V族化合物半導体層2の表面を窒化処理したことで、当該III−V族化合物半導体層2にIn−N結合及びGa−N結合を形成しAs酸化物を抑制して界面特性を向上させることができ、かくして従来よりも界面準位密度が低減されたMOSFET1を提供できる。また、アニール処理することにより、窒化処理層5においてGa−N結合が支配的となった界面結合状態を形成し、界面準位密度を一段と低減させることができる。

(もっと読む)

半導体装置、半導体集積回路装置及び半導体装置の製造方法

【課題】高耐圧且つ低オン抵抗な半導体装置及びこれを含む半導体集積回路装置を歩留まり良く、安価に提供する。

【解決手段】第1導電型の半導体基板(1)と、前記第1導電型と反対の第2導電型であって前記半導体基板の表面側に形成されたソース領域(11)、低濃度ドレイン領域(12)及び高濃度ドレイン領域(13)と、前記半導体基板上に形成されたゲート絶縁膜(14)と、前記ゲート絶縁膜上に形成されたゲート電極と、を備える半導体装置(10)であって、

前記ゲート電極は、前記低濃度ドレイン領域の少なくとも一部を覆うように形成され、且つ、前記低濃度ドレイン領域の上方において開孔(16)を有することを特徴とする半導体装置。前記低濃度ドレイン領域と高濃度ドレイン領域とは互いに隣接することが好ましい。

(もっと読む)

自己整合損傷層を有するデバイス構造体の形成方法

【解決課題】 自己整合損傷層を有するデバイス構造体の形成方法を提供すること。

【解決手段】デバイス構造体は、基板の半導体材料内部に画定された第1導電型の第1及び第2ドープ領域を有する。逆の導電型の第3ドープ領域が、横方向に第1ドープ領域を第2ドープ領域から分離する。ゲート構造部が基板の上表面に配置され、第3ドープ領域と垂直方向で重なる関係を有する。第1結晶損傷層は基板の半導体材料の内部に画定される。第1結晶損傷層は、基板の半導体材料によって取り囲まれた第1の複数のボイドを有する。第1ドープ領域は、第1結晶損傷層と基板の上表面との垂直方向の間に配置される。第1結晶損傷層は横方向に第3ドープ領域内には延びない。

(もっと読む)

イオン注入及び側方拡散による炭化シリコンパワーデバイスの自己整列的な製造方法

【課題】自己整列した浅い注入領域及び深い注入領域を形成し、浅い注入領域の低い拡散率を有するn型ドーパントを比較的固定すると共に、深い注入領域の高い拡散率を有するp型ドーパントを十分に拡散させ、良く制御されたチャネルを形成するpベース領域をn型ソースの周りに形成して横型炭化シリコンパワーデバイスを製造する。

【解決手段】炭化シリコン基板内にマスクの開口部を通してp型ドーパントをイオン注入して深いp型注入領域を形成する。マスクの同じ開口部を通してn型ドーパントをイオン注入して前記p型注入領域と比較して浅いn型注入領域を形成する。その後、前記深いp型注入領域を前記浅いn型注入領域を囲む炭化シリコン表面まで、該埋め込まれた深いp型注入領域を該浅いn型注入領域を通って炭化シリコン基板表面まで縦方向に拡散させることなく、側方拡散させるのに十分な温度及び時間でアニールする。

(もっと読む)

半導体素子

LDMOS(横方向拡散金属酸化物半導体)構造は、ソースを基板及びゲートシールドへと接続させ、この際、このような接点のためにより小さな面積が用いられる。前記構造は、導電性基板層と、ソースと、ドレイン接点とを含む。少なくとも1つの介在層により、前記ドレイン接点が前記基板層から分離される。導電性のトレンチ状のフィードスルー要素が前記介在層を通過し、前記基板及び前記ソースと接触することで、前記ドレイン接点及び前記基板層を電気的に接続する。 (もっと読む)

III族窒化物系電界効果トランジスタおよびその製造方法

【課題】オン抵抗が低いIII族窒化物系電界効果トランジスタおよびその製造方法を提供する。

【解決手段】本発明のIII族窒化物系電界効果トランジスタは、下地半導体層上に第1窒化物半導体層および第2窒化物半導体層が順次積層された窒化物半導体積層体と、窒化物半導体積層体の上面に接する、ソース電極およびドレイン電極と、ソース電極およびドレイン電極の間の窒化物半導体積層体における、第1窒化物半導体層の一部および第2窒化物半導体層が形成されていない領域であるリセス領域と、リセス領域上に形成された窒化物半導体膜と、リセス領域の内壁面、および第2窒化物半導体層の上面に形成された絶縁膜と、絶縁膜上に形成されたゲート電極とを有し、第2窒化物半導体層は、第1窒化物半導体層に比べて広い禁制帯幅を有し、窒化物半導体膜の上面は、第1窒化物半導体層の上面よりも低いことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】 所望の極浅拡散層を形成することが可能な半導体製造方法を提供する。

【解決手段】

シリコン基板1にイオン注入するイオン注入工程と、イオン注入工程の後に、シリコン

基板1にマイクロ波を照射するマイクロ波照射工程と、マイクロ波照射工程の後に、シリ

コン基板1を熱処理装置に移し、シリコン基板に0.1ミリ以上100m秒以下のパルス

幅の光を照射することにより、シリコン基板1を熱処理する熱処理工程と、を備える。

(もっと読む)

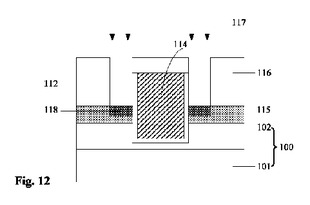

半導体装置及びその製造方法

【課題】ナローチャネル特性の劣化を抑制する。

【解決手段】素子分離領域STIは、半導体基板100に形成されたトレンチ104内に設けられており、トレンチ104の側壁上に形成された下地絶縁膜105を有している。素子形成領域100a上にはゲート絶縁膜112が形成されており、ゲート絶縁膜112は高誘電率膜110を有している。高誘電率膜110の第1の部分110aは、素子形成領域100aにおける上面上に形成されており、高誘電率膜110の第2の部分110bは、素子形成領域における上部側面104a上に下地絶縁膜105を介して形成されている。第2の部分110bと下地絶縁膜105との間には、MISトランジスタの閾値電圧を変更する金属を含有する第1のキャップ膜106が設けられている。

(もっと読む)

半導体装置およびその製造方法

【課題】ホットキャリアの発生を大幅に抑制して、トランジスタの長期信頼性を高める。

【解決手段】基板102の一面のチャネル領域108において、ゲート幅方向に断続的に深さが変化するように形成されたトレンチ162内部を埋め込むように形成されたゲート電極122を含むトランジスタにおいて、ソース領域112およびドレイン領域113の下方には、それぞれ第1のオフセット領域106および第2のオフセット領域107が形成される。ここで、第2のオフセット領域107は、ゲート長方向の断面において第2のオフセット領域107とチャネル領域108とのPN境界線のトレンチ162底部の角部を始点としたソース領域112に向けた横方向の距離をx、トレンチ162底部の角部を始点とした下方向の距離をyとして、合計距離x+yが0.1μm以上である。

(もっと読む)

半導体装置とその製造方法

【課題】SiGe層を用いてPチャネル型トランジスタのチャネル形成領域に圧縮応力を印加すると共に、リーク電流を低減する。

【解決手段】半導体装置120は、半導体基板100の表面部に形成されたソース領域及びドレイン領域122と、これらに挟まれたチャネル形成領域上にゲート絶縁膜101を介して形成されたゲート電極102とを含むPチャネル型トランジスタを備える。ゲート電極102の両側それぞれにおいて半導体基板100にリセスが形成され、リセスに、SiGeからなる第1エピタキシャル層111と、その上に形成され且つSiからなる第2エピタキシャル層112と、その上に形成され且つSiGeからなり、チャネル形成領域を挟む第3エピタキシャル層113とを備える。ソース領域及びドレイン領域122は、第3エピタキシャル層113中に形成され、且つ、それぞれの接合深さがいずれも第3エピタキシャル層133の深さよりも浅い。

(もっと読む)

トレンチDMOSトランジスタの製造方法

トレンチDMOSトランジスタの製造方法であって、半導体基板上に酸化物層及びバリア層を形成するステップと、トレンチを形成するために、酸化物層及び半導体基板をエッチングするステップと、トレンチの内壁にゲート酸化物層を形成するステップと、バリア層上にポリシリコン層を形成し、トレンチを充填するステップと、トレンチゲートを形成するために、ポリシリコン層をエッチバックするステップと、バリア層及び酸化物層を除去するステップと、拡散層を形成するために、トレンチゲートの両側の半導体基板内にイオンを注入するステップと、拡散層上をフォトレジスト層で覆い、ソース/ドレイン配置を定義するステップと、拡散層内にイオンを注入するステップと、トレンチゲートの両側に側壁を形成するステップと、拡散層及びトレンチゲート上に金属シリサイド層を形成するステップとを含む。低コスト及び改善された製造効率を伴う効果的な結果が達成される。  (もっと読む)

(もっと読む)

半導体装置を製作する方法

【課題】例えば大きな電荷キャリア移動度を有する半導体装置を製作する方法を提供する。

【解決手段】複数の積層された層群を有する超格子を形成するステップによって、半導体装置を製作する方法である。また当該方法は、前記超格子を通って、前記積層された層群と平行な方向に、電荷キャリアの輸送が生じる領域を形成するステップを有する。超格子の各層群は、基本半導体部分を定形する複数の積層された基本半導体分子層と、該基本半導体部分上のエネルギーバンド調整層と、を有する。前記エネルギーバンド調整層は、基本半導体部分に隣接する結晶格子内に取りこまれた、少なくとも一つの非半導体分子層を有し、前記超格子は、超格子が存在しない場合に比べて、前記平行な方向において大きな電荷キャリア移動度を有する。また前記超格子は、共通のエネルギーバンド構造を有しても良い。

(もっと読む)

バンド設計超格子を有する半導体装置

【課題】例えば大きな電荷キャリア移動度を有する半導体装置を提供する。

【解決手段】半導体装置は、複数の積層された層群を有する超格子を有する。また装置は、電荷キャリアが積層された層群と平行な方向に超格子を通って輸送される領域を有する。超格子の各層群は、基本半導体部分を定形する複数の積層された基本半導体分子層と、該基本半導体部分上のエネルギーバンド調整層と、を有する。さらにエネルギーバンド調整層は、少なくとも一つの非半導体分子層を有し、この層は、連接する基本半導体部分の結晶格子内に閉じ込められる。従って超格子は、平行な方向において、エネルギーバンド調整層がない場合に比べて大きな電荷キャリア移動度を有する。

(もっと読む)

最適化された低温ハロー注入又はポケット注入

ポケット注入又はハロー注入を実行するための改良された方法が開示される。ハロー注入によって生成されるダメージ及び欠陥の量は、リーク電流を増大させ、ノイズマージンを減少させ、また、最小ゲート電圧を増加させることによって、半導体デバイスの性能を低下させる。ハロー注入又はポケット注入を低温で実行すると、結晶構造に生じるダメージが減少し、結晶のアモルファス化が改善される。低温を使用することにより、ホウ素又はリン等、より軽い元素をハロー注入に使用することができる。 (もっと読む)

21 - 40 / 240

[ Back to top ]