Fターム[5F140BK20]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン領域、電極及びSD近傍領域の製造 (13,929) | ソース・ドレイン領域形成後の処理 (2,202) | 熱処理 (1,739)

Fターム[5F140BK20]の下位に属するFターム

活性化 (1,499)

Fターム[5F140BK20]に分類される特許

41 - 60 / 240

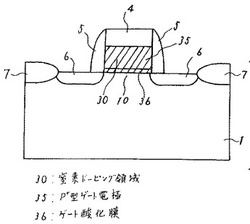

半導体装置及びその製造方法

【課題】ゲート電極中に含まれる不純物の拡散を防止することができ、さらに、ゲート絶縁膜の信頼性及びホットキャリア耐性を向上させることができる半導体装置及びその製造方法を得る。

【解決手段】N型シリコン基板1上にゲート酸化膜36およびP+型ゲート電極35を形成する。P+型ゲート電極35の両側にソース/ドレイン領域6を形成する。ゲート酸化膜36およびP+型ゲート電極35中には窒素がドープされ、窒素ドーピング領域30が形成される。

(もっと読む)

半導体装置の製造方法

【課題】比較的低い温度のもとで、良質で、かつ、薄いシリコン酸化膜等を均一に形成することができる半導体装置の製造方法を提供する。

【解決手段】ステップ1では、半導体基板がモノシラン(SiH4)に暴露される。次に、ステップ2では、残存するモノシラン(SiH4)が排気される。そして、ステップ3では、半導体基板が亜酸化窒素プラズマに晒される。ステップ1〜3を1サイクルとして、必要とされる膜厚が得られるまでこのサイクルを繰り返すことで、所望のシリコン酸化膜が形成される。

(もっと読む)

半導体素子およびその製造方法

【課題】半導体素子の低オン抵抗化を実現し、全体の製造工程数を低減する半導体素子およびその製造方法を提供すること。

【解決手段】ソース・ドレイン領域を形成する際のイオン注入時に、低耐圧横型トレンチMOSFETでは、ドレイン形成用の開口部がトレンチ側壁から離れ、ソース形成用の開口部がトレンチ側壁に達し、トレンチ横型パワーMOSFETでは、ソース形成用の開口部がトレンチ側壁から離れ、ドレイン形成用の開口部がトレンチ側壁に達するパターンのマスクを用いる。このマスクを用いて、高ドーズ量および低加速電圧で行うイオン注入と、低ドーズ量および高加速電圧で行うイオン注入を連続して行うことによって、低耐圧横型トレンチMOSFETのLDD領域と、トレンチ横型パワーMOSFETのLDD領域とを同時に形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】簡易な手順で、高誘電率ゲート絶縁膜とメタルゲート電極とのゲートスタック構造を有する相補型トランジスタの閾値を調整する。

【解決手段】相補型トランジスタの第1導電型のトランジスタ(162)の閾値電圧を変化させる第1の調整用金属を第1導電型のトランジスタ(162)および第2導電型のトランジスタ(160)に同時に添加し、第2導電型のトランジスタ(160)のメタルゲート電極(110a)上から第1の調整用金属の拡散を抑制する拡散抑制元素を添加する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】突出部の側面が凹凸状とされ、前記側面を覆うようにゲート酸化膜を形成したときに、実効的なチャネル長が増加して、ピラー型MOSトランジスタの電流駆動能力が低下するという課題があった。

【解決手段】基板と、前記基板の一面から垂直方向に突出された突出部7とを備え、突出部7の先端側の上部拡散層と、基端側の下部拡散層と、側面7cを覆うゲート絶縁膜14と、ゲート絶縁膜14を覆うゲート電極15と、を有し、チャネルが前記垂直方向となるピラー型MOSトランジスタ51を具備し、突出部7が平面視八角形状であり、突出部7の側面7cが{100}面からなる4つの主表面8a、8b、8c、8dと、{110}面および{111}面からなり、前記主表面8a、8b、8c、8dよりも面積が小さい4つの副表面9a、9b、9c、9dとからなる半導体装置101を用いることにより、上記課題を解決できる。

(もっと読む)

半導体装置及びその製造方法

【課題】内部回路の誤動作を誘発させない保護回路を有する半導体装置を提供する。

【解決手段】P型Si基板101と、ESD保護素子1Aと、被保護素子1Bとを備えた半導体装置1であって、ESD保護素子1Aは、ソースN型拡散領域107Aと、P型Si基板101内においてソースN型拡散領域107Aを覆い、ソースN型拡散領域107Aの下方から少なくともゲート電極106Aの下方の一部まで形成され、P型Si基板101の基本領域よりもP型不純物濃度が高い高濃度P型拡散領域103とを備え、被保護素子1Bは、ドレインN型拡散領域108Bと、P型Si基板101内においてドレインN型拡散領域108Bと接する低濃度P型拡散領域104とを備え、ESD保護素子1Aのドレイン電極112Aと被保護素子1Bのドレイン電極112Bとが接続され、高濃度P型拡散領域103は、低濃度P型拡散領域104よりもP型不純物濃度が高い。

(もっと読む)

非平面な基板表面を有する基板を処理する方法

非平面的な表面を有する基板を共形的に処理する技術を開示する。この技術は、複数の段階を備える。第1段階では、基板の幾つかの面が効果的に処理される。第2段階では、これらの面が更に処理されるのを防ぐ又は制限するべく処理が行われる。第3段階では、基板のその他の面が処理される。ある適用例では、第1段階及び第2段階において、粒子の流れに垂直又は実質的に垂直な面が処理され、その他の面は、第3段階において処理される。ある実施形態では、第2段階は、基板への膜の堆積工程を含む。 (もっと読む)

半導体装置の製造方法、及び光電変換装置の製造方法

【課題】重金属汚染物質による半導体装置又は光電変換装置の特性の悪化を抑制する。

【解決手段】半導体装置の製造方法は、半導体基板における第1の側の面に第1のゲッタリング層を形成する第1の工程と、前記第1の工程の後に、酸化雰囲気中で前記半導体基板を加熱することにより、前記半導体基板における前記第1の側と反対側の第2の側の面に酸化膜を形成する第2の工程と、前記第2の工程の後に、前記第1のゲッタリング層の少なくとも一部を除去する第3の工程と、前記第3の工程の後に、前記半導体基板の前記第2の側にポリシリコン層を形成するとともに前記半導体基板の前記第1の側に第2のゲッタリング層をポリシリコンで形成する第4の工程と、前記ポリシリコン層をパターニングすることにより、MOSトランジスタのゲート酸化膜及びゲート電極を形成する第5の工程とを備えている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】GIDL電流が発生することを抑制する。

【解決手段】第2導電型高濃度不純物層170は、素子形成領域110に形成されており、ソース及びドレインとして機能する。第2導電型低濃度不純物層160は、第2導電型高濃度不純物層170それぞれの周囲に設けられている。第2導電型低濃度不純物層160は、第2導電型高濃度不純物層170を深さ方向及びチャネル長方向に拡張し、第2導電型高濃度不純物層170より不純物濃度が低濃度である。第2導電型低濃度不純物層160は、少なくとも一部がゲート電極140及びゲート絶縁膜180の下に位置している。そしてゲート絶縁膜180は、第2導電型低濃度不純物層160上に位置する部分に傾斜部182を有している。傾斜部182は、ゲート電極140の中央部側から側面に向かうにつれて、変局点がないように膜厚が連続的に厚くなっている。

(もっと読む)

半導体装置

【課題】SiGeのチャネルを有する半導体装置の高性能化及び高信頼化をはかる。

【解決手段】シリコンを主成分とする半導体基板101の一主面に設けられ、素子分離絶縁膜102によって区画された素子形成領域103と、チャネル領域となるSi及びGeを主成分とし素子形成領域103上に設けられた半導体膜104と、半導体膜104上にゲート絶縁膜105を介して設けられたゲート電極106と、チャネル領域を挟んで半導体膜104及び基板101に形成されS/D領域110と、ゲート電極106の両側面に設けられた側壁絶縁膜109と、S/D領域110上の側壁絶縁膜109で区画されたS/Dコンタクト領域上に半導体膜104と金属との反応により形成され、且つS/Dコンタクト領域以外の半導体膜104よりも薄い膜厚に形成された金属化合物膜111とを備えた。

(もっと読む)

半導体装置およびその製造方法

【課題】大きな歪み量を発生可能な半導体装置およびその製造方法を提供する。

【解決手段】半導体装置の製造方法は、CとCの濃度の10倍以上のGeとを含んだSiGeC層を形成する工程(S3)と、SiGeC層内のCのうちで格子置換位置に位置しているものを格子間位置へと移動させることによって、前記SiGeC層内の全てのCに対する格子置換位置に位置するCの割合を形成された時点での割合から低下させて50%以下に低下させる工程(S4)と、を含む。

(もっと読む)

非対称的チャンネルゾーン及び異なる構成としたソース/ドレイン延長部を有する非対称的電界効果トランジスタの構成及び製造

【課題】 非対称的絶縁ゲート電界効果トランジスタ(100又は102)は半導体ボディのボディ物質(180又は182)のチャンネルゾーン(244又は284)によって横方向に分離されたソース(240又は280)及びドレイン(242又は282)を有している。

【解決手段】 ゲート電極(262又は302)が該チャンネルゾーンの上方でゲート誘電体層(260又は300)の上側に位置している。該ボディ物質の一層高度にドープしたポケット部分(250又は290)がほぼ該ソースのみに沿って延在している。該ソースは、主要ソース部分(240M又は280M)と、一層軽度にドープした横方向ソース延長部(240E又は280E)とを有している。該ドレインは、主要ドレイン部分(242M又は282M)と、一層軽度にドープした横方向ドレイン延長部(242E又は282E)とを有している。該ドレイン延長部は該ソース延長部よりも一層軽度にドープされている。これら2つの延長部を画定する半導体ドーパントの最大濃度は、該ソース延長部におけるよりも該ドレイン延長部において一層深くに発生する。付加的に又は代替的に、該ドレイン延長部は該ソース延長部よりも該ゲート電極下側を更に横方向に延在する。これらの特徴はスレッシュホールド電圧が動作時間に関して高度に安定であることを可能とする。

(もっと読む)

ソース/ドレインゾーンに沿って調節したポケット部分を具備する非対称的電界効果トランジスタを有する半導体構成体の構成及び製造

【課題】 半導体ボディの上部表面に沿って設けられている非対称的絶縁ゲート電界効果トランジスタ(100U又は102U)は、該トランジスタボディ物質のチャンネルゾーン(244又は284)によって横方向に分離された第1及び第2ソース/ドレインゾーン(240及び242又は280及び282)を包含している。

【解決手段】 ゲート電極(262又は302)がチャンネルゾーン上方でゲート誘電体層(260又は300)の上側に位置している。該ボディ物質の横方向に隣接した物質よりも一層高度にドープした該ボディ物質のポケット部分(250又は290)が該S/Dゾーンの内のほぼ第1のもののみに沿って該チャンネルゾーン内に延在している。該ポケット部分の垂直ドーパント分布は、互いに離隔されている夫々の位置(PH−1乃至PH−3)において複数個の局所的最大(316−1乃至316−3)に到達すべく調節されている。該調節は、典型的に、該ポケット部分の垂直方向ドーパント分布が上部半導体表面近くで比較的平坦であるように実施される。その結果、該トランジスタのリーク電流は減少されている。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】高集積であり且つビット線を埋め込む必要のない3次元トランジスタを有する半導体記憶装置を提供する。

【解決手段】ゲートトレンチを介して両側に位置する第1及び第2の拡散層とゲートトレンチの底面に形成された第3の拡散層とを有する活性領域と、第1及び第2の拡散層にそれぞれ接続された第1及び第2の記憶素子と、第3の拡散層に接続されたビット線と、ゲート絶縁膜を介してゲートトレンチの第1の側面を覆い、第1の拡散層と第3の拡散層との間にチャネルを形成する第1のゲート電極と、ゲート絶縁膜を介してゲートトレンチの第2の側面を覆い、第2の拡散層と第3の拡散層との間にチャネルを形成する第2のゲート電極とを備える。本発明によれば、ゲートトレンチの両側面にそれぞれ別のトランジスタが形成されることから、従来の2倍の集積度が得られる。

(もっと読む)

延長型ドレイン電界効果トランジスタを有する半導体構成体の構成及び製造

【課題】 拡張型ドレイン絶縁ゲート電界効果トランジスタ(104又は106)が、第1ウエル領域(184A又は186A)の一部によって構成されているチャンネル(322又は362)ゾーンによって横方向に分離されている第1及び第2ソース/ドレインゾーン(324及び184B又は364及び186B/136B)を包含している。

【解決手段】 ゲート誘電体層(344又は384)が該チャンネルゾーンの上側に存在している。該第1ソース/ドレインゾーンは、通常は、ソースである。通常はドレインである該第2S/Dゾーンは、少なくとも部分的には第2ウエル領域(184B又は186B)で構成されている。該半導体ボディのウエル分離部分(136A又は212U/136B)が該ウエル領域の間を延在しており且つ各ウエル領域よりも一層軽度にドープされている。該ウエル領域の構成は、該半導体ボディのIGFETの部分における最大電界をして上部半導体表面の十分に下側、典型的には該ウエル領域同士が互いに最も近い箇所におけるか又はその近くで発生させる。該IGFETの動作特性は動作時間と共に安定である。

(もっと読む)

歪誘起合金及び段階的なドーパントプロファイルを含むその場で形成されるドレイン及びソース領域

【解決手段】

トランジスタのドーパントプロファイルは、その場で(in situ)ドープされた歪誘起半導体合金に基いて得ることができ、段階的なドーパント濃度が高さ方向に沿って確立され得る。その結果、半導体合金をチャネル領域にごく近接して位置させることができ、それにより全体的な歪誘起効果を高めることができる一方で、最終的に得られるドーパントプロファイルについて過度に妥協しなくてよい。更に、半導体合金を選択的に成長させるのに先立ち追加的な注入種が組み込まれてよく、それにより内部歪の注入誘起緩和を回避することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】3Dピラー型SGTを複数並列に接続する際に、配線層を設ける必要のない半導体装置を提供する。

【解決手段】3Dピラー型SGTの上部主電極領域が選択エピタキシャル成長半導体層を含み、少なくとも2つの隣接する3Dピラー型SGTを、各々の選択エピタキシャル成長半導体層を接触させて並列接続する。

(もっと読む)

MISトランジスタ

【課題】ゲート電極とソース/ドレイン電極間で電気的短絡を起こし難いMISトランジスタを得る。

【解決手段】サイドウォール15を二重構造とする。バッファ層13は窒化酸化シリコンで形成され、バッファ層13の上に窒化シリコン層14が形成される。このサイドウォール15をマスクとしてシリサイド膜10を形成する。バッファ層13は窒化酸化シリコンのみならず、酸化シリコンで形成されてもよい。シリサイド膜はコバルトシリサイドでも、ニッケルシリサイドでもよい。窒化シリコン層14はバッファ層13よりも大きい応力を持つ。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の結晶欠陥発生を抑制することができる半導体装置の製造方法を提供する。

【解決手段】ウエハ上にSTI用のトレンチを形成し、そのトレンチに絶縁膜を埋め込む。次に、ウエハ表面に酸素を導入する。酸素導入は、酸素100%雰囲気下で、1100℃、60秒間、ウエハ表面にRTO(Rapid Thermal Oxidation)を行う。その後、高温アニールを行う。SRAM製造プロセスにおいて、転位が発生するおそれのある高温アニール工程とソース/ドレイン部のイオン注入工程の前に酸素導入を行うため、ウエハの結晶強度を高めることができ、アニール工程やイオン注入工程によって発生する転位を抑えることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】炭素含有シリコン領域を有するn型MISトランジスタを備えた半導体装置において、チャネル領域のゲート長方向に印加される引っ張り応力の大きさを、効果的に増大させる。

【解決手段】少なくともn型MISトランジスタNTrを有する半導体装置において、n型MISトランジスタnTrは、半導体基板10における第1の半導体領域10a上に形成された第1のゲート絶縁膜13aと、第1のゲート絶縁膜13a上に形成された第1のゲート電極14aと、第1のゲート電極14aの側面上に形成された第1のサイドウォール18Aと、第1のサイドウォール18Aの外側方に形成された炭素含有シリコン領域27とを備え、炭素含有シリコン領域27の上面高さは、第1の半導体領域10aにおける第1のゲート絶縁膜13aの下に位置する領域の上面高さよりも高い。

(もっと読む)

41 - 60 / 240

[ Back to top ]