Fターム[5F140BK20]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン領域、電極及びSD近傍領域の製造 (13,929) | ソース・ドレイン領域形成後の処理 (2,202) | 熱処理 (1,739)

Fターム[5F140BK20]の下位に属するFターム

活性化 (1,499)

Fターム[5F140BK20]に分類される特許

61 - 80 / 240

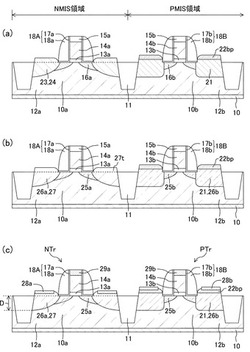

半導体装置及びその製造方法

【課題】炭素含有シリコン領域を有するn型MISトランジスタを備えた半導体装置において、チャネル領域のゲート長方向に印加される引っ張り応力の大きさを、効果的に増大させる。

【解決手段】少なくともn型MISトランジスタNTrを有する半導体装置において、n型MISトランジスタnTrは、半導体基板10における第1の半導体領域10a上に形成された第1のゲート絶縁膜13aと、第1のゲート絶縁膜13a上に形成された第1のゲート電極14aと、第1のゲート電極14aの側面上に形成された第1のサイドウォール18Aと、第1のサイドウォール18Aの外側方に形成された炭素含有シリコン領域27とを備え、炭素含有シリコン領域27の上面高さは、第1の半導体領域10aにおける第1のゲート絶縁膜13aの下に位置する領域の上面高さよりも高い。

(もっと読む)

可動ゲート型電界効果トランジスタの製造方法

【課題】ダメージを生じさせることなく、安価かつ短時間に犠牲層を除去する犠牲層プロセスを採用し、量産性を向上させる可動ゲート型電界効果トランジスタの製造方法を提供する。

【解決手段】第1犠牲層15と、第2犠牲層16と、を有する複合犠牲層の上に可動ゲートが形成される可動ゲート形成工程と、第2犠牲層16がエッチング除去される第2犠牲層除去工程と、第1犠牲層15がエッチング除去される第1犠牲層除去工程と、を備える可動ゲート型電界効果トランジスタの製造方法とした。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】耐圧確保とターンオフタイム短縮の両立が可能なIGBT構造を有する半導体装置を提供する。

【解決手段】縦型IGBT構造とPMOSFET30とが半導体基体上に一体で形成されている半導体装置10を構成する。この半導体装置は、PMOSFET30のドレイン電極29と、IGBTのコレクタ11とが電気的に接続されている。また、PMOSFET30のソース領域(第2のベース領域14)とドリフト領域12とにまたがって形成されたドリフト領域の取り出し領域(NSD19)が、PMOSFET30のソース領域の取り出し領域(PSD20)と導電膜により接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート絶縁膜を薄膜化しつつ、リーク電流を低減する。

【解決手段】半導体装置の製造方法は、半導体基板上にNMOSトランジスタのゲート電極13を形成する工程と、ゲート電極の側面に側壁絶縁膜17を形成する工程と、ゲート電極の両側の半導体基板内に不純物を導入する工程と、ゲート電極、側壁絶縁膜及び半導体基板上にアニールの前後でストレス値に差が生じる絶縁膜20を形成する工程と、ゲート電極、側壁絶縁膜及び半導体基板を絶縁膜で覆った状態でアニールにより不純物を拡散させ、ソース/ドレイン拡散層18を形成する工程とを具備する。

(もっと読む)

半導体装置の製造方法

【課題】オフリーク電流の発生を抑制する。

【解決手段】半導体装置の製造方法は、半導体基板11上にNMOSトランジスタのゲート電極13を形成する工程と、ゲート電極の側面に側壁絶縁膜17を形成する工程と、ゲート電極の両側の半導体基板内に第1の不純物を注入する工程と、ゲート電極の両側の半導体基板内に第2の不純物を注入し、半導体基板を非晶質化させる工程と、ゲート電極、側壁絶縁膜及び半導体基板を覆い、アニールの前後でストレス値に差が生じる絶縁膜を形成する工程と、アニールにより半導体基板内に第1の不純物を拡散させ、ソース/ドレイン拡散層18を形成する工程とを具備する。

(もっと読む)

チャネル領域への減少させられたオフセットを有する埋め込みSi/Ge材質を伴うトランジスタ

【解決手段】

非長方形形状を有していてよいキャビティに基いて歪誘起半導体合金を形成することができ、二酸化シリコン材質のような適切な保護層を設けることによって、非長方形形状は対応する高温処理の間にも維持され得る。その結果、歪誘起半導体材質の横方向のオフセットを小さくすることができる一方、キャビティエッチングプロセスの間に対応するオフセットスペーサの十分な厚みをもたらすことができるので、ゲート電極完全性を維持することができる。例えば、pチャネルトランジスタは六角形形状を伴うシリコン/ゲルマニウム合金を有することができ、それにより全体的な歪転移効率を顕著に高めることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】極浅接合の深さが精密制御された半導体装置およびその製造方法を提供する。

【解決手段】主面が第1面方位である第1導電型の第1半導体層11と、第1半導体層11上に直接接合され、主面が第1面方位と異なる第2面方位である第1導電型の第2半導体層12と、第2半導体層12に連接して第1半導体層11上に形成され、主面が第1面方位である第3半導体層13a、13bと、第2半導体層12上にゲート絶縁膜を介して形成されたゲート電極15と、ゲート電極15をゲート長方向に挟むように第2半導体層12に形成され、第1半導体層11と第2半導体層12との接合面16に至る第2導電型の第1不純物拡散領域17a、17bと、第1不純物拡散領域17a、17bをゲート長方向に挟むように第3半導体層13a、13bから第1半導体層11の上部にかけて形成された第2導電型の第2不純物拡散領域18a、18bと、を具備する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】金属微粒子と半導体基板の反応を利用して電極を形成する、高性能な半導体装置の製造方法およびグレイン粒径の小さい電極を有する高性能な半導体装置を提供する。

【解決手段】直径20nm以下の金属微粒子を溶媒中に分散した溶液を、半導体基板上に塗布する工程と、溶媒を蒸発させる工程と、金属微粒子と半導体基板を反応させ、半導体基板表面に金属半導体化合物薄膜を形成する工程とを有することを特徴とする半導体装置の製造方法。半導体基板上に金属半導体化合物薄膜を有する半導体装置であって、金属半導体化合物薄膜は膜厚方向に単グレインで形成され、単グレインの粒径が40nm以下であることを特徴とする半導体装置。

(もっと読む)

出力制御用半導体装置

【課題】 チップサイズを縮小することができ、低コスト化が可能となるスイッチングトランジスタ、及びそれを用いた出力制御装置を提供する。

【解決手段】 第一導電型の半導体基板1の主面上に、第二導電型の高濃度埋め込み層2を有し、エピタキシャル層3の表面に形成される第二導電型のドレイン領域9と第二導電型の高濃度埋め込み層2が第二導電型の柱状の高濃度拡散領域11を介して電気的に接続していることにより、ドレイン端子10が基板表面上にある縦型トランジスタを用いる。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】ソース・ドレインの寄生抵抗の低減及び短チャネル効果の抑制と共にリーク電流の低減をはかる。

【解決手段】チャネル領域を構成する第1の半導体領域12と、第1の半導体領域12上にゲート絶縁膜15を介して形成されたゲート電極16と、第1の半導体領域12をチャネル長方向から挟んで形成された金属シリサイドからなるソース・ドレイン電極14と、を具備してなる電界効果トランジスタであって、ソース・ドレイン電極14は、チャネル領域の平均的な不純物濃度よりも高い不純物濃度を有し、且つチャネル領域との界面又は界面近傍に前記不純物濃度のピークを持ち、チャネル領域は、ソース・ドレイン電極との界面又は界面近傍に前記不純物濃度のピークを持つ。

(もっと読む)

半導体装置と、電子部品及び半導体装置の製造方法

【課題】オン電流の低下を抑制しつつ、閾値電圧を高くすることを可能とした半導体装置と、電子部品及び半導体装置の製造方法を提供する。

【解決手段】半導体基板1に形成されたHVトランジスタ10を備え、HVトランジスタ10は、半導体基板1上に絶縁膜を介して形成されたゲート電極19と、ソース15及びドレイン13を有し、ゲート電極19の内部は、当該ゲート電極19に電圧が印加されてソース15とドレイン13との間に電流が流れるときに空乏化する。このような構成であれば、空乏化によりゲート電極19に容量が生じ、この容量はゲート絶縁膜の容量と直列に接続される。これにより、ゲート絶縁膜の容量が実質的に低下するため、HVトランジスタ10の閾値電圧を高くすることができる。

(もっと読む)

絶縁ゲート型半導体装置およびその製造方法

【課題】 絶縁ゲート型半導体素子が形成されるウェル領域は拡散領域であり、その底部ほど不純物濃度が薄くなり、抵抗が増加する問題がある。このため特に、アップドレイン構造の絶縁ゲート型半導体素子ではオン抵抗が増加する問題があった。

【解決手段】 p型ウェル領域を、2つのp型不純物領域を積層することにより構成する。それぞれのp型不純物領域は、p型不純物を、異なる注入エネルギーでn型半導体層内部と表面に多段注入し、熱処理により同時に拡散してp型ウェル領域とする。これにより、表面からある程度の深さ(5μm程度)までの不純物プロファイルが略平坦なp型ウェル領域を得ることができ、その表面に形成されるチャネル層の特性変動も抑制できる。

(もっと読む)

自己整合損傷層を有するデバイス構造体及びそのデバイス構造体の形成方法

【課題】 自己整合損傷層を有するデバイス構造体及びそのデバイス構造体の形成方法を提供する。

【解決手段】 デバイス構造体は、基板の半導体材料内部に画定された第1導電型の第1及び第2ドープ領域を有する。逆の導電型の第3ドープ領域が、横方向に第1ドープ領域を第2ドープ領域から分離する。ゲート構造部が基板の上表面に配置され、第3ドープ領域と垂直方向で重なる関係を有する。第1結晶損傷層は基板の半導体材料の内部に画定される。第1結晶損傷層は、基板の半導体材料によって取り囲まれた第1の複数のボイドを有する。第1ドープ領域は、第1結晶損傷層と基板の上表面との垂直方向の間に配置される。第1結晶損傷層は横方向に第3ドープ領域内には延びない。

(もっと読む)

ホウ素閉じ込めを強化した埋め込みSi/Ge材質を有するトランジスタ

【解決手段】

シリコン/ゲルマニウム合金(255)を備えたPチャネルトランジスタのPN接合の近傍に拡散阻害種(256A)を組み込むことによって、拡散関連のPM接合の不均一性を低減することができ、それによりデバイス安定性を高め且つ総合的なトランジスタ性能を高めることに寄与する。拡散阻害種(256A)は炭素、窒素等の形態で提供されてよい。

(もっと読む)

トランジスタ

【課題】トラッピングを少なくするためにAlGaN層を薄くし、またゲート漏洩を減少させるために層を追加して最大駆動電流を増加させるようにする。

【解決手段】高比抵抗半導体層20と、この高比抵抗半導体層20上に設けられたバリア半導体層18と、このバリア半導体層18に接触するするとともに、バリア半導体層18の表面部を被覆していないソースおよびドレインコンタクト13,14と、バリア半導体層18の被覆されていない表面上に設けられた絶縁層24と、この絶縁層24上に設けられ、ゲート漏洩のバリアを形成するゲートコンタクト16とを備えている。

(もっと読む)

半導体装置およびその製造方法

【課題】MISトランジスタを有する半導体装置の性能を向上させる。

【解決手段】シリコン基板1の主面上に半導体層を積み上げて形成された一対のソース・ドレイン領域sdn,sdpと、その側壁を覆う側壁絶縁膜ISと、側壁絶縁膜ISに平面的に挟まれた位置のシリコン基板1の主面上に、ゲート絶縁膜IGを隔てて配置されたゲート電極GEと、ゲート電極GEの側方下部からソース・ドレイン領域sdn,sdpの側方下部に渡って形成されたエクステンション領域exn,expとを有する半導体装置であって、ソース・ドレイン領域sdn,sdpの側壁は順テーパ状の傾斜を有しており、側壁絶縁膜ISの側壁のうち、ゲート絶縁膜IGおよびゲート電極GEと隣り合う方の側壁は、順テーパ状の傾斜を有している。

(もっと読む)

パワー半導体装置およびパワー半導体装置の製造方法

【課題】ドレイン領域とドリフト領域との境界近傍における電界集中を緩和することにより、パワー半導体装置のドレイン耐圧を改善する。

【解決手段】パワー半導体装置10は、チャネル領域を含むボディ領域70と、チャネル領域の上にゲート絶縁膜50を介して形成されたゲート電極60と、ボディ領域に取り囲まれた領域に形成されたN型のソース領域130と、ゲート電極60から離間して形成されたドレイン領域140とを備える。ドレイン領域140の周りは、ドレイン領域より不純物濃度が低い拡散領域100により取り囲まれている。また拡散領域100とゲート電極60の下方領域との間に拡散領域100より不純物濃度が低いドリフト領域80が形成されている。

(もっと読む)

半導体装置およびその製造方法、ならびにその半導体装置を用いた集積半導体装置および不揮発性半導体記憶装置

【課題】絶縁ゲート型電界効果トランジスタにおいて低電圧下で急峻なスイッチング特性を有する半導体素子を提供する。

【解決手段】大規模集積回路に用いられているプレーナ型のロジック回路用MOSFETにおいて、ドレイン拡散層電極のなかに、ダイオード素子と抵抗素子が並列配置されるように形成することで、低電圧であってもゲート電圧変化に対してドレイン電流が急峻な変化を示す高性能トランジスタが実現できる。

(もっと読む)

半導体装置

【課題】同一基板上に複数のトランジスタを備え、各トランジスタの動作特性を劣化させることなく、各々に適切な閾値電圧を設定することのできる半導体装置を提供する。

【解決手段】本発明の一態様に係る半導体装置は、素子分離領域2により分離された第1および第2のトランジスタ領域10、20を有する半導体基板1と、第1および第2のトランジスタ領域10、20において、半導体基板上1に形成された不純物拡散抑制層12、22と、不純物拡散抑制層12、22上に形成されたエピタキシャル結晶層13、23と、を有し、不純物拡散抑制層22の厚さは、不純物拡散抑制層12の厚さよりも厚く、チャネル領域11に含まれる導電型不純物は、エピタキシャル結晶層13中の領域における濃度が、半導体基板1中の領域における濃度よりも低く、チャネル領域21に含まれる導電型不純物は、エピタキシャル結晶層23中の領域における濃度が、半導体基板1中の領域における濃度よりも低い。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】ゲート絶縁膜の信頼性および半導体装置の性能を確保可能である半導体装置の製造方法および半導体装置を提供する。

【解決手段】本発明にかかる半導体装置の製造方法は、Si基板100上にゲート絶縁膜103を形成するゲート絶縁膜形成工程と、ゲート絶縁膜103上に第1の金属膜を形成する第1の金属膜形成工程と、第1の金属膜上に金属電極104を構成する第2の金属膜を形成する第2の金属膜形成工程と、熱処理を行なってゲート絶縁膜103と第1の金属膜との間にゲート絶縁膜103と第1の金属膜との反応膜118を形成する反応膜形成工程とを行なって、第1の金属膜形成工程時のゲート絶縁膜103の損傷を回復させている。

(もっと読む)

61 - 80 / 240

[ Back to top ]