Fターム[5F140BK20]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン領域、電極及びSD近傍領域の製造 (13,929) | ソース・ドレイン領域形成後の処理 (2,202) | 熱処理 (1,739)

Fターム[5F140BK20]の下位に属するFターム

活性化 (1,499)

Fターム[5F140BK20]に分類される特許

101 - 120 / 240

半導体装置およびその製造方法

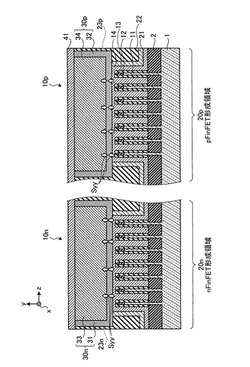

【課題】FinFETにおいて、従来のFinFETの構造に比してさらにチャネルに応力を印加することができる半導体装置を提供すること。

【解決手段】Si基板1と、フィン11、フィン11の延在方向に平行な面上にゲート絶縁膜13を介して形成される所定の幅のゲート電極14、およびフィン11の延在方向に平行な面上のゲート電極14の両側に形成されるソース/ドレイン領域を含むFinFET10n,10pと、を備え、ゲート電極14上に形成され、応力印加層31,32の形成温度と室温での線膨張係数の差が、フィン11の形成温度と室温での線膨張係数の差と異なる導電性材料によって形成される応力印加層31,32と、応力印加層31,32上に形成され、フィン11よりもヤング率の大きい導電性材料からなるプラグ層33,34と、を備える。

(もっと読む)

半導体装置、およびその製造方法

【課題】応力膜によるチャネル領域への歪み効果を向上させる形状の半導体基板を有し、かつ十分な深さのソース・ドレイン領域を有する半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置の製造方法は、半導体基板と、半導体基板上にゲート絶縁膜を介してゲート電極を形成する工程と、前記半導体基板の前記ゲート電極の両側の前記ゲート電極から離間した領域に凹部を形成する工程と、前記凹部の底面および側面からほぼ同じ深さまで前記半導体基板に導電型不純物を注入する工程と、前記凹部の底面および側面上に、前記半導体基板内の前記ゲート電極下のチャネル領域に歪みを与えて前記チャネル領域における電荷移動度を向上させる応力膜を形成する工程と、を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】駆動能力を向上させた半導体装置を提供する。

【解決手段】半導体装置には、ゲート幅方向に断続的に深さの変化する凹部を設けるためのトレンチ部3が形成されており、ゲート絶縁膜6を介して、トレンチ部3の内部及び上面部にゲート電極7が形成されている。ゲート電極7のゲート長方向の一方の側にはソース領域9が形成されており、他方の側にはドレイン領域10が形成されている。ソース領域9とドレイン領域10の少なくとも一部では、ゲート電極7の形成前にトレンチ部3の内壁からイオン注入を用いて不純物添加をおこなった後、拡散および活性化の熱処理を施すことによって、トレンチ部3の表面から底部にかけて深く形成させることを可能とする。これにより、ゲート電極7の凹部上面に集中して流れていた電流がトレンチ部3の全体に一様に流れるようになり、ゲート幅方向に深さが変化するように形成された凹部の実効的なゲート幅が広がる。このため、半導体装置のオン抵抗が低下し、駆動能力が高まる。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】炭化珪素半導体装置に於いて、MIS界面特性を劣化させないゲート絶縁膜のPDA手法(熱処理方法)を提供する。

【解決手段】炭化珪素半導体基板2上に、熱酸化法により、0.5nm〜2nmの範囲内の厚みを有する酸化珪素5を形成する。更に、酸化珪素5の上に堆積法によって酸化膜6を形成して、ゲート絶縁膜としての積層酸化膜7を得る。その上で、酸化膜6の堆積温度よりも高温で、且つ、酸素濃度が0.05Pa以上で5Pa以下の範囲内に制御された減圧の酸素雰囲気下で、積層酸化膜7に対して熱処理を行うことで、ゲート絶縁膜を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル領域を挟むソース/ドレイン領域にeSiGe層などを埋め込んだ構造において、接合リークの低減をはかる。

【解決手段】ソース/ドレイン領域に半導体エピタキシャル層を埋め込んだ半導体装置であって、半導体基板100の主表面に形成され、素子分離領域102で囲まれた素子形成領域上にゲート絶縁膜103を介して形成されたゲート電極104と、ゲート電極104下のチャネル領域を挟むソース/ドレイン領域に形成され、基板100とは異なる材料からなる第1の半導体膜111,113でそれよりもシリサイド化反応の高い第2の半導体膜112を挟んだ3層構造を有する半導体エピタキシャル層110と、ゲート電極104及びエピタキシャル110層上に形成され、且つ基板100とエピタキシャル層110との界面に沿って半導体膜112に延伸して形成されたシリサイド層126とを備えた。

(もっと読む)

半導体装置およびその製造方法

【課題】 駆動能力を向上させた半導体装置を提供する。

【解決手段】 当該半導体装置には、ゲート幅方向に深さの変化する凹部を設けるためのトレンチ部8が形成されており、ゲート絶縁膜9を介して、トレンチ部8の内部及び上面部にゲート電極10が形成されている。ゲート電極10のゲート長方向の一方の側にはソース領域12が形成されており、他方の側にはドレイン領域13が形成されている。ソース領域12とドレイン領域13の少なくとも一部の表面は、ゲート電極10近傍にLOCOS法を用いて形成した厚膜酸化膜の除去することで他よりも低く形成する。このように、ソース領域12とドレイン領域13の一部の表面を他よりも低くすることにより、ゲート電極10の当該凹部上面に集中して流れていた電流がトレンチ部8の全体に一様に流れるようになり、ゲート幅方向に深さが変化するように形成された凹部の実効的なゲート幅が広がる。このため、半導体装置のオン抵抗が低下し、駆動能力が高まる。

(もっと読む)

半導体素子およびその製造方法

【課題】MOSトランジスタに十分な応力(ストレス)が加える半導体素子およびその製造方法を提供する。

【解決手段】半導体素子は、半導体基板100と、半導体基板100上に備えられたゲート電極114およびゲート電極114の側壁面に備えられたスペーサ116を含むゲート構造物110と、ゲート構造物110の両側の半導体基板100内に形成されたソース/ドレーン領域102と、ゲート構造物110上エッチング停止膜130と、を含み、エッチング停止膜130は、スペーサ116上の第1領域130_1およびゲート電極の上面上の第2領域130_2を含み、第1領域130_1の厚さは、第2領域130_2の厚さの85%以下である。

(もっと読む)

ビーム照射装置、及び、ビーム照射方法

【課題】 高品質の加工を行う。

【解決手段】 第1の波長、及び第1の波長とは異なる第2の波長のレーザビームを出射するレーザ光源と、第1面及び第1面と反対側の第2面を有する加工対象物を保持するステージと、第1の波長のレーザビームを、ステージに保持された加工対象物の第1面に入射させる第1の光学系と、第2の波長のレーザビームを、ステージに保持された加工対象物の第2面に入射させる第2の光学系と、第1の波長のレーザビームが、ステージに保持された加工対象物の第1面に入射した後に、第2の波長のレーザビームが、第2面に入射するように、レーザ光源によるレーザビームの出射を制御する制御装置とを有するビーム照射装置を提供する。

(もっと読む)

半導体素子の製造方法

【課題】本発明は、素子性能を向上させて工程を単純化させることができる半導体素子の製造方法を提供できる。

【解決手段】本発明による半導体素子の製造方法は、半導体基板にウェルを形成する段階と、半導体基板にゲートオキサイドを形成する段階と、ゲートオキサイドの上にゲートを形成する段階と、ゲート下部にポケット(pocket)を形成する段階と、半導体基板に対して第1スパイクアニール(spike anneal)を行なう段階と、半導体基板に深いソース/ドレインインプラント工程を行なう段階及び半導体基板に対して第2スパイクアニールを行なう段階と、を含む方法とする。

(もっと読む)

ドレインおよびソース領域にリセスを形成することによってトランジスタの接合容量の低減

スペーサ構造に基づいてドレイン及びソース領域の一部にリセスを形成することにより、深いドレインおよびソース領域を形成するためのその後の注入プロセスによって、SOIトランジスタの埋め込み絶縁層までドーパント濃度を適度に高くすることができる。さらに、スペーサ構造は、実質量の歪み半導体合金をその本来の厚みで保持し、従って、効率的な歪み誘起機構が設けられる。高度なアニール技術により、過度の側方拡散が回避され、よって各々のスペーサの横幅が縮小される。これにより、トランジスタデバイスの長さが縮小される。従って、低減された接合容量との組み合わせにおいて、縮小した横寸法に基づいて電荷キャリア移動度を高めることができる。  (もっと読む)

(もっと読む)

トランジスタのゲート電極のプレアモルファス化のブロッキング

トランジスタのソース/ドレイン領域を選択的にプレアモルファス化する一方で、トランジスタのゲート電極はプレアモルファス化しない技術が提供される。例示的実施形態においては、ゲート電極にわたってプレアモルファス化注入ブロッキング材料が形成される。更に例示的実施形態においては、各種ストレッサを用いてチャネル領域に歪みが誘発される。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】対称フラットバンド電圧、同一ゲート電極材料かつ高誘電率誘電体層を有するCMISFETを提供する。

【解決手段】nMISFETは、半導体基板10の表面上に配置された第1ゲート絶縁膜16と、第1ゲート絶縁膜16上に配置されたM1xM2yO(M1=Y,La,Ce,Pr,Nd,Sm,Gd,Tb,Dy,Ho,Er,Tm,YbまたはLu,M2=Hf,Zr,Ta,x/(x+y)>0.12)で表される組成比を有する第1金属酸化物層20と、第2金属酸化物層24と、第2金属酸化物層24上に配置された第1導電層28とを備え、pMISFETは、半導体基板10表面上に配置された第2ゲート絶縁膜18と、第2ゲート絶縁膜18上に配置されたM3zM4wO(M3=Al,M4=Hf,Zr,Ta,z/(z+w)>0.14)で表される組成比を有する第3金属酸化物層22と、第4金属酸化物層26と、第4金属酸化物層26上に配置された第2導電層30とを備える半導体装置およびその製法。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】イオン注入される不純物濃度以上に不純物濃度を増大させた高濃度不純物層を有し、この高濃度不純物装置とシリサイド電極とにおける接触電気抵抗を低減したソース・ドレインを有するCMOS電界効果トランジスタ及びその製造方法を提供する。

【解決手段】n型MOS電界効果トランジスタ10とp型MOS電界効果トランジスタ20とを備え、そのソース・ドレイン13、14で、シリサイド電極132、142の下に、急峻な濃度勾配を有する2層の高濃度不純物層133、134、143、144を有するCMOS電界効果トランジスタ1を提供する。

(もっと読む)

MOSFETアレイにおけるレイアウト依存の閾値電圧変動の迅速な推定方法

集積回路レイアウトにおいて、レイアウトによって誘起される閾値電圧の変動を自動的に推定する方法。前記方法は、解析のために前記レイアウト内の拡散領域を選択する工程で始まる。続いて、システムが、選択された領域のSi/STIエッジと、チャネル領域と、前記チャネル領域に結合するゲート/Siエッジを特定する。次に、特定されたチャネル領域夫々における閾値電圧の変動を特定する。この工程には、縦方向の効果による閾値電圧変動を計算する工程と、横方向の効果による閾値電圧変動を計算する工程と、縦方向と横方向の変動を組み合わせて全体の変動を計算する工程が必要である。最後に、個々のチャネルにおける変動を組み合わせることにより変動の合計が決定される。  (もっと読む)

(もっと読む)

高耐圧IC

【課題】安価に製造できる高耐圧接合終端構造による絶縁分離構造を用いる場合においても、dV/dt耐量が高く、高電位島内の寄生素子構造のラッチアップによる誤動作を防止することができる高耐圧半導体装置の提供。

【解決手段】高電位ゲート駆動回路部と、レベルシフト回路部とを同一の他導電型半導体基板1上に備え、前記ゲート駆動回路部には少なくとも一つの横型MOSFETが形成され、前記半導体基板の主面に平行方向に選択的に、かつ前記横型MOSFETのソース領域5およびドレイン領域7の下方に、寄生素子抑制用の埋め込み絶縁膜3を有する高耐圧ICとする。

(もっと読む)

処理装置、トランジスタ製造方法

【課題】SiC中のSi欠損を発生させずにSiC基板の不純物層をアニールする技術を提供する。

【解決手段】本発明の処理装置10は、搬送室11と、高温熱処理室12と、前処理装置13を有している。処理対象物70は前処理装置13内の加熱装置22により加熱され、SiC基板71表面に形成された有機膜74は焼成され、SiC基板71表面には炭素皮膜76が形成される。炭素皮膜76が形成されたSiC基板71は高温熱処理装置12のアニール室40内において高温に加熱され、アニールされる。SiC基板71表面には炭素皮膜76が配置されているから、SiC基板71からのSiの欠損が生じない状態で不純物層をアニールすることが可能である。

(もっと読む)

半導体装置

【課題】ポリシリコン/メタル積層電極構造のポリシリコン/メタル界面における界面抵抗を低減し、動作速度の低下を防止する。

【解決手段】半導体基板100と、領域N1にチャネル領域102を挟むように形成された拡散層103と、ゲート絶縁膜104と、金属膜105a、105b及びn型ポリシリコン膜105cを含むゲート電極105と、を有するnチャネルMISFETと、領域P1にチャネル領域202を挟むように形成されボロンをドーパントして含む拡散層203と、ゲート絶縁膜204と、金属膜205a〜c及び窒素を含む金属膜205cとの界面部におけるボロン濃度が5E19cm−3以下であるn型ポリシリコン膜205dを含むゲート電極205と、を有するpチャネルMISFETと、を備える。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】従来の耐圧80V用のトレンチ横型パワーMOSFETよりも簡素なプロセス工程で製造でき、かつ従来の80Vよりも低い耐圧用の横型パワーMOSFETよりもデバイスピッチが小さくて単位面積当たりのオン抵抗が小さいこと。

【解決手段】基板50に浅く幅の狭いトレンチ51を小さいピッチで形成し、トレンチ51の周囲にドリフト領域となるn拡散領域60を形成する。トレンチ51の内側には厚さが0.05μmの均一な厚さのゲート酸化膜59を形成し、その内側にゲートポリシリコン52を形成する。基板50の表面領域にベース領域62およびソース領域となるn+拡散領域61を形成すると共にトレンチ51の底部にドレイン領域となるn+拡散領域58を形成する。ゲートポリシリコン52の内側に層間絶縁膜65を設け、その内側をドレイン領域に電気的に接続するポリシリコン63で埋める。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化プロセスにおいても、また、Nchトランジスタ及びPchトランジスタの両方を持つデバイスにおいても、欠陥等を発生させることなく、トランジスタのチャネル領域に対する応力制御を行うことを可能にする。

【解決手段】Nchトランジスタの第1のゲート電極107及びPchトランジスタの第2のゲート電極108のそれぞれの構成材料として、互いに応力の大きさが異なる材料を用いている。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体基板の素子形成面に大きな段差が生じる場合でも、段差部底面の所望の部位に不純物を導入し得る半導体装置およびその製造方法を提供する。

【解決手段】同一極性の2つのMOS トランジスタがそれぞれのソース・ドレイン領域の各一方の不純物拡散層を共有するとともに2つのMOS トランジスタの各ポリシリコンゲート同士が隣り合う部分を有する半導体装置において、2つのMOS トランジスタの各ポリシリコンゲート11の高さが150nm 以上、隣り合うポリシリコンゲート相互の間隔が87nm 以下であって、2つのMOS トランジスタで共有される不純物拡散層151は、拡散層表面部の不純物濃度が拡散層内部で最も高い。

(もっと読む)

101 - 120 / 240

[ Back to top ]